基础006_pg109_IP-Xfft

作者:桂。

时间:2018-05-09 07:20:48

链接:http://www.cnblogs.com/xingshansi/p/9012232.html

前言

简要记录xilinx FFT的IP核使用。参考:pg109-xfft.pdf

一、综述

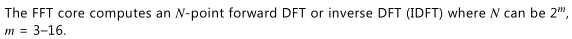

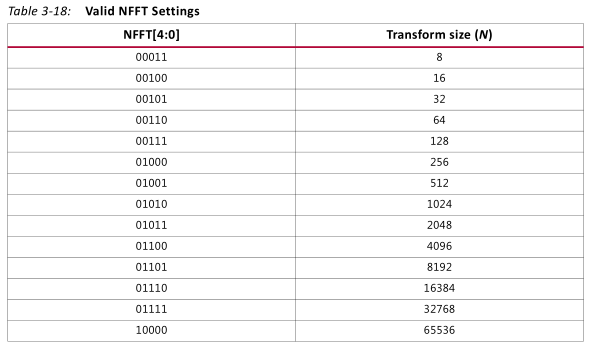

支持FFT点数(8~65536):

精度:

三种工作模式:

- 浮点(Full-precision unscaled arithmetic):动态最大,电路最复杂

- 定点(Scaled fixed-point):动态最小,电路最简单,默认scaled. 其中scaling 因此由s_axis_config_tdata配置(具体设置见:二、管脚描述)。

- 块浮点(Block floating-point):介于定点与浮点之间,是一种折中思路,例如对于16bit定点数17, 17 = 0.5313*25,取小数位7bit,指数为4bit,

0.5313 -> 7bit, 5 -> 4bit, 这样11bit便近似表示了16bit的特性。因此块浮点通常也可用于数据压缩传输技术。

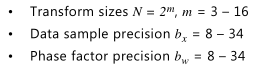

根据表达式特性,FFT结构均可实现IFFT:

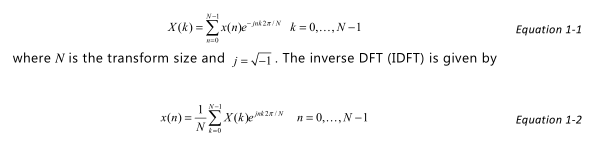

内部实现结构为基2、基4、混合基(前级基4+最后一层为基2):

对于Burst I/O结构,采用DIT(decimation-in-time)思路; 对于pipelined streaming I/O结构,采用DIF(decimation-in-frequency)思路。这一点可根据Xilinx 常用模块汇总(verilog)【02】一文的结构图来理解,流水的自然相邻的一起处理,Burst则无此限制。

二、管脚描述

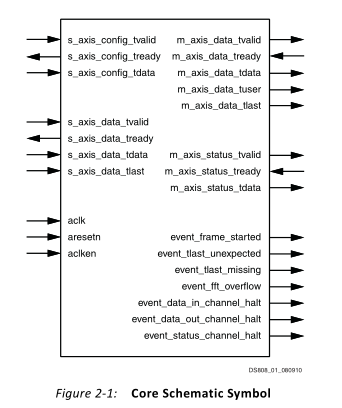

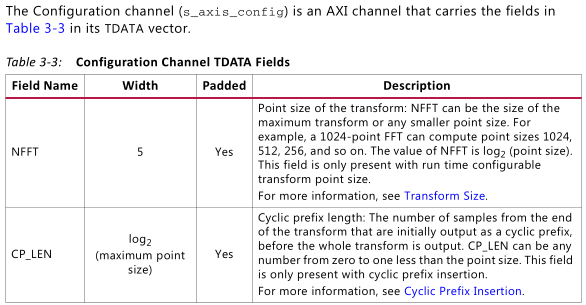

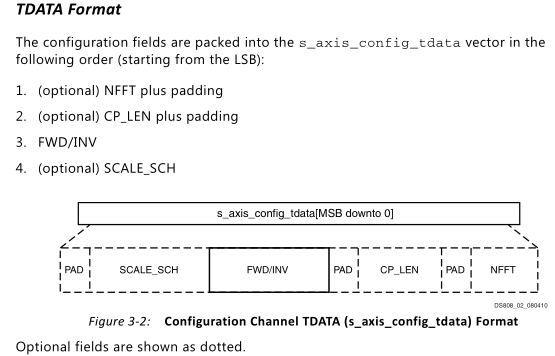

其中s:slave(从),m:master(主)。 s_axis_config_tdata具体参数:

其中NFFT、CP_LEN为optional,各预留8bit,FWD/INV为确定,例如FWD/INV为3bit,则总共占用19bits. s_axis_config_tdata参数举例:

A core has a configurable transform size with a maximum size of 128 points, cyclic prefix insertion and 3 FFT channels. The core needs to be configured to do an 8 point transform, with an inverse transform performed on channels 0 and 1, and a forward transform performed on channel 2. A 4 point cyclic prefix is required.

分析:

其中CP_LEN(cyclic prefix length,例如长度1024,则CP_LEN取值0~1023)。由于是8点FFT,根据下表:

确定NFFT:00011 ,由于各个参数8bit,因此padding-000,000 00011

确定CP_LEN:8点FFT,4 point cyclic prefix is required,因此对于128点,CP_LEN为64,1000000,补齐8bit:01000000

确定FWD/INV:3channels,且1代表FFT,0代表IFFT,因此:100,补齐8bit:00000100

确定SCALE_SCH:

1. For Burst I/O architectures, the scaling schedule is specified with two bits for each stage, with the scaling for the first stage given by the two LSBs.

2. The scaling can be specified as 3, 2, 1, or 0, which represents the number of bits to be shifted.

3. An example scaling schedule for N =1024, Radix-4, Burst I/O is [1 0 2 3 2] (ordered from last to first stage).

4. For N =128, Radix-2, Burst I/O or Radix-2 Lite, Burst I/O, one possible scaling schedule is [1 1 1 1 0 1 2] (ordered from last to first stage).

5. For Pipelined, Streaming I/O architecture, the scaling schedule is specified with two bits for every pair of Radix-2 stages, starting at the two LSBs. For example, a scaling schedule for N = 256 could be [2 2 2 3]. When N is not a power of 4, the maximum bit growth for the last stage is one bit. For instance, [0 2 2 2 2] or [1 2 2 2 2] are valid scaling schedules for N = 512, but [2 2 2 2 2] is invalid. For this transform length. the two MSBs of SCALE_SCH can only be 00 or 01.

6. This port is only available with scaled arithmetic (not unscaled, block floating-point or single precision floating-point).

三、仿真测试

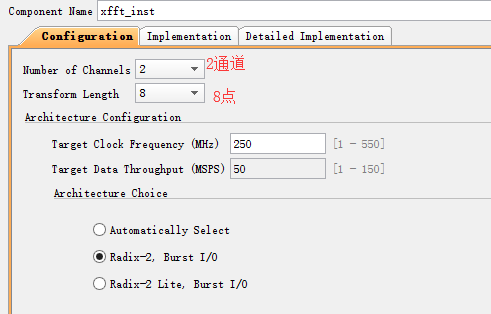

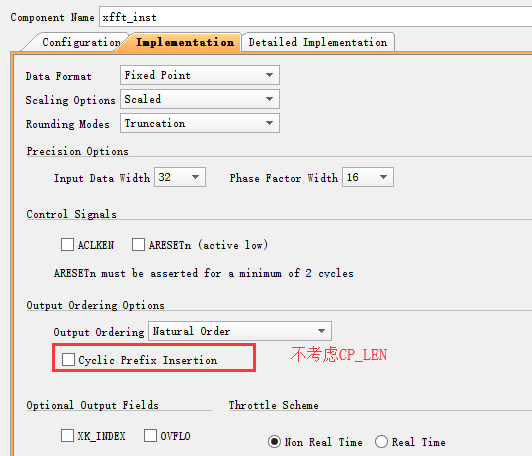

假设需要2通道8点的FFT运算,通道1进行FFT,通道2进行IFFT,不考虑CP_LEN:

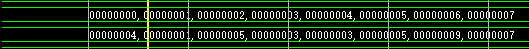

仿真测试,对应us_axis_config_tdata,不包含CP_LEN,不考虑缩放,[ FWD/INV, NFFT ] = [00000000,0 01 00011]【此处参数设置有误,待细究。】,仿真结果:

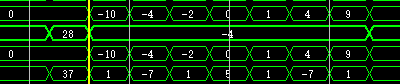

FFT输出结果:

详细参考:印象笔记:1/0019/013