总线及数据传输技术【待完善】

作者:桂。

时间:2017-08-05 14:41:36

链接:http://www.cnblogs.com/xingshansi/p/7290224.html

前言

最近的工作内容涉及硬件,三个高频词汇:总线、接口、协议,例如I2C、PCIe、RS-232C、RapidIO(SRIO)以及Aurora等等,往细里说还有数据的带宽、位宽、工作频率、数据传输可靠性等等,打算不定期更新,梳理出一篇文章,理理头绪。

知识范畴:高速串行接口、计算机网络基础(OSI-Open System Interconnection的七层协议:不同设备的互联以及数据交换)、总线(BUS)技术

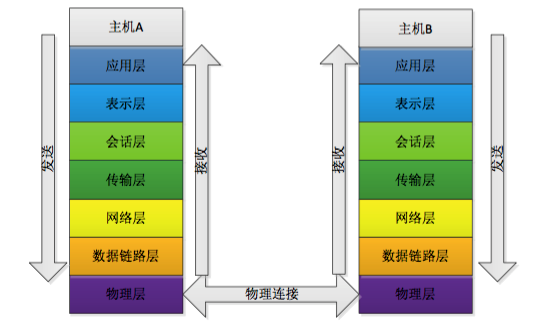

一、OSI七层协议

OSI 模型各层间关系和通讯时的数据流向如图所示:

这个类似于今天的快递:一个名叫主机A的男孩有封信(数据)要寄给名叫主机B的姑娘:

主机A → 快递小哥,快递小哥根据数据特性对物品打包并填写的信息 → 成为包裹(数据添加了一些协议头)→ 根据地址特性,不同的卡车/飞机运往其他城市 → 流程逆过来,直到一个名叫主机B的用户收到包裹,流程结束。

各层的解释:

- 应用层:就是应用软件使用的协议,如邮箱使用的POP3,SMTP、远程登录使用的Telnet、获取IP地址的DHCP、域名解析的DNS、网页浏览的http协议等;这部分协议主要是规定应用软件如何去进行通信的。

- 表示层:决定数据的展现(编码)形式,如同一部电影可以采样、量化、编码为RMVB、AVI,一张图片能够是JPEG、BMP、PNG等。

- 会话层:为两端通信实体建立连接(会话),中间有认证鉴权以及检查点记录(供会话意外中断的时候可以继续,类似断点续传)。

- 传输层:将一个数据/文件斩件分成很多小段,标记顺序以被对端接收后可以按顺序重组数据,另外标记该应用程序使用的端口号及提供QOS。(不同的应用程序使用不同计算机的端口号,同样的应用程序需要使用一样的端口号才能正常通信)

- 网络层:路由选路,选择本次通信使用的协议(http、ftp等),指定路由策略及访问控制策略。(IP地址在这一层)

- 数据链路层:根据端口与MAC地址,做分组(VLAN)隔离、端口安全、访问控制。(MAC地址在这一层)处理VLAN内的数据帧转发,跨VLAN间的访问,需要上升到网络层。

- 物理层:将数据最终编码为用0、1标识的比特流,然后传输。(例如将题主头像的图片,变为一串01100111100这样的数字来表示)。

以上参考知乎。

例如一些常见的网络互联设备:

1)中继器(repeater):物理层的网络互联设备;

2)网桥(bridge):网桥属于作用在物理层和数据链路层的存储转发设备,在两个相同类型的网段之间进行帧中继,在局域网之间存储或转发数据帧。

网桥用于在局域网中连接同一类型的不同网段,互连采用不同传输速率、不同传输介质的网络,即网桥所链接的不同网段之间,在网桥两侧的网络中,其网络协议和地址应该一致。

3)路由器(router):路由器工作在物理层、数据链路层和网络层,它比中继器和网桥更复杂一点,并包含有软件。在路游击所包含的地址之间,可能存在若干路径,路由器可以为某次特定的传输选择一条最好的路径。

4)网关:网关又被称为网间协议变换器,用以实现不同通信协议的网络之间的互联,一个普通的网关可用于连接两个不同的总线/网络,并由网关进行协议转换,提供更高层次的接口。网关允许在具有不同协议和报文组的两个网络之间传输数据,在报文从一个网段到另一个网段的传送中,网关提供了一种方式把报文重新封装,形成新的报文组。

二、高速数据传输

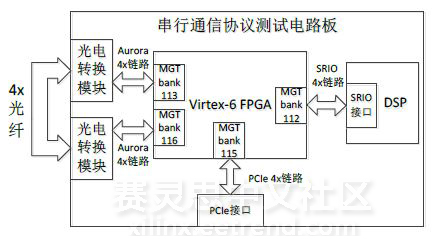

目前涉及的高速数据传输都是利用串口(并口不是更快?参考知乎)。Xilinx的V7系列有GTX/H/Z模块,以提供高速串行通信支持。同时Xilinx提供多种串行通信协议IP核,Aurora 8B/10B,PCI Express 2.0和Serial RapidIO 2.0是其中较为常用的三种协议。

几种传输的实现方式:

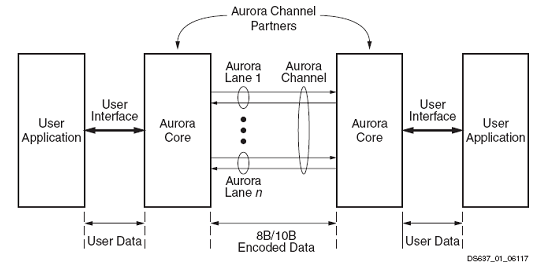

A-Aurora 8B/10B

Aurora协议是Xilinx公司提供的一个链路层协议,可以用来进行点到点的串行数据传输。Aurora允许器件之间以下图方式通过多个MGT通道绑定完成通信。单个GTX可以实现现750Mbit/s-6.5Gbit/s的通信传输,多个GTX通道的组合可实现几十Gbit/s 甚至上百Gbit/s的通信传输。

8B/10B即把8位数据编码为10位数据。Aurora提供了可直接与FIFO对接的用户接口,而其他协议通常需要用户自行编写GTP接口逻辑。

Aurora核初始化的Aurora通道可传输任意大小的数据帧,且能在任意时刻打断。数字信号T0经过FPGA存入FIFO,通过FIFO对数据的存取实现光纤对数据的收发,再由光纤自接收,通过FOGA恢复T0信号。 高速收发器、Aurora、光纤几个概念便串了起来。

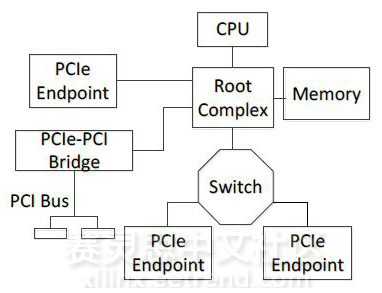

B-PCI-Express 2.0

参考:http://xilinx.eetrend.com/article/7995

PCI Express(简称PCIe)总线技术是取代PCI的第三代IO技术。PCIe采用串行点对点互联,允许每个设备拥有专属的一条连接,不争夺带宽资源,同时保证了数据的完整性。PCI Express 2.0协议的链路线速率达到5Gb/s,最高支持32X链路。

PCIe总线以包的形式在不同器件之间交换信息,数据按照协议首先被封装成一个包头,该包头长度在32bit地址下为12字节,当数据进入数据链路层后,会添加2字节的序列号和4字节的LCRC字段,数据包进入物理层后,使用1字节的开始字符和1字节的结束字符将其封装成帧。

C-Serial RapidIO 2.0

RapidIO是针对嵌入式系统芯片间和板间互联而设计的一种基于包交换的高速串行标准。

SRIO是物理层采用串行差分模拟信号传输的RapidIO标准。SRIO 2.0协议性能进一步增强,链路线速率可达6.25Gb/s.

D-三种协议比较

1)协议结构:Aurora仅定义链路层+物理层,PCIe 2.0以及 SRIO 2.0都比Aurora复杂;

2)网络拓扑结构:

- Aurora 8B/10B协议不支持网络拓扑结构

- PCIe规定了生成树拓扑结构,这种结构适合于单个主机,多个外围设备通信模式,但限制了端点数量,且不支持任意节点与节点间直接通信。PCIe的典型网络拓扑结构如下图所示:

- SRIO的拓扑结构比PCIe更为灵活,可设计成网型,星型,雏菊链或树形拓扑结构,支持节点对节点通信,各节点间可对等的发起数据传输。

3)线路速率(目前V7能力?待确认):Aurora 8B/10B协议在链路数目和链路线速率选择上比较灵活,链路数目可以在1x至16x之间自由选择,链路线速率可以在0.5Gb/s到6.6Gb/s间自由选择。PCIe 2.0支持1x,2x,4x,8x,12x,16x,32x链路,链路线速率支持2.5Gb/s和5.0Gb/s。SRIO 2.0支持1x、2x、4x、8x和16x链路,链路线速率支持1.25Gb/s、2.5Gb/s、3.125Gb/s、5.0Gb/s和6.25Gb/s。

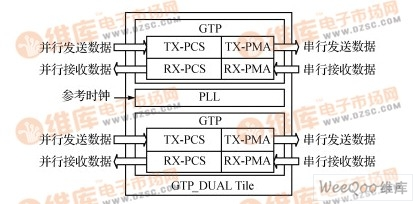

E-RocketIO

RocketIO收发器是在Virtex2 Pro以上系列FPGA中集成的专用串行通信模块,在使用时不占用FPGA其他逻辑与片上存储资源。在Virtex5 LXT和SXT系列FPGA中,RocketIO称为GTP,每两个GTP共用一个PLL,组成一个GTP_Dual。其结构框图如下图所示。后来的GTX/H/Z都可以理解成升级版的RocketIO,指的是串行的高速收发模块。

DMA介绍:http://www.51hei.com/stm32/3864.html

三、总线技术

A-总线分类

总线(BUS,即公共汽车,数据的公共传输路线)分类的方式有很多,如被分为外部和内部总线、系统总线和非系统总线等等,下面是几种最常用的分类方法。

另外,总线的传输核心思想是多路复用:时分多路复用-TDMA/频分多路复用-FDMA/码分多路复用-CDMA。

1.2.1按功能分

以微机系统为例:

(1) 片总线(Chip Bus, C-Bus) 又称元件级总线,是把各种不同的芯片连接在一起构成特定功能模块(如CPU模块)的信息传输通路,它的宽度可以是8、16、32或64位。目前比较流行的几种内部总线技术:I2C总线、SCI总线等。

(2) 内总线(Internal Bus, I-Bus) 又称系统总线或板级总线,是微机系统中各插件(模块)之间的信息传输通路。例如CPU模块和存储器模块或I/O接口模块之间的传输通路。常用的有PC总线、AT总线(ISA总线)、PCI总线等。

(3) 外总线(External Bus, E-Bus)

又称通信总线,是微机系统之间或微机系统与其他系统(仪器、仪表、控制装置等)之间信息传输的通路,如EIA RS-232C、IEEE-488等。

其中的系统总线,即通常意义上所说的总线,一般又含有三种不同功能的总线,即数据总线DB、地址总线AB和控制总线CB。

地址总线是专门用来传送地址的。在设计过程中,见得最多的应该是从CPU地址总线来选用外部存储器的存储地址。地址总线的位数往往决定了存储器存储空间的大小,比如地址总线为16位,则其最大可存储空间为216(64KB)。

数据总线是用于传送数据信息,它又有单向传输和双向传输数据总线之分,双向传输数据总线通常采用双向三态形式的总线。数据总线的位数通常与微处理的字长相一致。例如Intel 8086微处理器字长16位,其数据总线宽度也是16位。在实际工作中,数据总线上传送的并不一定是完全意义上的数据。

控制总线是用于传送控制信号和时序信号。如有时微处理器对外部存储器进行操作时要先通过控制总线发出读/写信号、片选信号和读入中断响应信号等。控制总线一般是双向的,其传送方向由具体控制信号而定,其位数也要根据系统的实际控制需要而定。

1.2.2按传输方式分

按照数据传输的方式划分,总线可以被分为串行总线和并行总线。从原理来看,并行传输方式其实优于串行传输方式,但其成本上会有所增加。通俗地讲,并行传输的通路犹如一条多车道公路,而串行传输则是只允许一辆汽车通过单线公路。目前常见的串行总线有SPI、I2C、USB、IEEE1394、RS232、CAN等;而并行总线相对来说种类要少,常见的如IEEE1284、ISA、PCI等。

1.2.3按时钟信号方式分

按照时钟信号是否独立,可以分为同步总线和异步总线。同步总线的时钟信号独立于数据,也就是说要用一根单独的线来作为时钟信号线;而异步总线的时钟信号是从数据中提取出来的,通常利用数据信号的边沿来作为时钟同步信号。

B-总线评价指标

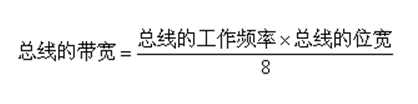

总线的带宽指的是单位时间内总线上传送的数据量,即每钞传送MB的最大数据传输率。

总线的位宽指的是总线能同时传送的二进制数据的位数,或数据总线的位数,即32位、64位等总线宽度的概念;总线的位宽越宽,数据传输速率越大,总线的带宽就越宽。

总线的工作时钟频率以MHz为单位,它与传输的介质、信号的幅度大小和传输距离有关。在同样硬件条件下,我们采用差分信号传输时的频率常常会比单边信号高得多,这是因为差分信号的的幅度只有单边信号的一半而已。

总线的带宽、位宽和工作频率,这三者密切相关,它们之间的关系:

C-总线通信协议

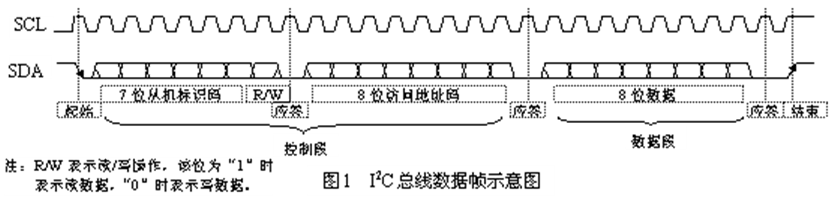

对于总线的学习,了解其通讯协议是整个过程中最关键的一步,所有介绍总线技术的资料都会花很大的篇幅来描述其协议,特别是文中第一部分关于ISO/OSI的那七层定义。其实要了解一种总线的协议,最主要的就是去了解总线的帧数据每一位所代表的特性和意义,总线各节点间有效数据的收发都是通过各节点对帧数据位或段的判断和确信来得以实现。

上图所示是常见的I2C总线上传输的一字节数据的数据帧,其总线形式是由数据线SDA和时钟SCL构成的双线制串行总线,并接在总线上的电路模块即可作为发送器(主机)又可作为接收器(从机)。帧数据中除了控制码(包括从机标识码和访问地址码)与数据码外还包括起始信号、结束信号和应答信号。

起始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

控制码:用来选泽操作目标与对象,即接通需要控制的电路,确定控制的种类对象。在读期间,也即SCL时钟线处于时钟脉冲高电平时,SDA上的数据位不会跳变。

数据码:是主机向从机发送的具体的有用的数据(如对比度、亮度等)和信息。在读期间,SDA上的数据位不会跳变。

应答信号:接收方收到8bit数据后,向发送方发出特定的低电平。读/写的方向与其它数据位正好相反,也即是由从机写出该低电平,主机来读取该低电平。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变表示数据帧传输结束。

当然不同的总线其数据位或段的定义肯定不同,但依据同样的原理可以更快的去了解它的协议的特性和特点。虽然其信息帧的大小不一,但具体的某一数据位或数据段都类似于本文所提及的I2C总线,会依据它的协议的要求来定义它所达标的意义和功能。

四、常用总线协议

记录用到的总线的细节信息。

A-I2C总线

http://blog.csdn.net/ce123_zhouwei/article/details/6877000

http://www.cnblogs.com/Camilo/p/3778868.html

B-

C-

参考:

- 总线:http://blog.csdn.net/ce123_zhouwei/article/details/6853195

浙公网安备 33010602011771号

浙公网安备 33010602011771号