verilog学习(5)实战3之计数器与bus

一:计算机中位的概念

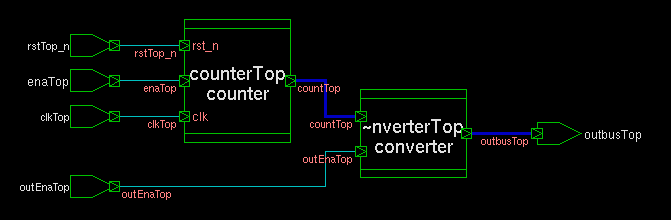

所要设计的电路(我是从结果dve里得到的,本来想用visio画的,懒。。)

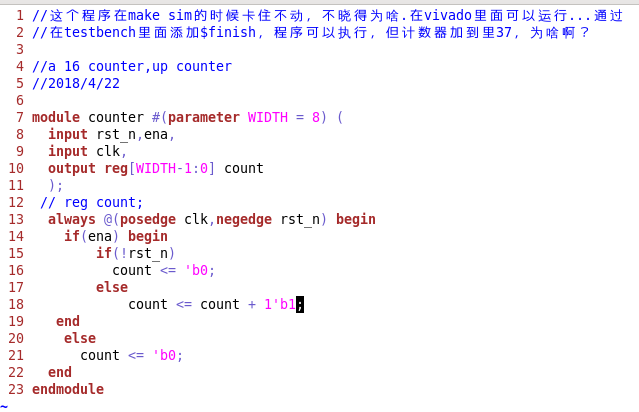

二:计数器设计

1:counter.v代码

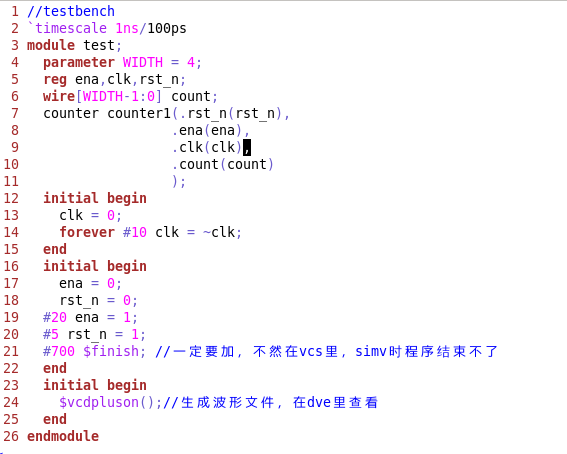

2:testbench for counter

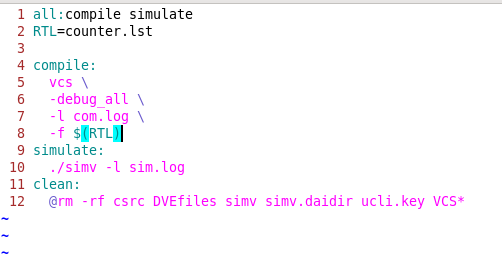

3:写makefile

4:在终端运行检查逻辑仿真是否正确。

三:bus设计

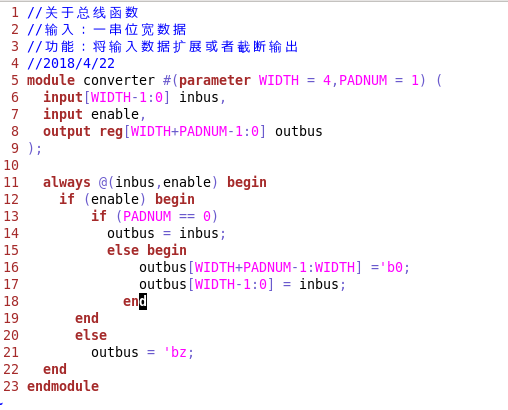

1:converter.v设计

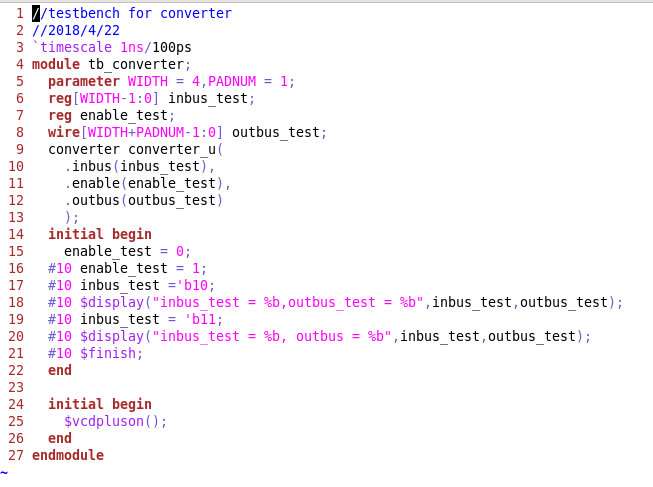

2:testbench for converter

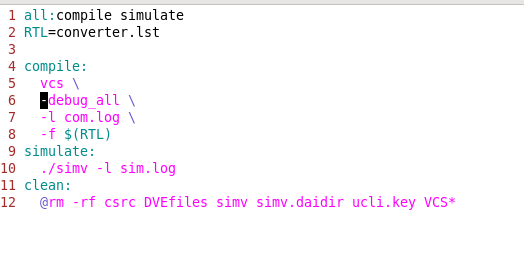

3:makefile

4:在终端检查逻辑仿真有没有问题

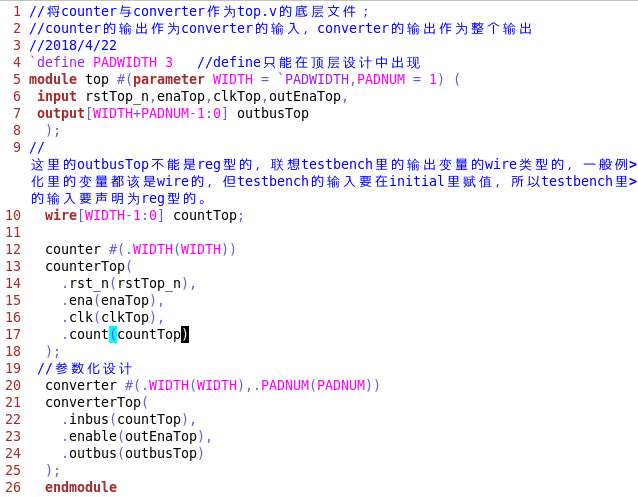

三:顶层设计

1:顶层源文件top.v

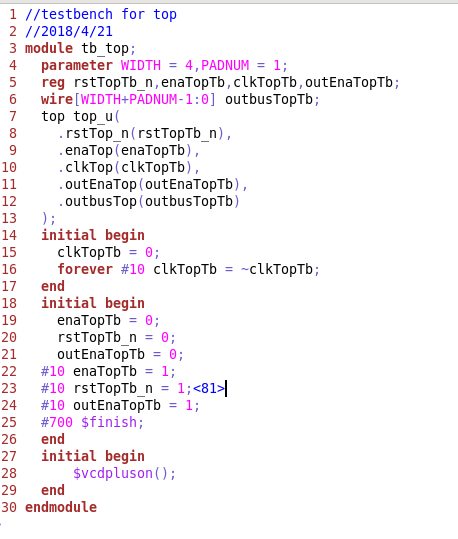

2:顶层设计testbench

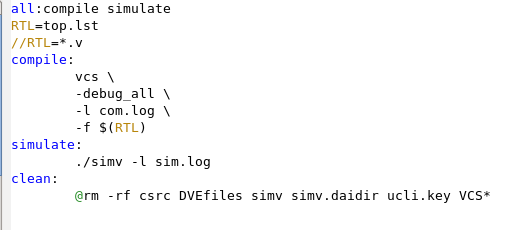

3:makefile

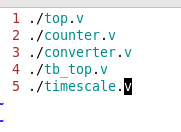

4:top.lst

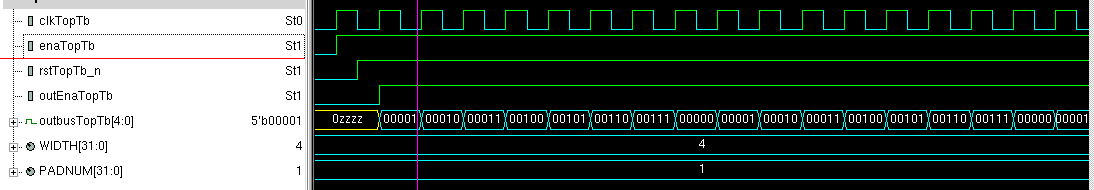

5:在终端make,使用dve &查看波形

四:对顶层设计综合

1:在设计工程项目中新建syn文件夹存放综合文件

2:将synopsys_dc.setup文件以及library文件放在syn中(前面DC学习中讲过这方面内容http://www.cnblogs.com/xh13dream/p/8672260.html)

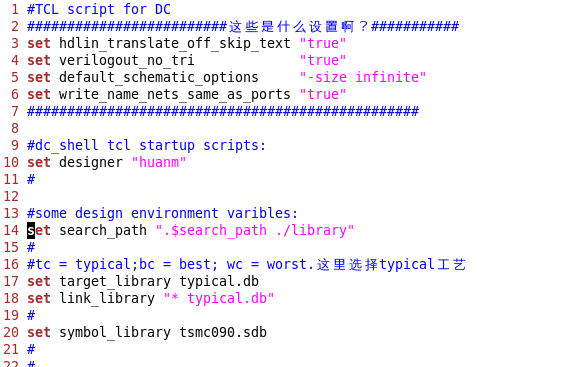

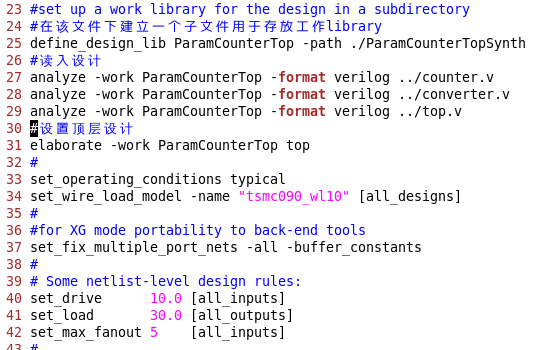

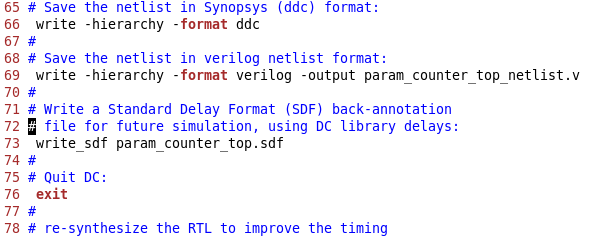

3:写约束文件syn.tcl

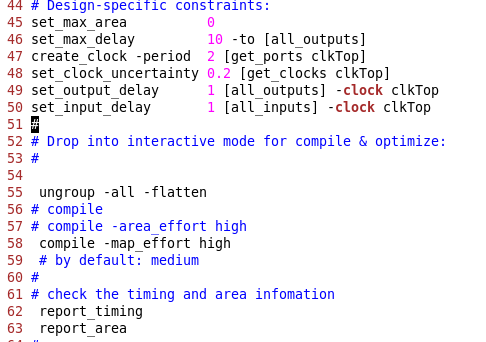

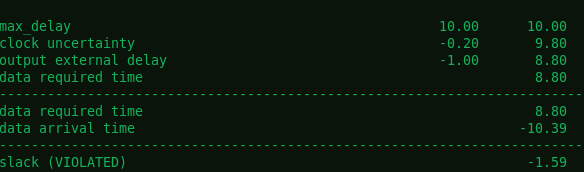

4:执行dc_shell -f syn.tcl,得到部分综合内容

slack为负,不满足综合要求,改约束等等使slack大于0。