RTL基本知识:如何正确在敏感信号列表中包含function中的信号

在使用Verilog建模组合逻辑时,经常会使用“@*”的方式实现将进程中素有输入信号隐含加入到敏感信号列表中。但是如果该进程中包含对函数的引用时,尽管使用“@*”,综合前后的仿真结果还是有出现不一致的情况。本文将对此进行示例说明。

1 问题示例

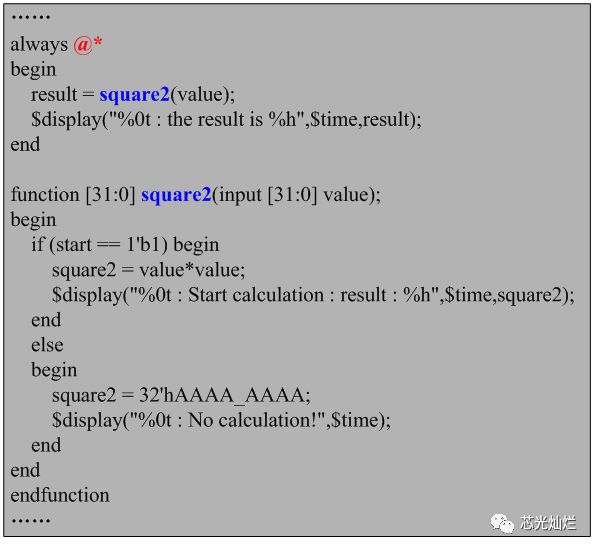

Verilog中可以在always后使用“@*”来代替冗长的敏感信号列表,这样做虽然在一定程度上可以保证仿真和综合的一致性,但是在一些情况下并不完全正确。例如下例,其中的函数引用了全局变量start,期望在start或者value发生变化时分别输出不同的仿真结果和信息:

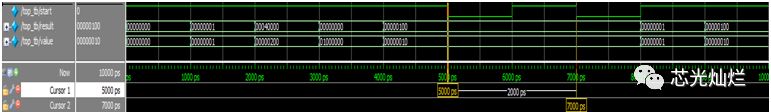

仿真后的结果和信息如下:

在5ns和7ns处,全局信号start发生变化,且always语句使用了“@*”隐含增加了过程性语句中的所有信号,但是always调用的函数square2并没有执行,导致了仿真结果异常,并没有在start发生变化时输出预期的结果,显然“@*”并没有监测到start的变化。为此,对代码进行小部分修改,如下:

更多资讯,请关注个人公众号:芯光灿烂

【魏老师说IC】旨在通过该平台为大家提供一个集成电路技术交流、分享、学习的平台,如果有任何问题或者咨询,可以在博客中留言或者关注个人微信公众号“芯光灿烂”进行更深入的交流和学习。