真正的RISC-V开发板——VEGA织女星开发板开箱评测

前言

由于最近ARM公司要求员工“停止所有与华为及其子公司正在生效的合约、支持及未决约定”,即暂停与华为的相关合作,大家纷纷把注意力投向了另一个的处理器架构RISC-V,它是基于精简指令集(RISC)的一个开源指令集架构。相比于其他指令集,"RISC-V 指令集可以自由地用于任何目的,允许任何人设计、制造和销售 RISC-V 芯片和软件",正是由于这种开放性,于2015年成立的RISC-V基金会,吸引了很多科技巨头加入RISC-V基金会,现在的RISC-V基金会成员已经超过了235个,包括国外的Google、三星、英伟达、微芯、高通、惠普、意法半导体、西数、NXP等,国内的阿里巴巴、华为、高云等公司。可能是由于智能推荐的算法,我在知乎上的一篇关于RISC-V文章:国产处理器的逆袭机会——RISC-V,最近收到了很多网友的关注和评论。正好前一段时间申请到一块NXP恩智浦的一款真正的RISC-V开发板——织女星开发板,所以拿来玩玩,学习一下RISC-V架构处理器的开发。

关于RISC-V架构

RISC-V(发音同“risk-five”)是一种免费开源指令集架构(ISA),通过开放标准协作开创处理器创新的崭新纪元。RISC-V基金会创立 于2015年,由超过235家成员组织组成,建立了首个开放、协作的软硬件创新者社区,开创了处理器创新的新时代。RISC-V ISA发端于深厚的学术研究,将免费且可扩展的软硬件架构自由度提升至新的水平,为未来50年的计算设计与创新铺平了道路。——来自RISC-V_百度百科

现在的处理器指令集主要分为RISC和CISC,即精简指令集和复杂指令集,RISC的代表就是著名的ARM架构,专注于高性能,低功耗,小体积,主要应用于移动设备;而CISC的代表是x86架构,像常用的PC、服务器的CPU等等,专注于桌面,高性能和民用市场。

而RISC-V是属于RISC阵营的,RISC-V,即第五代精简指令集。相比于ARM,RISC-V的历史很短,2010年诞生于加州大学伯克利分校,当时的Krste Asanovic教授希望寻找一个合适的CPU指令架构,但x86架构复杂臃肿、ARM架构需要授权费、开源的OpenRISC架构又太老旧了,所以他最终决定自己做个开源CPU架构,并在2015年成立了RISC-V基金会(RISC-V Foundation ),专门推动RISC-V发展,现在的RISC-V基金会成员也超过了235个,包括国外的Google、三星、英伟达、微芯、高通、惠普、意法半导体、西数、NXP,国内的阿里巴巴、华为、高云等公司。最新的RISC-V基金会成员:RISC-V基金会成员列表

本着大道至简的原则,《RISC-V架构文档(The RISC-V Instruction Set Manual)》仅有236页,熟悉体系结构的工程师仅需一至两天便可将其通读,虽然RISC-V的架构文档还在不断地丰富,但是相比x86的架构文档与ARM的架构文档,RISC-V的篇幅可以说是极其短小精悍。

ARM处理器按位数可分为32位和64位,按架构又可分为Cortex-A/Cortex-R/Cortex-M三大系列,分别针对不同的应用领域。而RISC-V也有很多内核,截止目前(2019-06-22),RISC-V社区显示的Core共有29个,SOC PLATFORM共有13个,SOC共有7个。

- 部分RISC-V Core

| RISC-V Core | Supplier | Github | Bit | License |

|---|---|---|---|---|

| RI5CY | ETH Zurich, Università di Bologna | Github | 32 | Solderpad Hardware License v. 0.51 |

| Zero-riscy | ETH Zurich, Università di Bologna | Github | 32 | Solderpad Hardware License v. 0.51 |

| Hummingbird E200 | Bob Hu(胡振波) | Github | 32 | Apache 2.0 |

| Riscy Processors | MIT CSAIL CSG | Github | / | MIT |

| SweRV EH1 | Western Digital | Github | 32 | Apache 2.0 |

| K210 | Kendryte(嘉楠耘智) | Github | 64 | BSD |

| freedom | SiFive | Github | / | BSD |

- RISC-V SoC

| RISC-V SoC | Supplier | Core | OS | Bit | Link |

|---|---|---|---|---|---|

| RV32M1 | NXP | RI5CY,Zero RI5CY,ARM Cortex-M4F,ARM Cortex-M0+ | RTOS | 32 | Datasheet |

| FE310-G000 | SiFive | E31 | RTOS | 32 | Datasheet |

| FE310-G002 | SiFive | E31 | RTOS | 32 | Product Page |

| Freedom U540 | SiFive | U54, E51 | Linux | 64 | Product Page |

| GAP8 | GreenWaves Technologies | PULP / 1 + 8 RI5CY | RTOS | 32 | Product Page |

| K210 | Kendryte(嘉楠耘智) | K210 | RTOS | 32 | Datasheet |

| RavenRV32 | efabless | PicoRV32 | RTOS | 32 | Datasheet |

关于VEGA织女星开发板

织女星开发板是OPEN-ISA社区为中国大陆地区定制的一款体积小、功耗超低和功能丰富的基于RV32M1 的 RISC-V评估开发板。利用该开发板,用户可以快速建立一个使用 RV32M1 的 RISC-V应用和演示系统。

RISC-V内核支持使用SEGGER公司的JLink调试器来进行程序的下载、调试,没错,就是那个经常用来调试ARM内核的调试器,要使用带有TMS(SWDIO)、TCLK(SWCLK)、TDI、TDO接口的调试器,不能使用那种只有SWDIO和SWCLK的调试器。当然,也可以使用板载的FreeLink调试器,不过在使用板载调试器调试RISC-V之前,需要使用LPCScrypt_installer_2.1.0_842.exe软件,把FreeLink的CMSIS-DAP固件升级为JLink固件,这样才可以调试RISC-V核。可以参考:织女星开发板调试器升级为Jlink固件

之所以说这是一块真正的RISC-V开发板,是因为它的主控芯片RV32M1是真正的RISC-V内核芯片,众所周知,市面上很多RISC-V开发板基本都是基于FPGA实现的RISC-V软核处理器。

基于FPGA实现的RISC-V开发板

- Perf-V:国内澎峰科技出品,基于Xilinx Artix-7系列FPGA-XC7A50T实现

- 蜂鸟E203:国内芯来科技出品,基于Xilinx Artix-7系列FPGA-XC7A75T,可以配置为RV32IC或RV32EC架构。

- 小脚丫STEP开发板:国内思得普科技出品,基于Intel公司Cyclone 10系列FPGA芯片10CL016YU256C8G

- 小脚丫STEP-MXO2 二代FPGA开发板:基于Lattice公司MXO2系列的FPGA芯片LCMO2-4000HC-4MG132

基于RISC-V芯片实现的开发板

- NXP VEGA织女星开发板:NXP恩智浦出品,基于NXP四核异构处理器,片上集成两个ARM内核和两个RISC-V内核,板载资源丰富。目前还买不到这块开发板和RV32M1芯片,想体验这块RISC-V板子的朋友,可以免费申请:NXP恩智浦VEGA织女星开发板免费申请!官方社区:OPEN-ISA社区

- Sipeed M1(荔枝丹)开发板:基于K210 RISC-V芯片,K210是国内嘉楠耘智的团队在2018年研发出一款7nmAI芯片,采用了基于rocket-chip的双核RV64GCC RISC-V CPU。

- Lichee Tang(荔枝糖)开发板:基于国产FPGA芯片EG4S20,EG4S20是国内安路科技开发设计的FPGA芯片,20K逻辑单元,130KB SRAM。

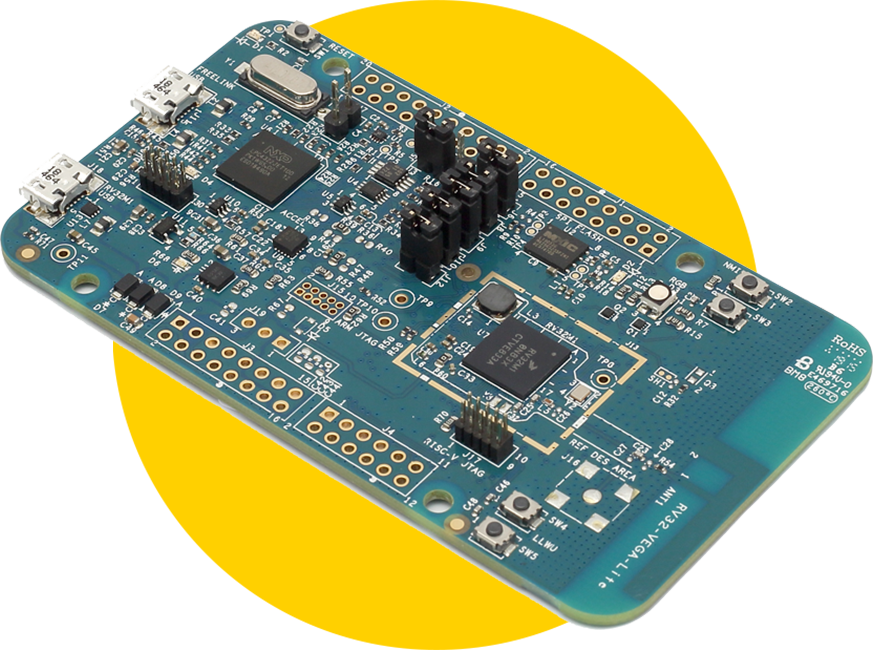

VEGA织女星开发板分为两种,一种是国际版,一种是国内版

- 国际版本VEGA开发板

- 国内版织女星开发板RV32-VEGA-Lite

硬件上稍微有所不同,软件上完全兼容国际版VEGABoad 开发板,充分利用已有的 OPEN-ISA的生态环境,希望进一步带动中国大陆地区 RISC-V的软件生态链。

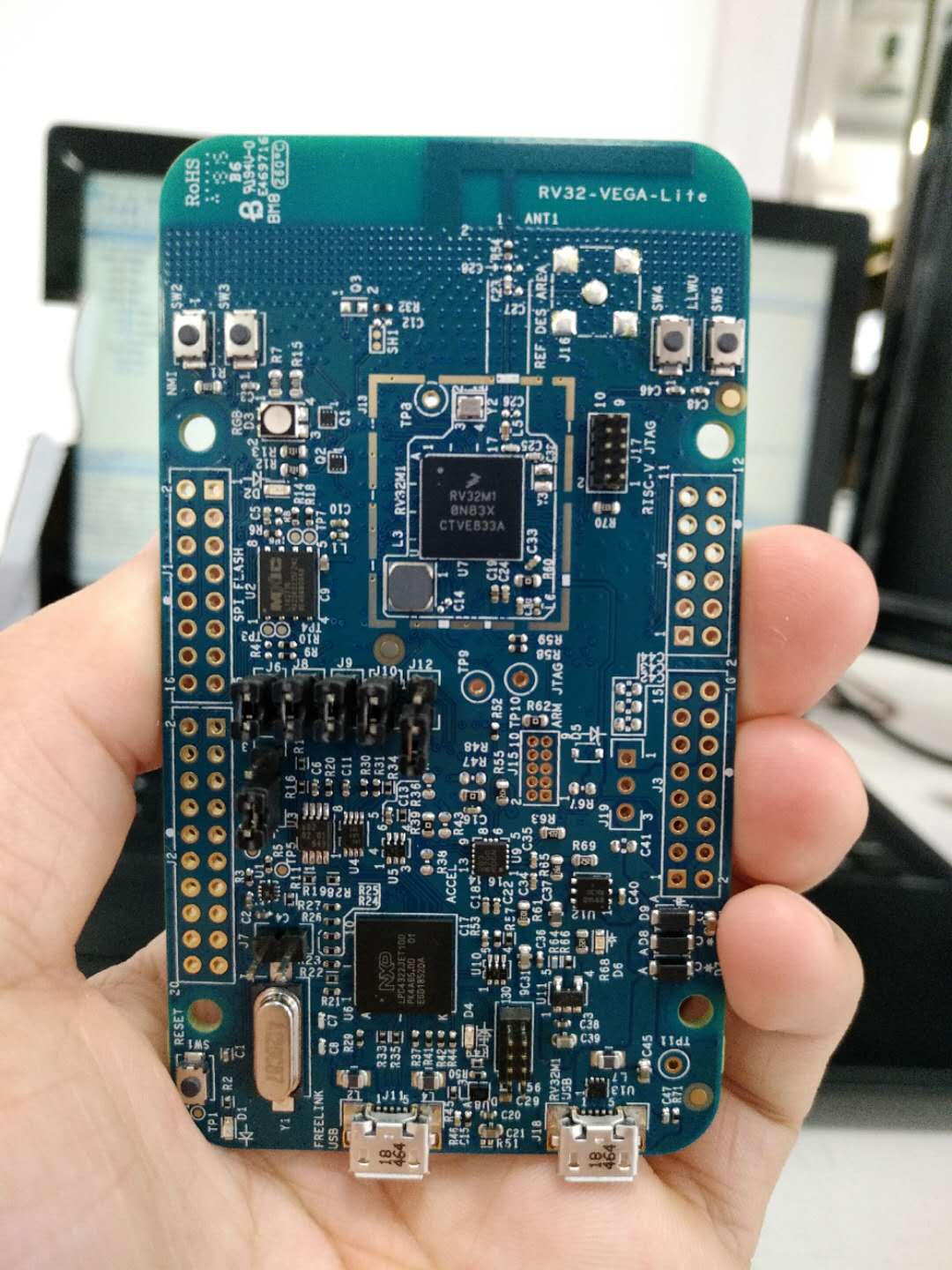

开箱爆照

这块开发板从申请到收到,大概用了两周的时间,包装盒、开发板、跳线帽、MicroUSB数据线,一应俱全,全国包邮,不得不说大厂就是大气。

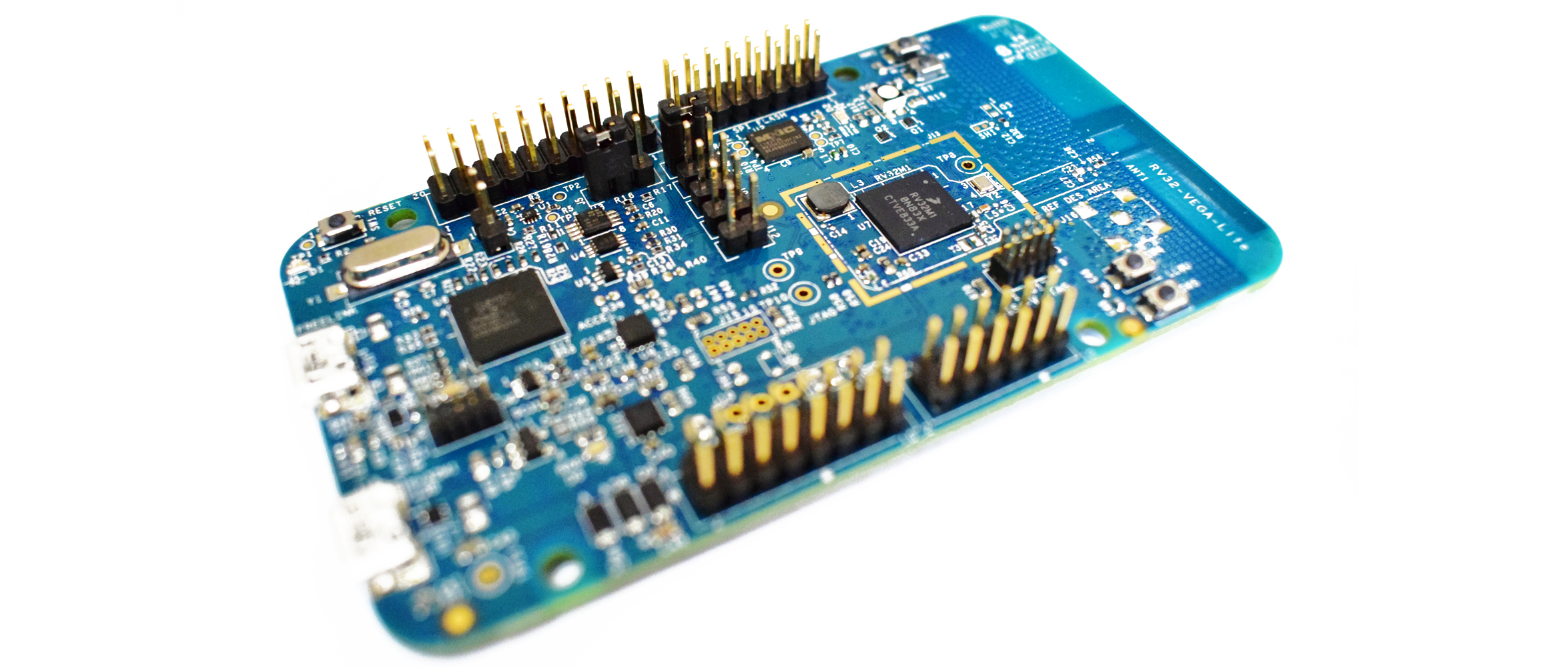

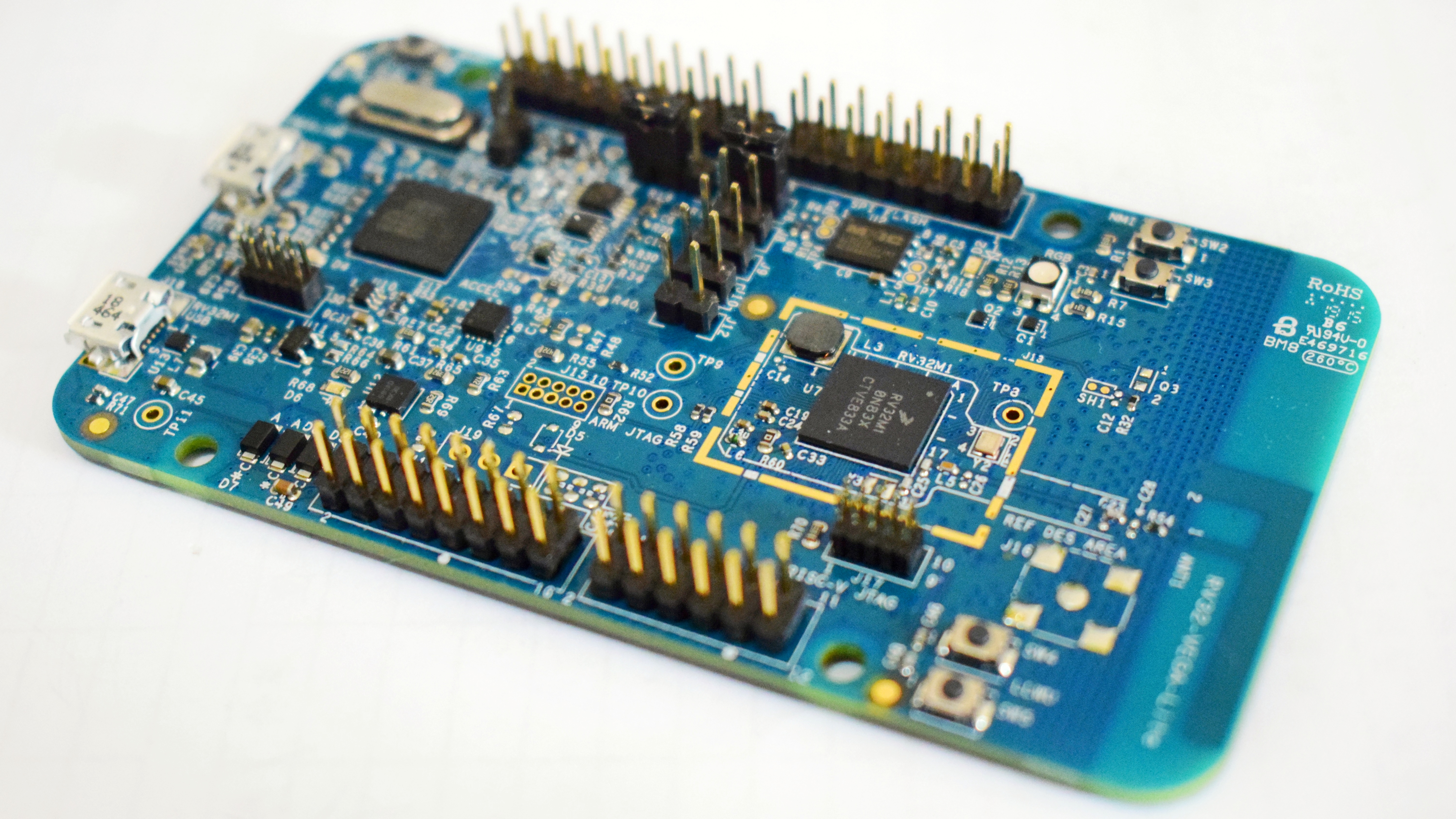

- 开发板正面

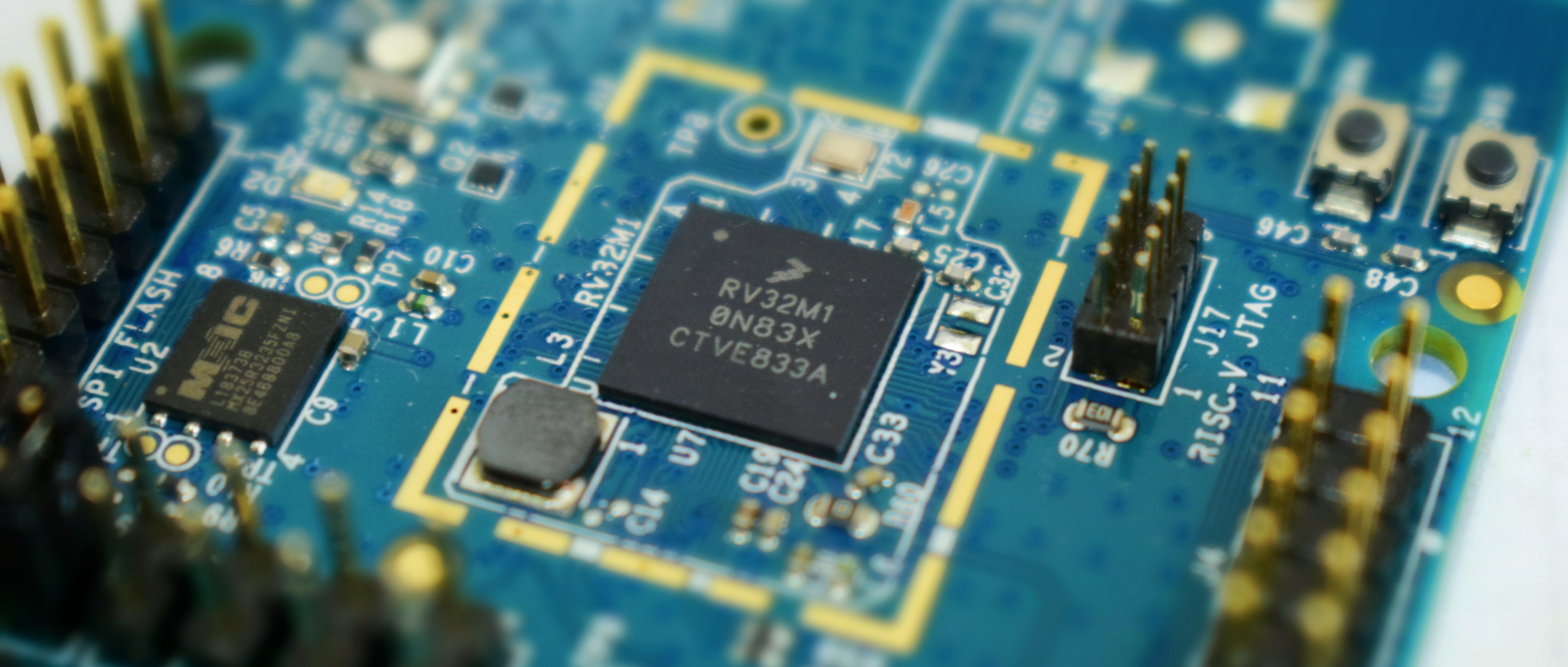

- 芯片特写

板载资源简介

VEGA织女星开发板采用6层PCB设计,以满足 RM32M1 设备所需的射频电路。沉金PCB工艺,蓝色油墨,白色丝印,符合欧盟RoHS标准,无铅环保。芯片周围留有屏蔽罩的焊接位置,不过并没焊接。好了,我们来看一下板载的资源吧。

- 主控芯片:恩智浦的RV32M1, 四核异构:两个ARM核,两个RISC-V核,自带无线功能。

- 板载调试器:基于LPC4322的FreeLink调试器,默认为CMSIS固件,升级为Jlink固件后可调试ARM核和RISC-V内核。

- 调试接口:两个ARM核共用一个JTAG调试口,两个RISC-V核共用一个JTAG调试口,可能是由于PCB空间大小的限制,这两个2*5P的接口并不是通用的2.54mm间距的排针,而是比较少用的1.25的排针,对于手头没有这种接口排线的朋友,可能不是很方便的使用,不过我们有万能的淘宝。

- RF射频电路:板载有射频电路,当然也留有了J16天线端子的位置。

- 串行Flash:美信的MX25R3235FZNIL0,4MB串行闪存,可以存储一些非易失性数据。

- 加速度和磁力传感器:恩智浦的FXOS8700CQ,六轴传感器,IIC接口

- SDHC卡槽:PCB背面留有位置,但是并没有焊接。

- 光敏传感器:PCB留有位置,没有焊接。

- 按键:4个用户按键,板载的两侧各2个,可以实现人机交互操作。

- LED指示:1个RGB和1个状态指示LED 。

- Arduino接口:内部的两排插座,是兼容Arduino的,如果之前玩过Arduino,那么它的一些扩展模块,可以直接使用,而无需连线。

- 调试跳线:板子中部留有两排跳线,一边是FreeLink调试器的输出,一边是RV32M1芯片的ARM调试接口,如果想使用板载调试器调试ARM内核,那么只需要使用几个跳线帽直接短接排针即可,但是如果想使用板载调试调试RISC-V内核,需要将跳线断开,并使用导线将FreeLink的调试输出和RISV-V调试接口J17相连接。

主控芯片RV32M1简介

要重点介绍一下织女星开发板的主控芯片RV32M1,RV32M1是一颗真正的 RISC-V芯片,其目的是为了扩大和推动 RISC-V生态系统的发展,让广大的MCU 嵌入式开发工程师有真正的 RISC-V 芯片可用。目前该芯片只供应给OPEN-ISA 社区生产评估开发板使用,不单独销售。如果需要样片,可以到社区申请。下面来看一下RV32M1的片上资源。

-

两个RISC-V内核,一个 RI5CY 核、一个 ZERO_RISCY 核。关于这两款RISC-V Core,是由博洛尼亚大学苏和黎世联邦理工学院(ETH Zurich, Università di Bologna)开发的32位内核,遵循Solderpad Hardware License v. 0.51许可。

-

两个ARM内核,一个 Cortex-M4F 核、一个 Cortex-M0+ 内核。

-

1.25 MB Flash 、384 KB SRAM

-

集成了可工作在 2.36 GHz 到 2.48 GHz 频率范围,支持 FSK/GFSK 和 O-QPSK调制的无线收发器。

-

支持低功耗蓝牙(BLE)、通用 FSK(支持250、500、1000、2000 kbps)或者 IEEE 802.15.4 标准,可以运行 BLE Mesh、Thread和 Zigbee协议栈。

-

两个ARM核共用一个JTAG调试口,两个RISC-V核共用一个JTAG调试口,每个核都可以运行在48MHz频率,但在高速模式(HSRUN)时,可达72MHz,如果要查看系统当前的运行频率,可以在主程序中使用如下函数来获取系统时钟频率:

uint32_t SysClk; SystemCoreClockUpdate(); SysClk = SystemCoreClock; PRINTF("系统时钟: %d \r\n", SysClk); -

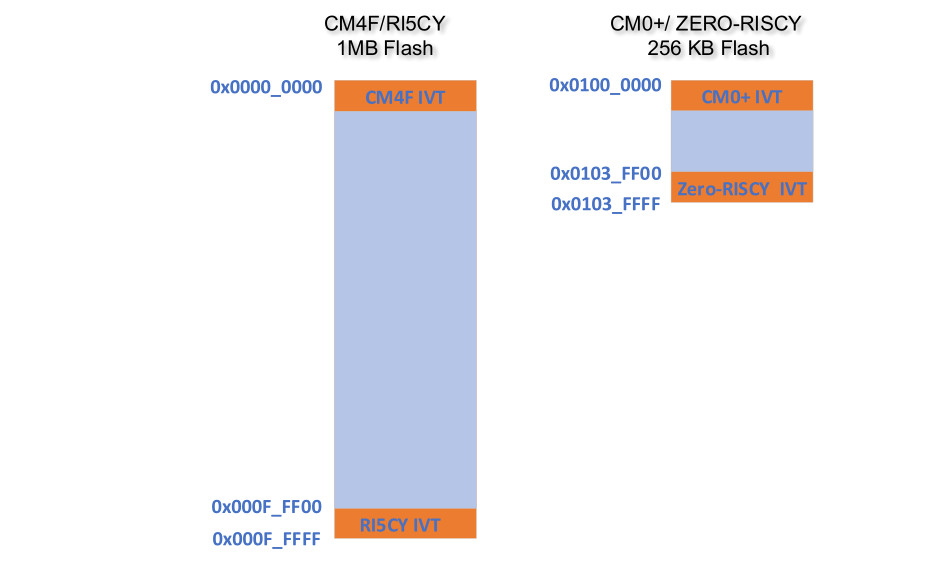

4个核被分为两个子系统,大核CM4F/RI5CY和小核CM0+/ZERO-RISCY,片上集成1.25 MB Flash 、384 KB SRAM,其中1 MB的Flash被大核所使用,起始地址0x0000_0000,另外的256 KB Flash被小核所使用,起始地址0x0100_0000。

-

Flash地址示意

-

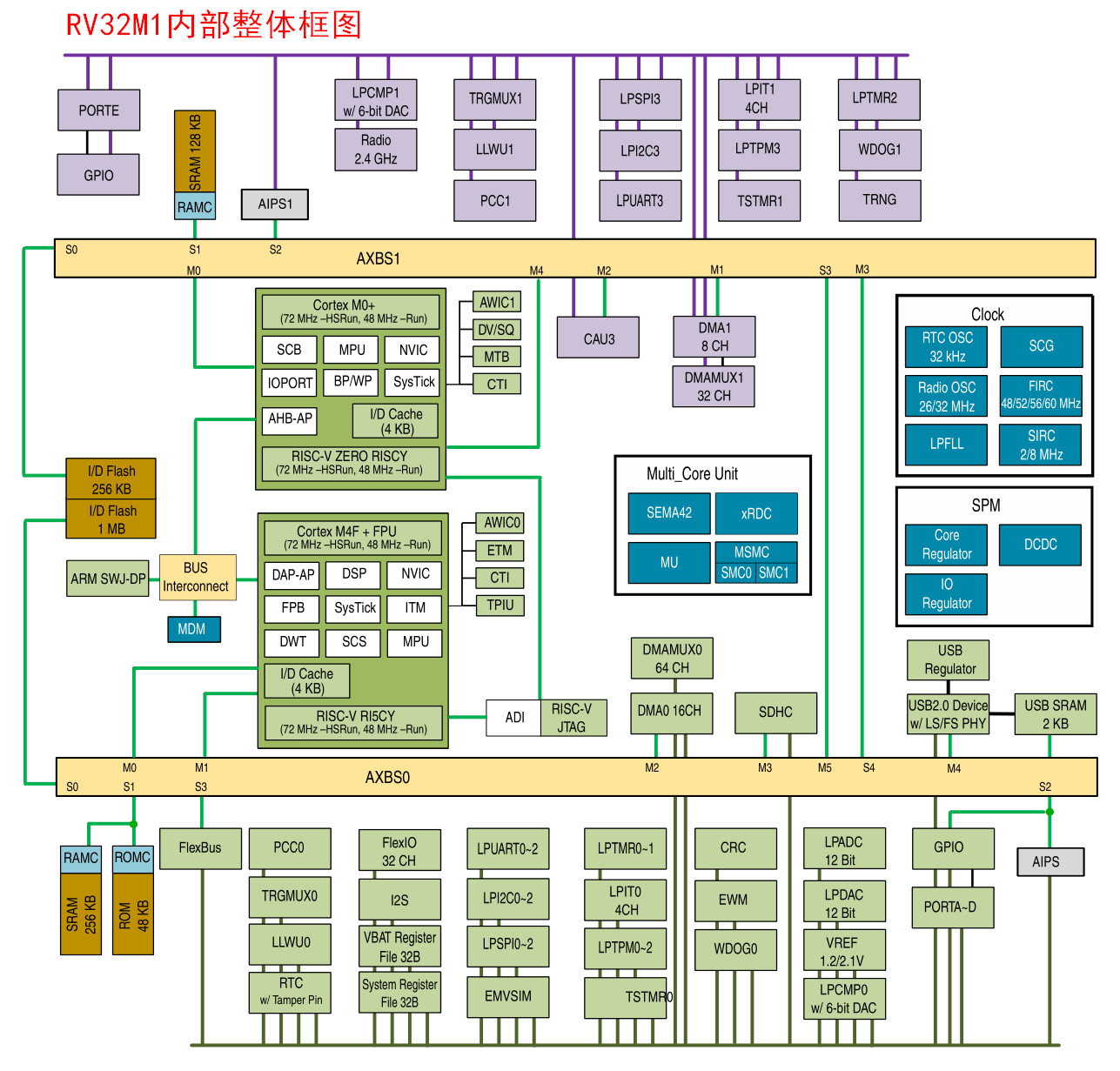

为了支持多核运行模式,RV32M1片上集成了多核管理系统(Multi_Core Unit),包括消息传递单元(Messaging Unit)、信号量2(SEMA42)、系统控制模块 (MSCM)、 扩展资源控制器 (XRDC)等模块,用于多核间的通信和控制。

-

内部整体框图

-

通过配置RV32M1片上的FOPT寄存器(Flash Option Register),可以支持上电时从不同的核来启动,默认从RISC-V RI5CY内核启动,如果要进行ARM核开发,如M4开发,则必须切换为从ARM核启动,否则当使用调试器进行程序下载时,根本不能识别到ARM芯片,这一点要特别注意。关于FOPT寄存器各位的描述,可以查看RV32M1参考手册P450,为了便于切换启动模式,官方已经为我们写好了配置文件,直接通过openocd和telnet软件就可以完成对FOPT寄存器的配置。

支持的开发工具

RISC-V核开发工具

- Eclipse开发框架 + GNU MCU Build Tools编译工具 + openocd调试软件 + riscv32-unknown-elf-gcc编译器

- GCC命令行编译

ARM核开发工具

和其他的ARM内核开发一样,织女星开发板的ARM内核开发,可以使用以下环境

- Keil-MDK

- IAR

- GCC命令行编译

注意:Keil环境要安装要安装openisa的器件支持包

关于织女星开发板开发环境的搭建及相关配置可以参考:

点亮一个LED

参考上述文章,搭建完成开发环境后,就可以导入Demo工程,点亮一个LED灯,如下效果。

参考资料

历史精选

欢迎关注我的个人博客:www.wangchaochao.top

或微信扫码关注我的公众号