SDRAM layout之等长理解

转载于: http://blog.sina.com.cn/s/blog_5fe66f090100fa2s.html

layout的时候,对SDRAM之类的,虽然走线可以不等长,但误差余量是多少却是一直都没有搞明白,结合SDRAM的控制时序作个简单的分析。

首先明白几个感念:

1.建立时间和保持时间,这里说的建立时间和保持时间是针对接收端而言的,建立时间(SetupTime)指的是数据在时钟沿到达之前必须保持稳定的最小时间,保持时间指的是数据在时钟沿到达之后必须保持稳定的最小时间,建立时间和保持时间对接收端的IC来说是个必须要满足的参数,否则采集就会出错或不成功,因为IC内部采集和处理数据的逻辑门和连线需要时间,否则触发器在数据还没有稳定的时候会有误触发。

2.发送端和接收端的时序,对于发送端来说,每个时钟周期都要发送数据,并且是时钟沿到来就启动发送,但对接收端来说,任何时钟沿采样的数据,都是发送端前一个时钟发送的数据,理解这一点是非常重要的。

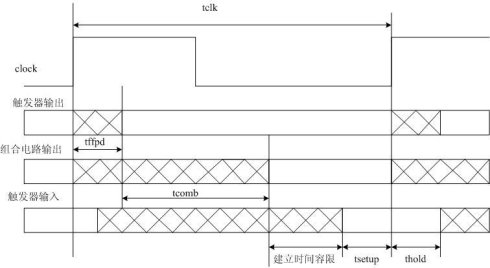

3.建立时间容限和保持时间容限,了解layout导线延时就必须理解建立时间容限和保持时间容限,因为满足建立时间容限和保持时间容限的的导线延时都是可以接受的,不会影响电路逻辑关系的,理解这些关系,参考下图理解:

上图为网上截取。

建立时间容限如图,保持时间容限为tffpd + tcomb - thold,上图上中间的表示的是输出端的时序,最后一个表示的是接收端的时序。

layout导线延时的容许范围就是:|data - clock| <= 建立时间容限与保持时间容限的最小值

具体以SDRAM为例子加以说明:

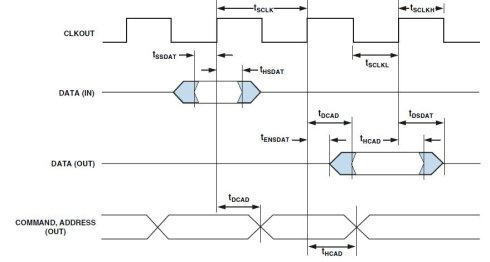

1.SDRAM的时序如下图

首先看,DATA(OUT) 图中tTENDAT = 0,即对发送端而言,时钟沿到达立即发送数据,tDSDAT = 4ns,说明数据正在发送时在时钟沿到后的4ns时发送的,即保持时间容限 = 4ns - 0.8ns(保持时间tSDAT),建立时间容限 = 7.5ns(tSCLK时钟周期) - 4ns(总线上有新的发送数据的真正时刻) - 1.5ns(tSSDAT建立时间) = 2ns

以6inch/ns的传播速度计算,数据线和时钟线的导线长度可以相差2*6=12inch,这是个非常大的容差范围,所以SDRAM根本无需做等长处理。

纯属个人理解,如有错误,还请网友不吝赐教!

posted on 2017-08-09 15:51 Red_Point 阅读(2266) 评论(0) 编辑 收藏 举报