Allegro Sigrity OptimizePI Training(一)去耦电容仿真设置

本文大纲

1. 去耦电容仿真设置(一)

2. 去耦电容仿真设置(二)

3. 去耦电容仿真设置(三)

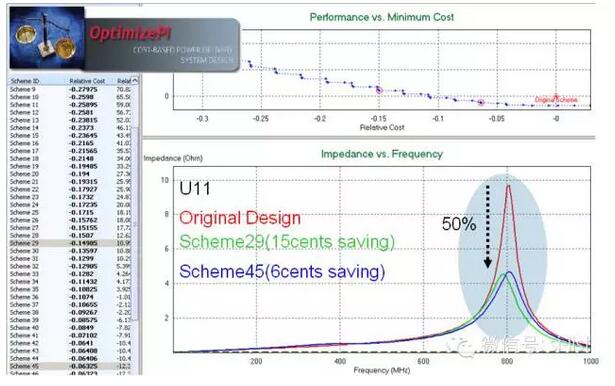

4.仿真优化结果查看

关于OptimizePI

去耦电容仿真设置(一)

1. 开始菜单->Cadence->Sigrity 2015->Sigrity Suite Manager。

2. 选择OptimizePI,在右边窗口选择可用的license双击启动OptimizePI。

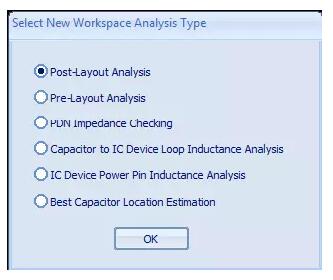

3. 在菜单栏选择Workspace->New,在弹出的窗口中,选择“Post-Layout Analysis”,点击OK确认。

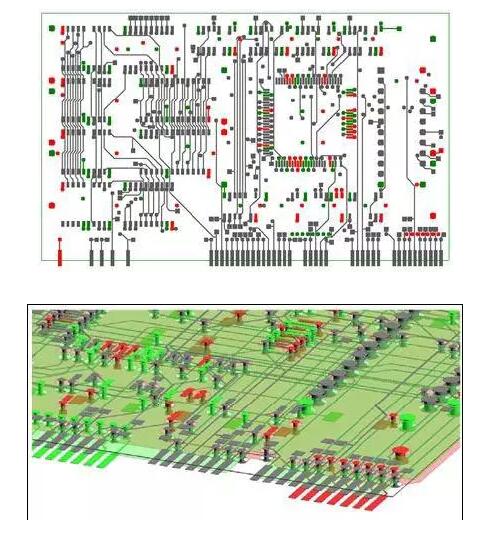

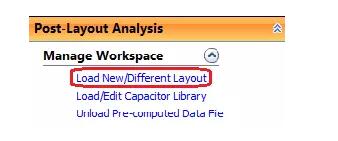

4. 在workflow中选择“Load New/Different Layout”,在弹出的对话框选择“Load an existing layout”,打开“D:\Training\Sigrity_OptimizePI\Lab\Module1\demo_OPI.spd”。

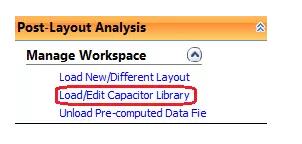

5. 在workflow中选择“Load/Edit Capacitor Library”

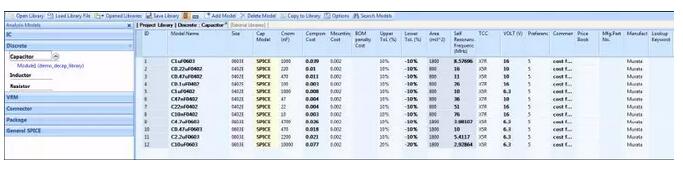

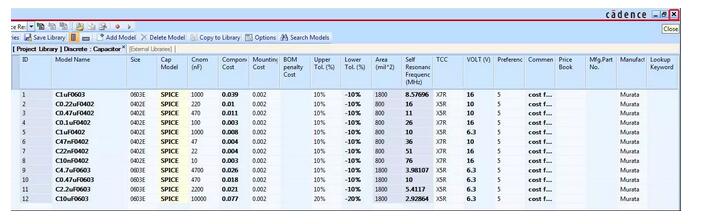

在弹出的Analysis Model Manager窗口,在Discrete-Capacitor位置,右键菜单选择“Load Library File”,打开“D:\Training\Sigrity_OptimizePI\Lab\Module1\demo_decap_library.xml”。

导入的电容库如下:

6. 点击Analysis Model Manager窗口右上角的 <ignore_js_op> 按键,关闭Analysis Model Manager窗口。

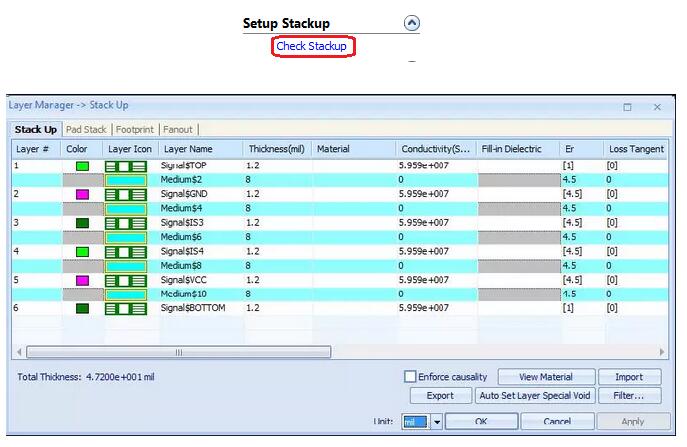

7. 在workflow中选择“Check Stackup”,打开Stack Up窗口。检查并设置金属层、介质层的厚度和材料参数。设置完成后点击OK按钮回到主界面。

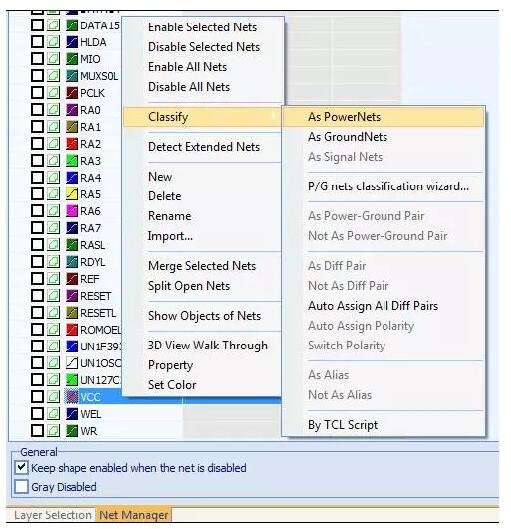

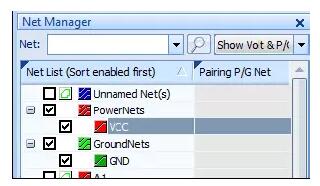

8. 在workflow中选择“Select Nets”。在Net Manager页面,选择VCC网络,右键菜单选择Classify->As PowerNets,然后使能VCC网络。

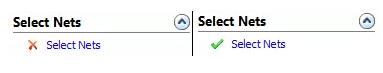

注意使能VCC网络后,Workflow的Select Nets前面的图标 <ignore_js_op> 会变成 <ignore_js_op>

。

-----本节完,共四章----

posted on 2019-03-02 17:02 Red_Point 阅读(3313) 评论(0) 编辑 收藏 举报