altera嵌入式乘法器

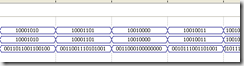

做FFT时,要对乘法器的输出进行截位。看altera器件handbook时,handbok给出了一个表:

这个表格说明只有两个输入信号都为无符号型的数据时,输出数据的数据类型才是无符号的。那该怎样截位呢?按理论,两个有符号数相乘,符号位有两个,符号相同的数相乘截位还好办,因为两个符号位是一样的,只去一个就可以了,若是两个符号不同的数相乘,也就是一个负数和一个正数相乘,其结果肯定是负的,但问题是两个符号位都是1吗?还是一个是1,一个是0.带着这个疑问,我对乘法器宏单元进行了仿真。仿真结构如下

从仿真结果可以看出,无论相乘的两个数符号是否相同,但输出结果两个符号位是一致的,两个正数或两个复数相乘,符号位为两个0,一个正、一个负输出结果符号位为两个1.截位的时候只保留一个符号位就可以了。对于有符号数的相乘,altera帮助文件里面是这样说的

从仿真结果也可以看出,对于有符号数的乘法,乘法器是将输入的数转换成二进制补码然后相乘的,但输出结果并不是以补码的形式输出的。就以00101011与10000001相乘为例:变成补码以后分别为00101011和11111111.数据位相乘得01010101010101,算出的结果为1101010101010101,但仿真出的结果为1110101010101011,正好为算出数据的补码,所以需要对算出的数据求补码才是正确的结果。