存储器结构、cache、DMA架构分析--【原创】

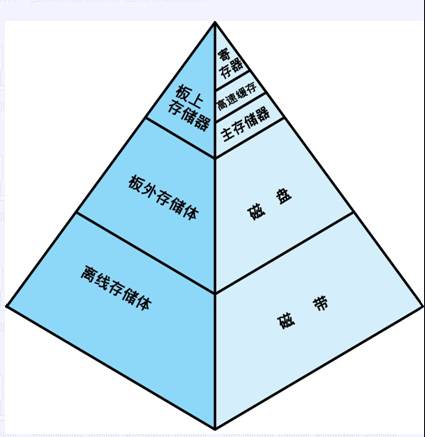

存储器的层次结构

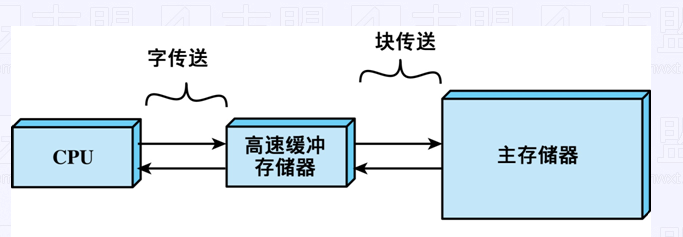

高速缓冲存储器 cache

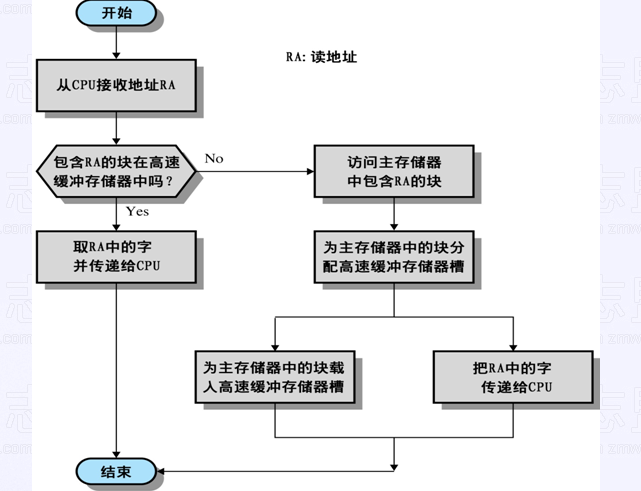

读cache操作

cache如果包含数据就直接从cache中读出来,因为cache速度要比内存快

如果没有包含的话,就从内存中找,找到后就放到cache中去,以后再读的话就直接从cache读了,下次访问很多次的时候就会快很多,相当于提高了命中率,cpu的访问速度就大大提高了

cache能大大提高cpu的访问速率

cache的设计

不能太大,也不能太小

太大的话,因为程序在查看数据的时候需要把cache走一遍,如果cache太大,

那么走一遍的时间就太长,就不能达到提升速率的效果

如果太小的话,存放在内存的块数就少了,命中率降低,访问内存的次数就增加了,cpu性能同样降低了

块大小

Cache与memory的的数据交换单位

由小变大时, 由局部性原理,命中增加

变得更大时, 新近取得数据被用到的可能性,小于那些必须被移出Cache的数据再次用到的可能性,命中率大大降低

DMA

大量移动数据

cpu性能快,外设的速度比较慢,cpu就要一直等待外设

因此诞生了DMA

以前没有DMA,就把数据从内存经过cpu到外设

有了DMA的话,cpu把指令告诉DMA,把内存从某个地址开始,多大的数据写给外设,这样的话DMA就去做了,cpu就不用做了,DMA就把内存中取出数据,然后再到外设,这种机制就是DMA机制,cpu就解放了,做更重要的事,因此这种内存拷贝、数据大量移动拷贝的时候就用DMA来解放cpu,记住cpu只在开始于结束时参与

开始时:

结束时:

中断处理例程

欢迎交流

新浪博客:http://blog.sina.com.cn/u/2049150530

csdn博客:http://blog.csdn.net/u011749143

博客园:http://www.cnblogs.com/sky-heaven/

chinaUnix: http://blog.chinaunix.net/uid/30049997.html

知乎:http://www.zhihu.com/people/zhang-bing-hua

【作者】sky

本文版权归作者和博客园共有,欢迎转载,但未经作者同意必须保留此段声明,且在文章页面明显位置给出原文连接,否则保留追究法律责任的权利.