(二)启动代码分析 02

首先从开发板硬件讲起:

思考问题: 开发板上电后,程序是如何启动呢???

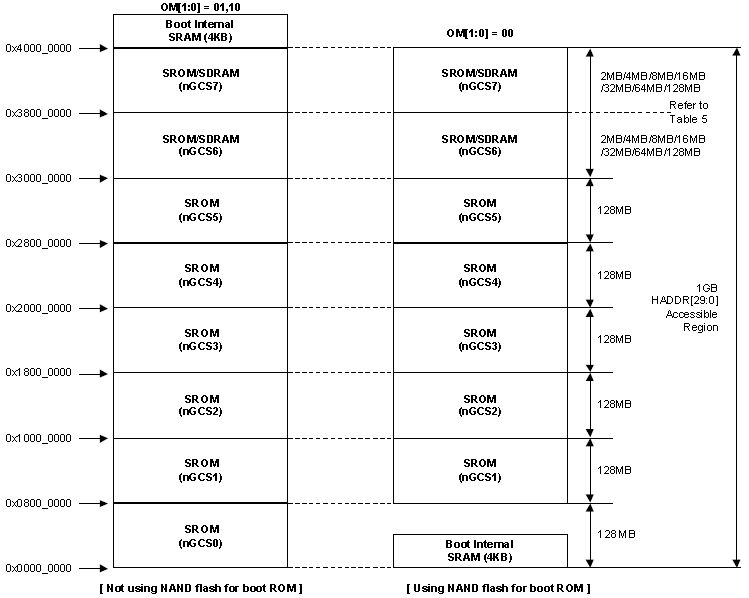

这里分 nor flash 启动 和 nand flash 启动

讲解 :

nand flash 启动:

______________________________________________________________________________________________________________________

由于NAND FLASH是接在NAND FLASH控制器上而不是系统总线上,所以没有在S3C2440A的8个BANK中分配地址空间。如果S3C2440被配置成从Nand Flash启动,在S3C2440上电后,Nand Flash控制器的会自动的把Nand Flash上的前4K数据搬移到内部SRAM中,也就是所谓的”Steppingstone”, 同时把这段片内SRAM映射到nGCS0片选的空间(即0x00000000)。系统会从这个内部SRAM中启动,程序员需要完成的工作,就是把最核心的启动程序放在Nand Flash的前4K中,也就是说,你需要编写一个长度小于4K的引导程序,作用是将主程序拷贝到RAM (一般是SDRAM)中运行。而在Nand Flash方式启动的情况下,系统是”看不到”Nor Flash的,因为Nor Flash也是挂在nGCS0上的,而nGCS0的地址空间已经被占用了。

________________________________________________________________________________________________________________________

1 GET option.inc 2 GET memcfg.inc 3 GET 2440addr.inc 4 5 ;Pre-defined constants 6 7 USERMODE EQU 0x10 8 FIQMODE EQU 0x11 9 IRQMODE EQU 0x12 10 SVCMODE EQU 0x13 11 ABORTMODE EQU 0x17 12 UNDEFMODE EQU 0x1b 13 MODEMASK EQU 0x1f 14 NOINT EQU 0xc0 15 16 ;The location of stacks 17 18 UserStack EQU (_STACK_BASEADDRESS-0x3800) ;0x33ff4800 ~ 19 SVCStack EQU (_STACK_BASEADDRESS-0x2800) ;0x33ff5800 ~ 20 UndefStack EQU (_STACK_BASEADDRESS-0x2400) ;0x33ff5c00 ~ 21 AbortStack EQU (_STACK_BASEADDRESS-0x2000) ;0x33ff6000 ~ 22 IRQStack EQU (_STACK_BASEADDRESS-0x1000) ;0x33ff7000 ~ 23 FIQStack EQU (_STACK_BASEADDRESS-0x0) ;0x33ff8000 ~ 24 25 26 27 MACRO 28 $HandlerLabel HANDLER $HandleAddr 29 30 $HandlerLabel 31 sub sp,sp,#4 ;decrement sp(to store jump address) 32 stmfd sp!,{r0} ;PUSH the work register to stack(lr does not push because it return to original address) 33 ldr r0,=$HandleAddr ;load the address of HandleXXX to r0 34 ldr r0,[r0] ;load the contents(service routine start address) of HandleXXX 35 str r0,[sp,#4] ;store the contents(ISR) of HandleXXX to stack 36 ldmfd sp!,{r0,pc} ;POP the work register and pc(jump to ISR) 37 MEND 38 39 40 IMPORT |Image$$RO$$Base| ; Base of ROM code 41 IMPORT |Image$$RO$$Limit| ; End of ROM code (=start of ROM data) 42 IMPORT |Image$$RW$$Base| ; Base of RAM to initialise 43 IMPORT |Image$$ZI$$Base| ; Base and limit of area 44 IMPORT |Image$$ZI$$Limit| ; to zero initialise 45 IMPORT Main ; The main entry of mon program 46 IMPORT RdNF2SDRAM ; Copy Image from Nand Flash to SDRAM 47 48 49 AREA Init,CODE,READONLY 50 ENTRY 51 ResetEntry 52 53 b ResetHandler 54 b HandlerUndef ;handler for Undefined mode 55 b HandlerSWI ;handler for SWI interrupt 56 b HandlerPabort ;handler for PAbort 57 b HandlerDabort ;handler for DAbort 58 b . ;reserved 59 b HandlerIRQ ;handler for IRQ interrupt 60 b HandlerFIQ ;handler for FIQ interrupt 61 62 63 HandlerFIQ HANDLER HandleFIQ 64 HandlerIRQ HANDLER HandleIRQ 65 HandlerUndef HANDLER HandleUndef 66 HandlerSWI HANDLER HandleSWI 67 HandlerDabort HANDLER HandleDabort 68 HandlerPabort HANDLER HandlePabort 69 70 IsrIRQ 71 sub sp,sp,#4 ;reserved for PC 72 stmfd sp!,{r8-r9} 73 74 ldr r9,=INTOFFSET 75 ldr r9,[r9] 76 ldr r8,=HandleEINT0 77 add r8,r8,r9,lsl #2 78 ldr r8,[r8] 79 str r8,[sp,#8] 80 ldmfd sp!,{r8-r9,pc} 81 82 LTORG 83 84 85 ResetHandler 86 87 ldr r0,=WTCON ;watch dog disable 88 ldr r1,=0x0 89 str r1,[r0] 90 91 ldr r0,=INTMSK 92 ldr r1,=0xffffffff ;all interrupt disable 93 str r1,[r0] 94 95 ldr r0,=INTSUBMSK 96 ldr r1,=0x7fff ;all sub interrupt disable 97 str r1,[r0] 98 99 ;To reduce PLL lock time, adjust the LOCKTIME register. 100 ldr r0,=LOCKTIME 101 ldr r1,=0xffffff 102 str r1,[r0] 103 104 ldr r0,=CLKDIVN 105 ldr r1,=CLKDIV_VAL ; 0=1:1:1, 1=1:1:2, 2=1:2:2, 3=1:2:4, 4=1:4:4, 5=1:4:8, 6=1:3:3, 7=1:3:6. 106 str r1,[r0] 107 108 ;CLKDIV_VAL>1 means Fclk:Hclk is not 1:1. 109 [ CLKDIV_VAL>1 ; means Fclk:Hclk is not 1:1. 110 mrc p15,0,r0,c1,c0,0 111 orr r0,r0,#0xc0000000;R1_nF:OR:R1_iA 112 mcr p15,0,r0,c1,c0,0 113 | 114 mrc p15,0,r0,c1,c0,0 115 bic r0,r0,#0xc0000000;R1_iA:OR:R1_nF 116 mcr p15,0,r0,c1,c0,0 117 ] 118 ;Configure UPLL 119 ldr r0,=UPLLCON 120 ldr r1,=((U_MDIV<<12)+(U_PDIV<<4)+U_SDIV) ;Fin = 12.0MHz, UCLK = 48MHz 121 str r1,[r0] 122 nop ; at least 7-clocks delay must be inserted for setting hardware be completed. 123 nop 124 nop 125 nop 126 nop 127 nop 128 nop 129 ;Configure MPLL 130 ldr r0,=MPLLCON 131 ldr r1,=((M_MDIV<<12)+(M_PDIV<<4)+M_SDIV) ;Fin = 12.0MHz, FCLK = 200MHz 132 str r1,[r0] 133 134 ;Set memory control registers 135 136 adrl r0, SMRDATA ;be careful! 137 ldmia r0,{r1-r13} 138 ldr r0,=BWSCON 139 stmia r0,{r1-r13} 140 141 bl InitStacks 142 143 ;=========================================================== 144 145 ldr r0, =BWSCON 146 ldr r0, [r0] 147 ands r0, r0, #6 ;OM[1:0] != 0, NOR FLash boot 148 bne copy_proc_beg ;do not read nand flash 149 adr r0, ResetEntry ;OM[1:0] == 0, NAND FLash boot 150 cmp r0, #0 ;if use Multi-ice, 151 bne copy_proc_beg ;do not read nand flash for boot 152 ;nop 153 ;=========================================================== 154 nand_boot_beg 155 156 bl RdNF2SDRAM 157 158 ldr pc, =copy_proc_beg 159 ;=========================================================== 160 copy_proc_beg 161 adr r0, ResetEntry 162 ldr r2, BaseOfROM 163 cmp r0, r2 164 ldreq r0, TopOfROM 165 beq InitRam 166 ldr r3, TopOfROM 167 0 168 ldmia r0!, {r4-r7} 169 stmia r2!, {r4-r7} 170 cmp r2, r3 171 bcc %B0 172 173 sub r2, r2, r3 174 sub r0, r0, r2 175 176 InitRam 177 ldr r2, BaseOfBSS 178 ldr r3, BaseOfZero 179 0 180 cmp r2, r3 181 ldrcc r1, [r0], #4 182 strcc r1, [r2], #4 183 bcc %B0 184 185 mov r0, #0 186 ldr r3, EndOfBSS 187 1 188 cmp r2, r3 189 strcc r0, [r2], #4 190 bcc %B1 191 192 193 ;=========================================================== 194 ; Setup IRQ handler 195 196 197 ldr r0,=HandleIRQ ;This routine is needed 198 ldr r1,=IsrIRQ ;if there is not 'subs pc,lr,#4' at 0x18, 0x1c 199 str r1,[r0] 200 201 b Main ;Do not use main() because ...... 202 203 InitStacks 204 mrs r0,cpsr 205 bic r0,r0,#MODEMASK 206 orr r1,r0,#UNDEFMODE|NOINT 207 msr cpsr_cxsf,r1 ;UndefMode 208 ldr sp,=UndefStack ; UndefStack=0x33FF_5C00 209 210 orr r1,r0,#ABORTMODE|NOINT 211 msr cpsr_cxsf,r1 ;AbortMode 212 ldr sp,=AbortStack ; AbortStack=0x33FF_6000 213 214 orr r1,r0,#IRQMODE|NOINT 215 msr cpsr_cxsf,r1 ;IRQMode 216 ldr sp,=IRQStack ; IRQStack=0x33FF_7000 217 218 orr r1,r0,#FIQMODE|NOINT 219 msr cpsr_cxsf,r1 ;FIQMode 220 ldr sp,=FIQStack ; FIQStack=0x33FF_8000 221 222 bic r0,r0,#MODEMASK|NOINT 223 orr r1,r0,#SVCMODE 224 msr cpsr_cxsf,r1 ;SVCMode 225 ldr sp,=SVCStack ; SVCStack=0x33FF_5800 226 227 ;USER mode has not be initialized. 228 229 mov pc,lr 230 ;The LR register will not be valid if the current mode is not SVC mode. 231 232 LTORG 233 234 SMRDATA 235 DCD 0x22011000 236 DCD 0x00000700 ;GCS0 237 DCD 0x00000700 ;GCS1 238 DCD 0x00000700 ;GCS2 239 DCD 0x00000700 ;GCS3 240 DCD 0x00000700 ;GCS4 241 DCD 0x00000700 ;GCS5 242 DCD ((B6_MT<<15)+(B6_Trcd<<2)+(B6_SCAN)) ;GCS6 243 DCD ((B7_MT<<15)+(B7_Trcd<<2)+(B7_SCAN)) ;GCS7 244 DCD ((REFEN<<23)+(TREFMD<<22)+(Trp<<20)+(Tsrc<<18)+REFCNT) 245 246 ;DCD 0x32 ;SCLK power saving mode, BANKSIZE 64M/64M 247 DCD 0xB1 248 DCD 0x30 ;MRSR6 CL=3clk 249 DCD 0x30 ;MRSR7 CL=3clk 250 251 BaseOfROM DCD |Image$$RO$$Base| 252 TopOfROM DCD |Image$$RO$$Limit| 253 BaseOfBSS DCD |Image$$RW$$Base| 254 BaseOfZero DCD |Image$$ZI$$Base| 255 EndOfBSS DCD |Image$$ZI$$Limit| 256 257 ALIGN 258 259 AREA RamData, DATA, READWRITE 260 261 ^ _ISR_STARTADDRESS ; _ISR_STARTADDRESS=0x33FF_FF00 262 HandleReset # 4 263 HandleUndef # 4 264 HandleSWI # 4 265 HandlePabort # 4 266 HandleDabort # 4 267 HandleReserved # 4 268 HandleIRQ # 4 269 HandleFIQ # 4 270 271 272 ;IntVectorTable ;@0x33FF_FF20 273 HandleEINT0 # 4 274 HandleEINT1 # 4 275 HandleEINT2 # 4 276 HandleEINT3 # 4 277 HandleEINT4_7 # 4 278 HandleEINT8_23 # 4 279 HandleCAM # 4 280 HandleBATFLT # 4 281 HandleTICK # 4 282 HandleWDT # 4 283 HandleTIMER0 # 4 284 HandleTIMER1 # 4 285 HandleTIMER2 # 4 286 HandleTIMER3 # 4 287 HandleTIMER4 # 4 288 HandleUART2 # 4 289 ;@0x33FF_FF60 290 HandleLCD # 4 291 HandleDMA0 # 4 292 HandleDMA1 # 4 293 HandleDMA2 # 4 294 HandleDMA3 # 4 295 HandleMMC # 4 296 HandleSPI0 # 4 297 HandleUART1 # 4 298 HandleNFCON # 4 299 HandleUSBD # 4 300 HandleUSBH # 4 301 HandleIIC # 4 302 HandleUART0 # 4 303 HandleSPI1 # 4 304 HandleRTC # 4 305 HandleADC # 4 306 ;@0x33FF_FFA0 307 END

该初始代码来自书籍:ARM 处理器 裸机开发实战 ---机制而非策略