lattice_ddr3调试经验分享(一)建立工程与仿真

一,仿真

依据 DoubleDataRateDDR3SDRAMControllerIPCoreUsersGuide设定自己需要的DDR,不过lattice支持的ddr实在是太少了,所以就选择customer。

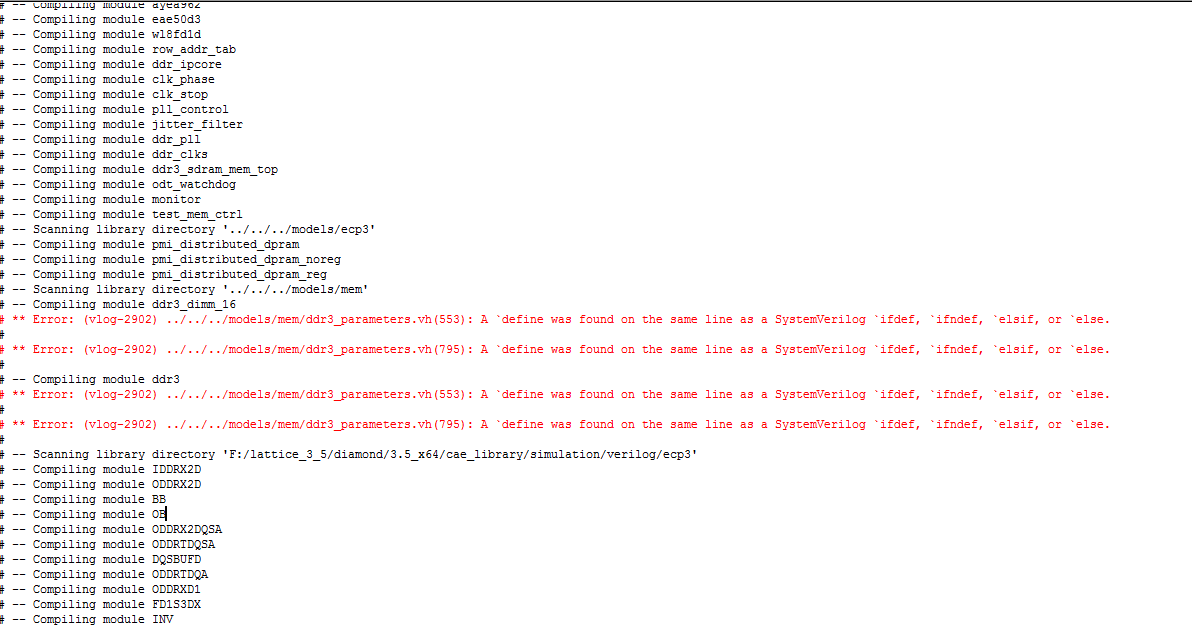

仿真的时候,和MIG类似,选定工作目录在sim/modelsim/目录下。

再 tool -->tcl -->execute macro 执行do文件 ddr_ipcore_eval.do 。这个ddr_ipcore 是我自己取的IP核的名称

在10.2c的modelsim下会报error,网上有人说在10.1下可以顺利通过,没有试过。因为我只有10.2c的modelsim

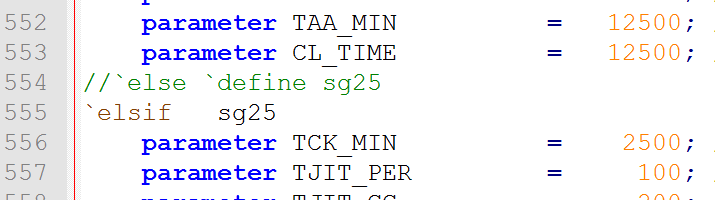

大概的意思是说,那两行它认为是SV的的代码风格。好吧。改成verilog的

这么改是不是等效的,我没有具体去查。 对于795行也是这么改。

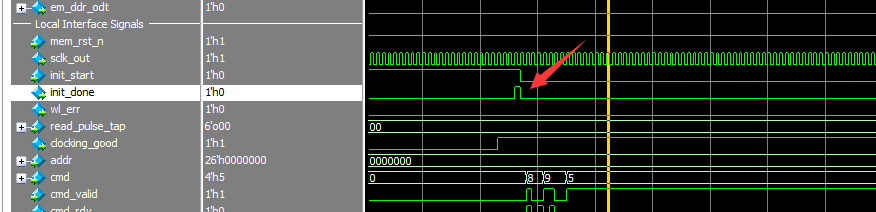

在do一下,波形图漂亮!

lattice 的ddr3初始化成功后,不是和MIG 一样一直拉高,而是只给出一个高脉冲。

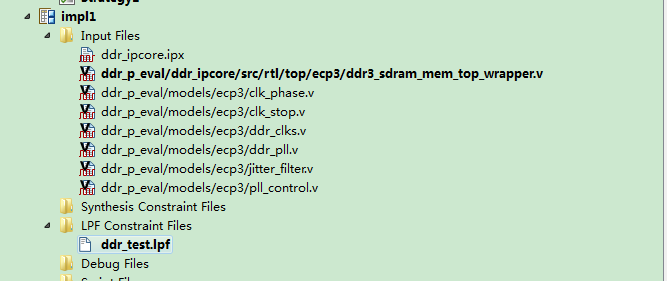

二:可综合文件添加

上述的步骤只是在工程中有了一个ddr_ipcore.ipx的文件。还需要加入 ddr3_sdram_mem_top_wrapper.v 这个才是可综合的顶层。 这个顶层还包含了一些pll的模块,所以还需要加入

clk_phase.v

clk_stop.v

ddr_clks.v

ddr_pll.v

jitter_filter.v

pll_control.v

结果如图

这么多就完了?不是,还有一步

三:约束

在IP 核生成的综合文件夹下有一个lpf文件。把这个文件中的约束复制到自己的lpf文件中即可。

注意我这个地方是把IP自动生成的top当top,所以这个约束就不用改了,如果你有自己的top,那个这个约束中牵涉到器件位置的约束语句就需要修改位置了。

这种偷懒方法,我相信大家都喜欢的。哈哈

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884

浙公网安备 33010602011771号

浙公网安备 33010602011771号