verilog中连续性赋值中的延时

上次遇到一个问题。写一个testbench需要移动两个时钟之间的相位。后来一想,貌似我们都是这么写clock的

always #(`P/2) clk = ~clk

我的两个时钟都是这么写,只是p不一样,那相位怎么移动呢?

于是就追究起 如何延迟赋值的问题

根据standard-2005.

对于连续赋值延时只有这一种

wire #delay_time b ;

assign a = b ;

1,在第0时刻仿真器读取b的值

2,如果b的值,与a不同,取消上一个event, 新建立event ----- 过delay_time后,将新值赋值给 a

3, 如果b值与a相同,那么维持现状

4,在这delay_time时间内,如果b继续变化。回到2或者3.

用真OO无双大神的话说,就是无code无真相

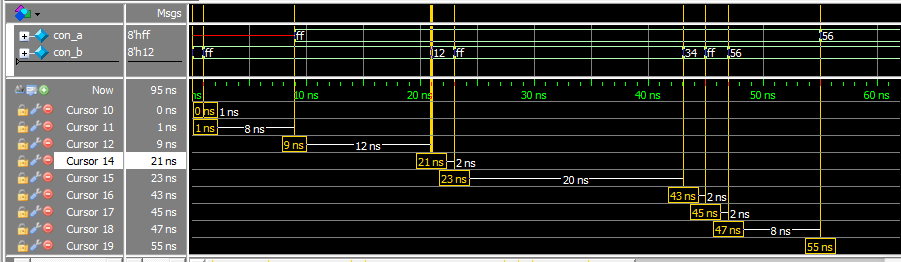

1 module delay_test ; 2 //Continuous assignments check 3 wire [7:0] #8 con_a ; 4 reg [7:0] con_b ; 5 assign con_a = con_b ; 6 //********************** 7 initial begin 8 con_b = 0 ; 9 #1 10 con_b = 8'hff ; 11 #20 12 13 con_b = 8'h12 ; 14 #2 15 con_b = 8'hff ; 16 #20 17 18 con_b = 8'h34 ; 19 #2 20 con_b = 8'hff ; 21 #2 22 con_b = 8'h56 ; 23 #20 ; 24 end 25 endmodule

测试两个回合

先初始化a=b=ff

第一回合发生在第21ns的时刻, b=12维持了2ns (<delay_time 8ns),在第23ns时刻变成了ff。发现经过20ns(>delay_time 8ns)a的值一直是ff。

第二回合发生在第43ns时刻, b=34维持2ns,再b=ff维持2ns,再b=56(在第47ns)维持2ns。结果在第56ns (56-47=8)a=56

有code有图有真相。

所以对于我的问题可以是

wire #Delay_time clk2 assign clk2 = clk1

这样就把clk1的相位移动了一下,形成了一个新的时钟clk2

其实还可以是用forever。效果是一样的

1 initial begin 2 #Delay_time 3 forever #(`P/2) clk2 = ~clk2 ; 4 end

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884