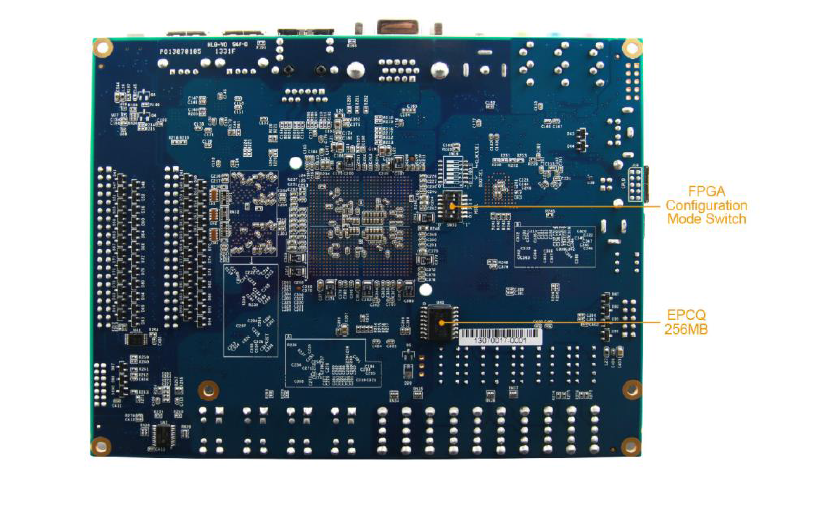

首先看一下友晶DE-SOC开发板的user manual

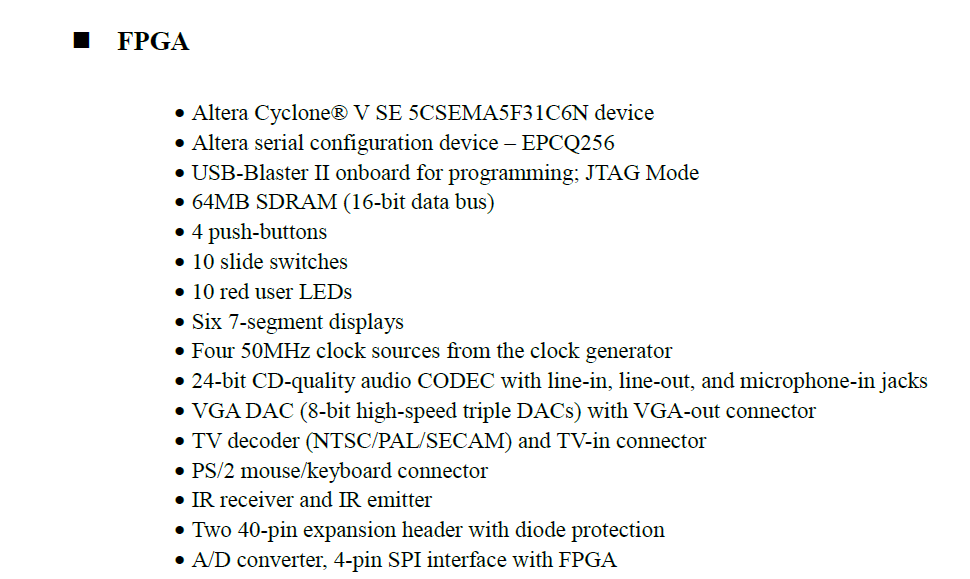

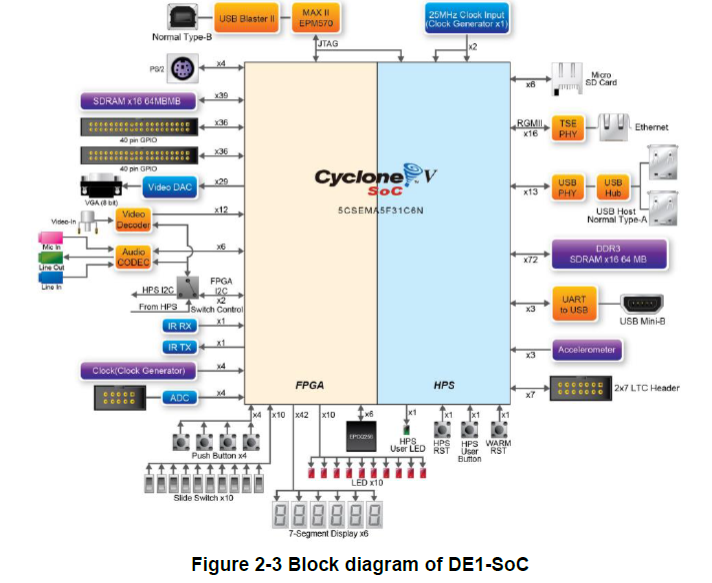

对于友晶DE-SOC系列开发板来说,由于其内部自带ARM 的cortex-A9硬核,所以使用nios II开发来说其实是不划算的,但是这里重点是为了学习NIOS II的开发,所以对于用DS-5来开发ARM-FPGA的开发,等将整套系统玩透后再来一一进行记录,下面是DE-SOC开发板提供的系统外设:

对于FPGA部分的开发结构如下所示

对于HPS部分的硬件结构如下所示

整个系统的结构图:

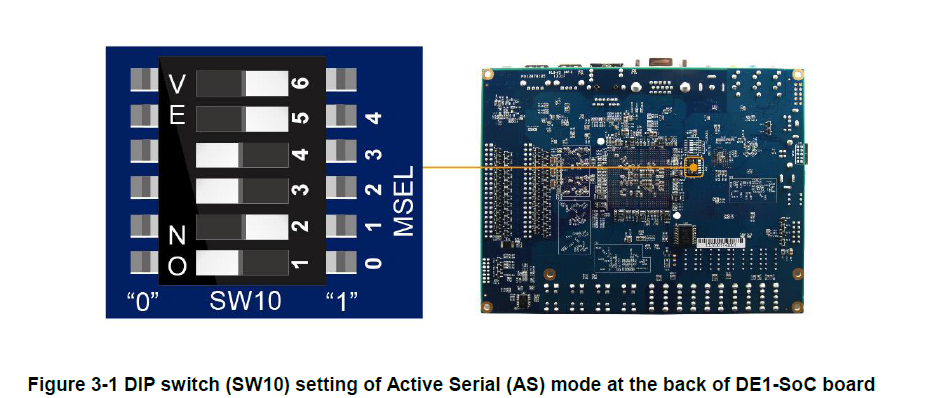

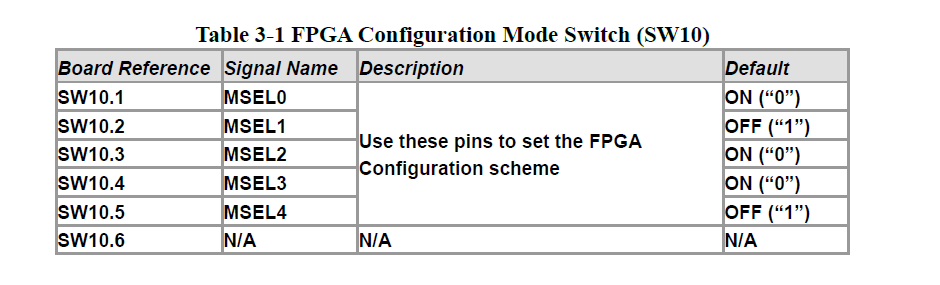

对于开发板,可以通过背面的拨码开关来更改开发模式

引脚与对应的模式选项,这里选用FPGA开发故拨码开关拨到01001进行开发,即系统检测模式,拨到此模式,打开开发板,开发板数码管会从0~F跳动,led灯会有规律的跳动,接上VGA,液晶显示器上回跳出DE-SOC的图片,接上喇叭,按KEY1,回有滴的一声响。

下面是JTAG的路径链

HPS的复位机构数

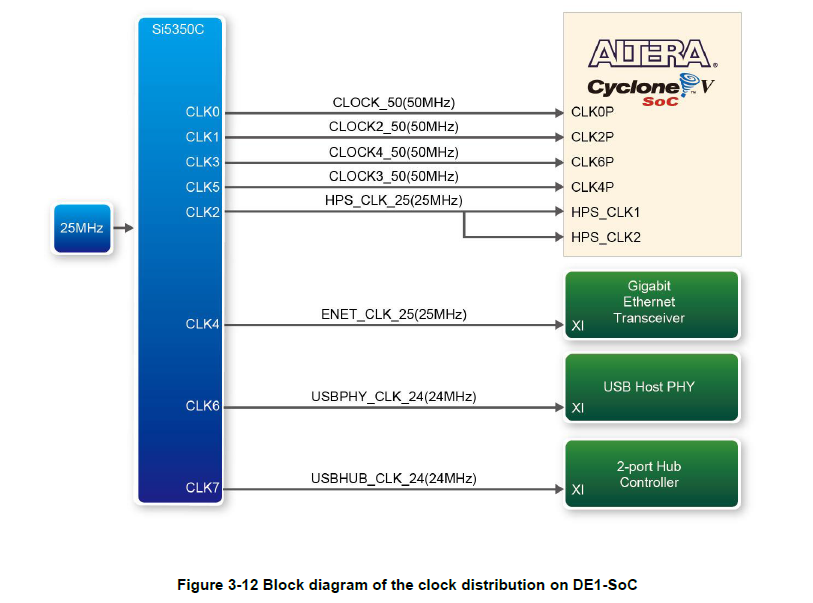

DE-SOC的时钟分配

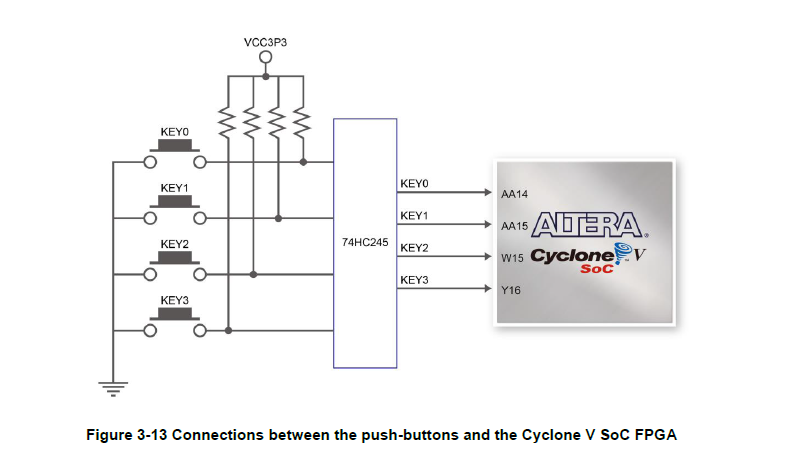

按键电路图

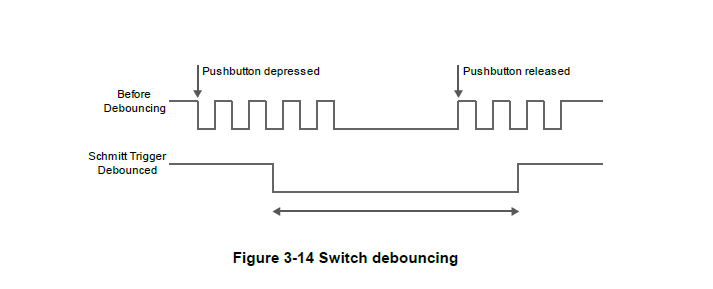

开发板自带施密特触发器去抖动,对按键进行了硬件消抖:

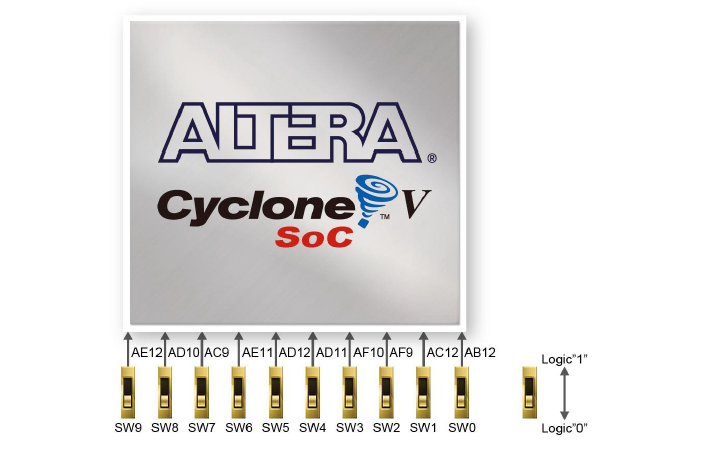

拨码开关的拨动逻辑

LED的电路图,可知IO口为高电平的时候,LED灯亮

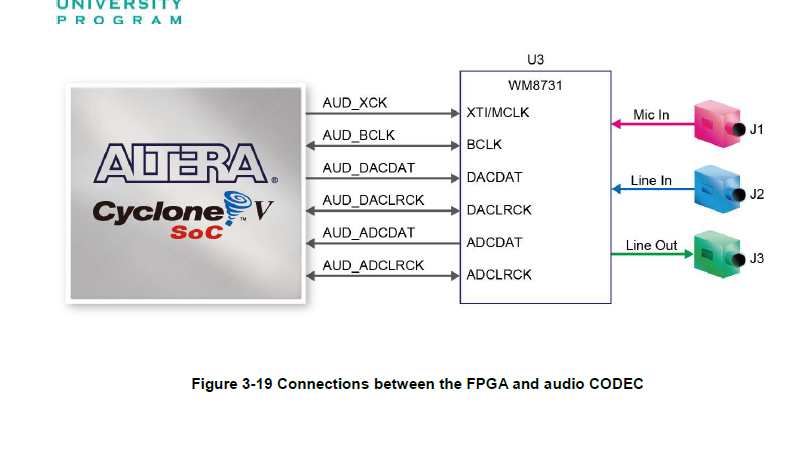

audio 解码电路的连接

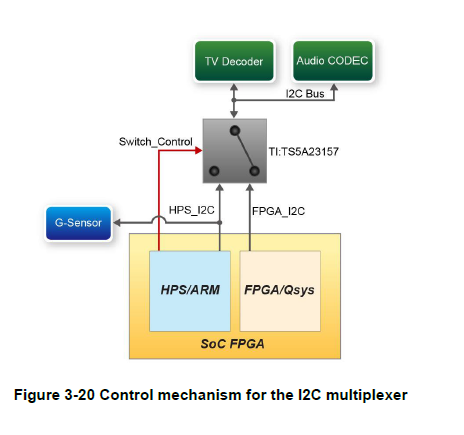

I2C通讯的器件,可以看出默认是由FPGA控制的,HPS也可以通过

将HPS的I2C控制信号置高来对audio codec和TV decoder进行访问。

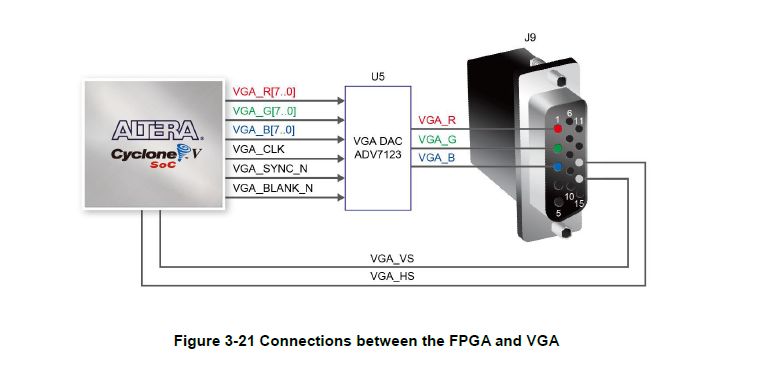

VGA接口电路模拟图

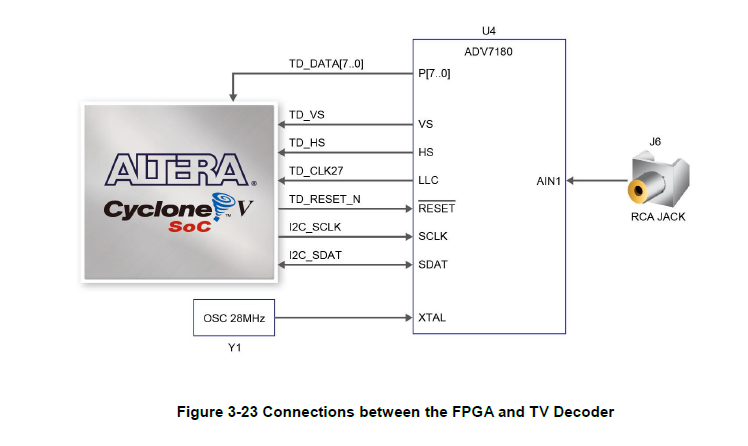

TVdecoder的接口电路

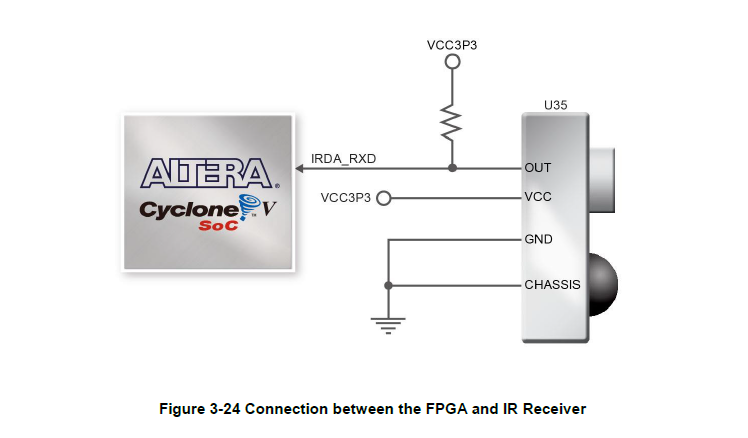

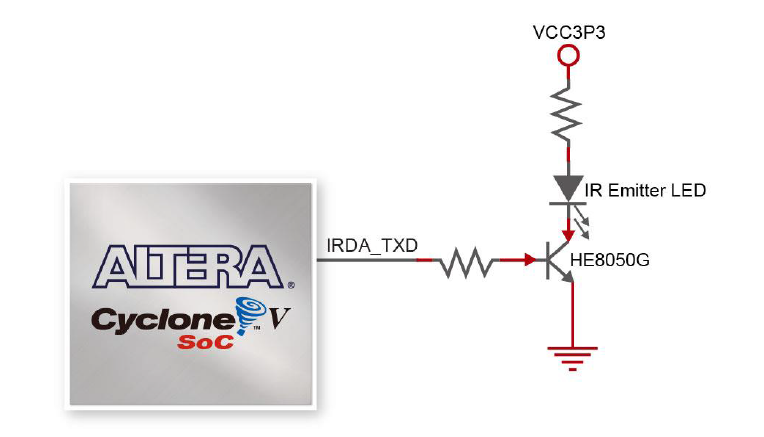

红外接收电路 红外发射电路

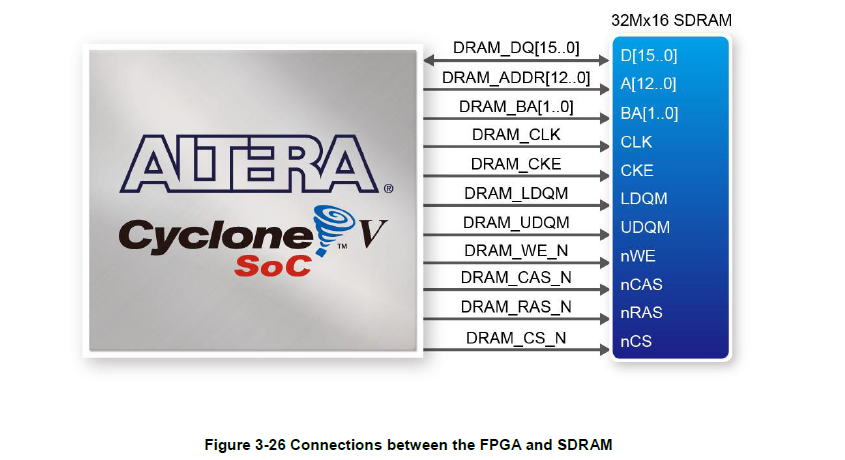

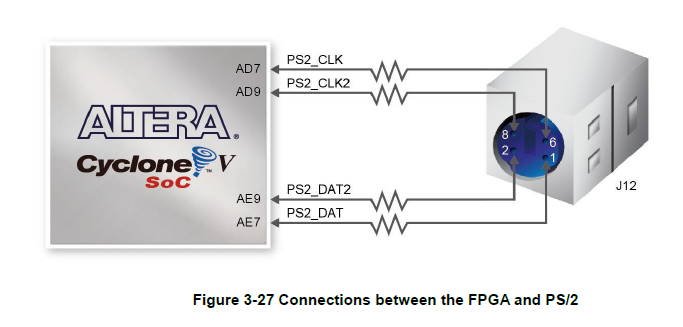

SDRAM连接电路 PS接口电路

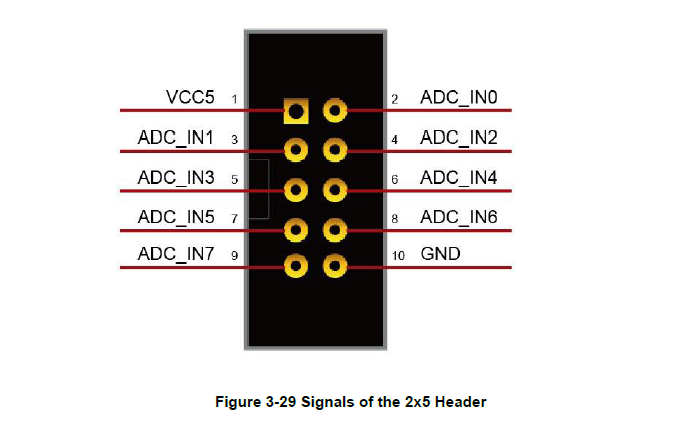

ADC接口和ADC与FPGA的连接电路

从此处往后都是HPS接口电路

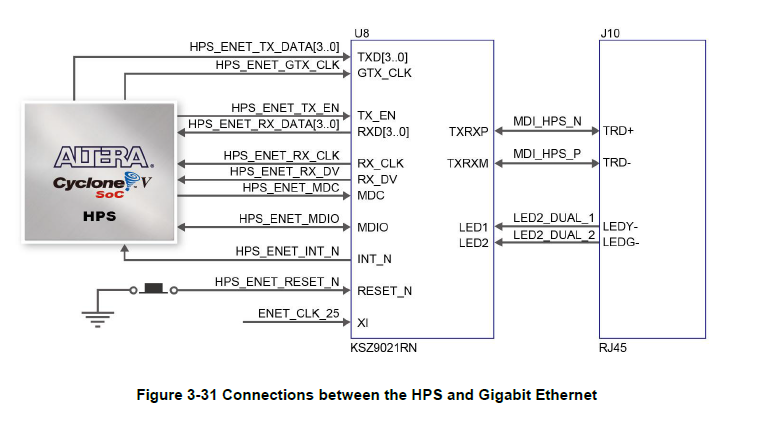

千兆bit网接口; uart 转USB接口电路

microSD卡连接电路

2个USB接口与FPGA的连接

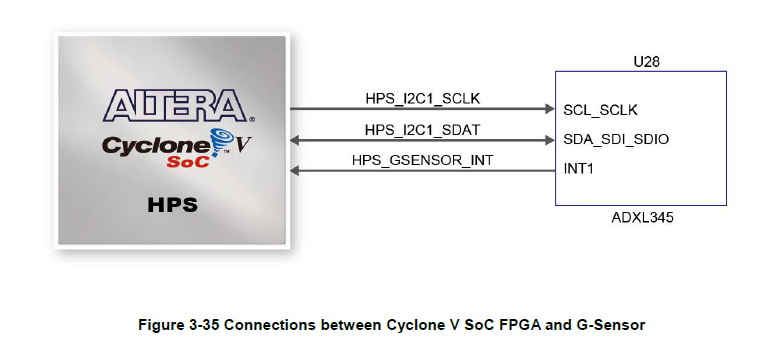

加速度传感器

LTC开关器件的连接电路

本文所有内容都取自Altera的官方DE1-SoC_User_manual.pdf文档,文档中还有相应电路对应的接口对应的GPIO。