Vivado级联Modelsim仿真Re-launch问题

前两天在群里看到有朋友说Vivado级联Modelsim仿真出现修改设计代码后重新run do文件,波形没有随着代码修改而改变,这个问题博主之前没有注意到,因为把Vivado和Modelsim级联好后还没有试过仿真过,不过用ISE级联好后,修改设计代码,可以直接重新run do文件进行仿真,不必关闭Modelsim。

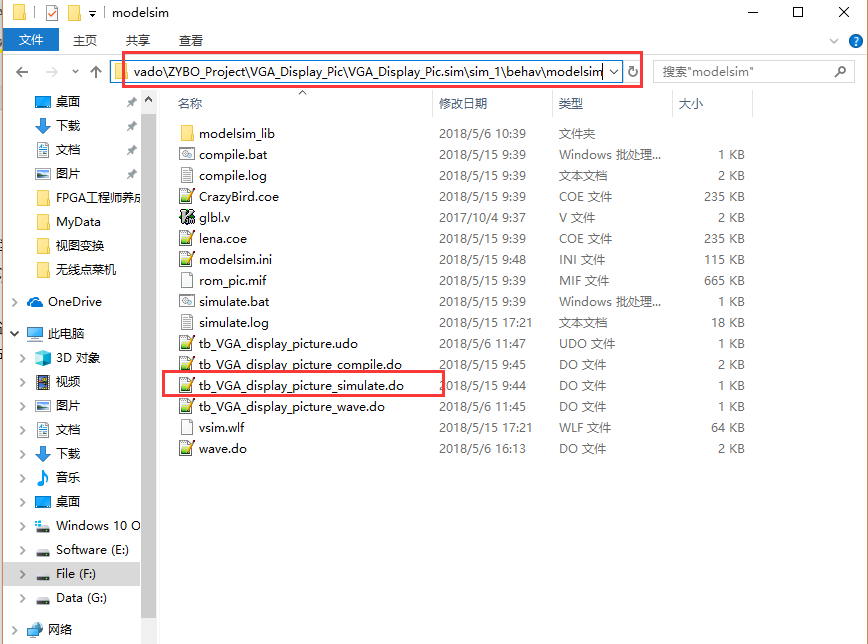

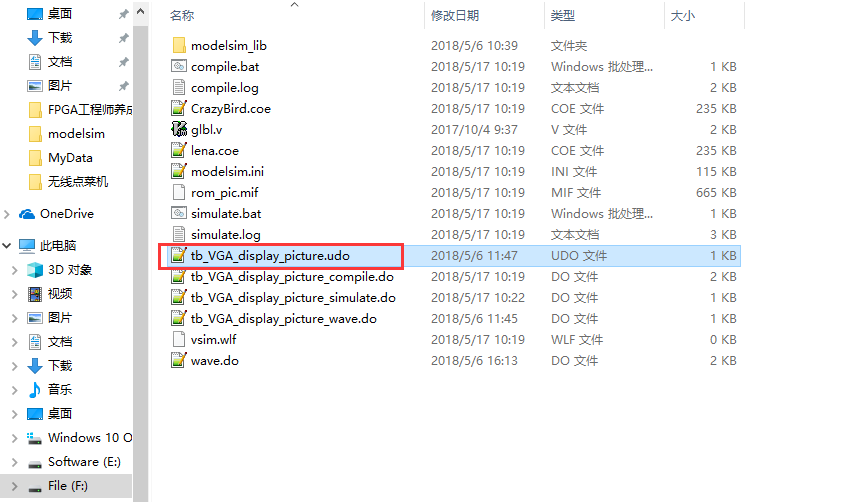

对于这个问题博主打开Vivado工程目录下生成的do文件看了下。

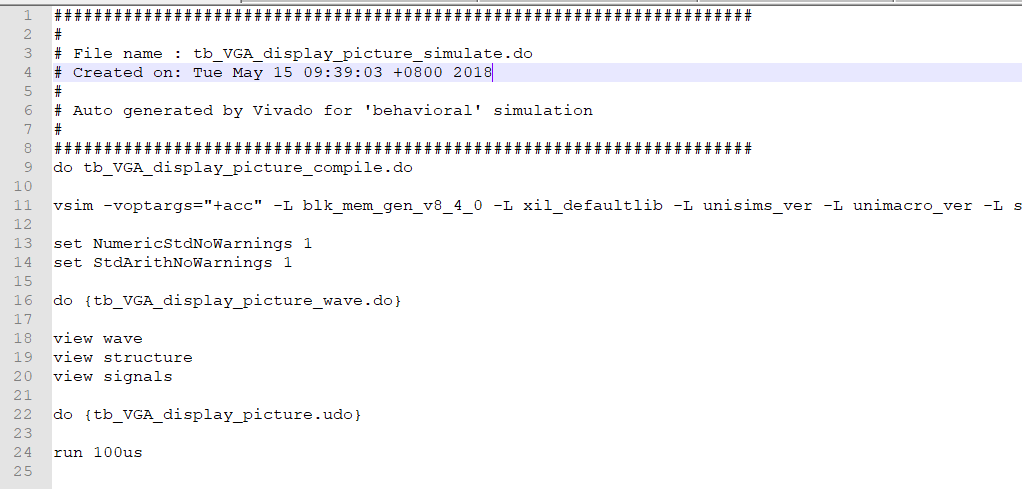

我们需要run的是这个xxx_simulate.do文件,打开看下里面内容。

发现这里面没有,编译库和编译文件的脚本,所以我们修改设计代码后重新run do文件之后,波形是没有变化。这个问题现在可以解决的。

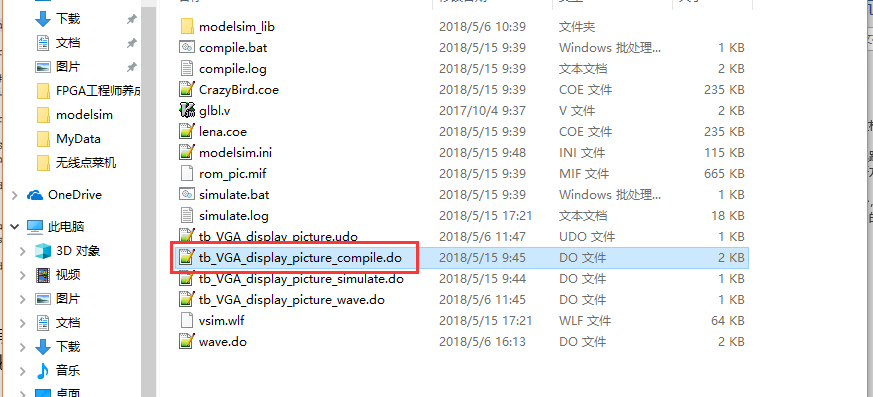

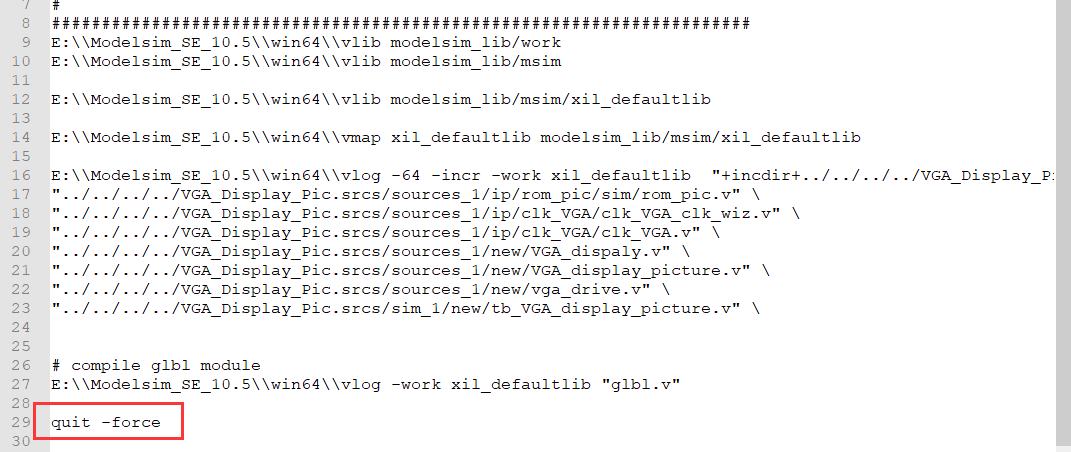

在这里目录下还有一个文件,是xxx_compile.do文件,打开看看。

原来编译的语句都在这里,注意这里的quit –force,这句会直接强制关闭Modelsim,所以如果你直接运行这个文件,Modelsim会直接退出,所以这行去掉。

然后回到xxx_simulate.do,在这个位置添加一句do xxx_compile.do,这样修改后,每次run do文件,就会编译你工程里面的修改的设计文件了。不过这里需要注意,当你关闭Modelsim后,重新再Vivado中启动Modelsim仿真,上面说的这两个文件会重新加载,所以要重新修改。不过里面得xxx.udo会保留。开发者可以根据自己的需求在里面添加相应的TCL脚本,方便仿真。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan