Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器。在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还是有一些不方便,所以我便直接使用Modelsim独立仿真,但是对于IP Core的话,就需要添加Vivado IP Core的库文件,本人查阅了很多资料,最终实现了使用Modelsim仿真Vivado Clocking Wizard IP Core,软件版本,Vivado 2017.3、Modelsim SE10.4。具体流程如下,实测记录。

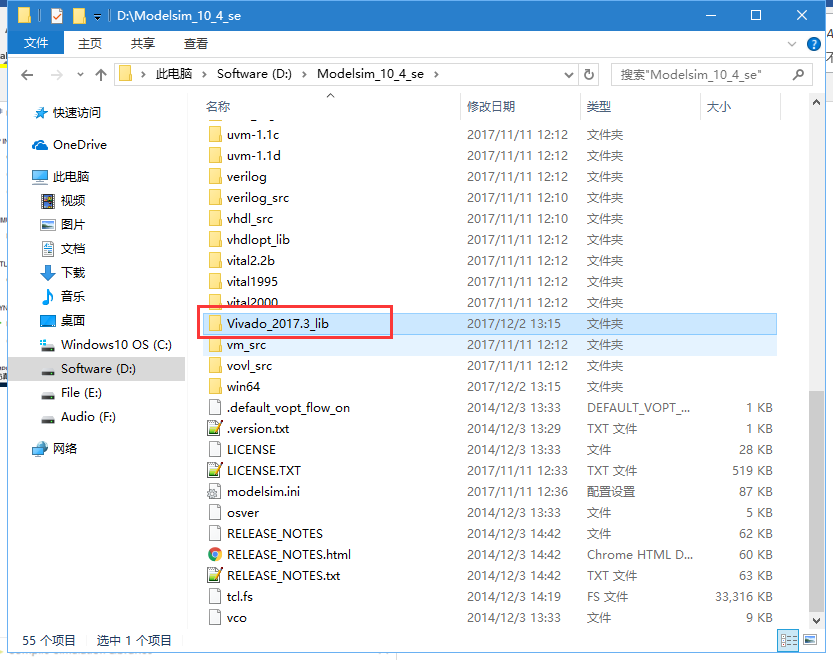

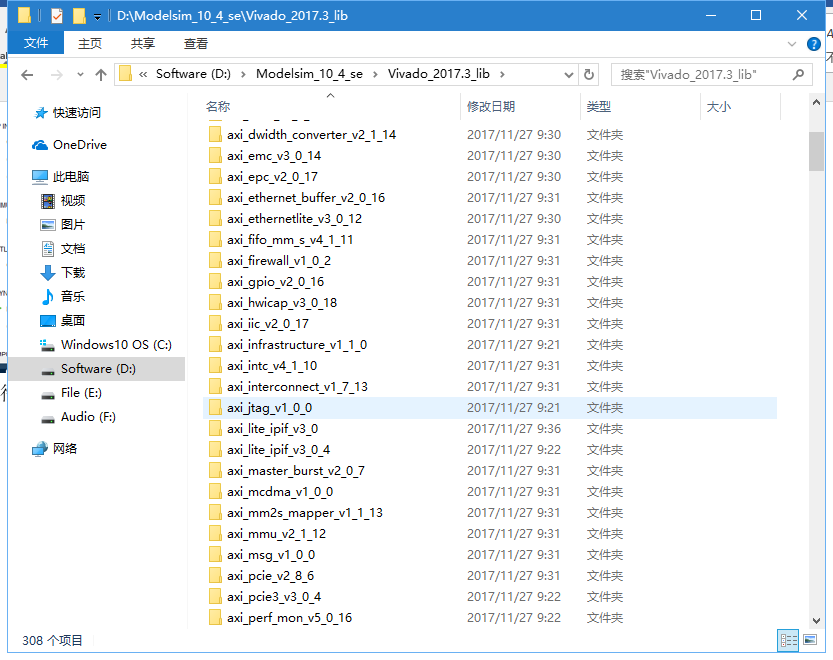

首先,在 Modelsim 的安装目录下新建一个文件夹,我这里是D:\Modelsim_10_4_se\Vivado_2017.3_lib

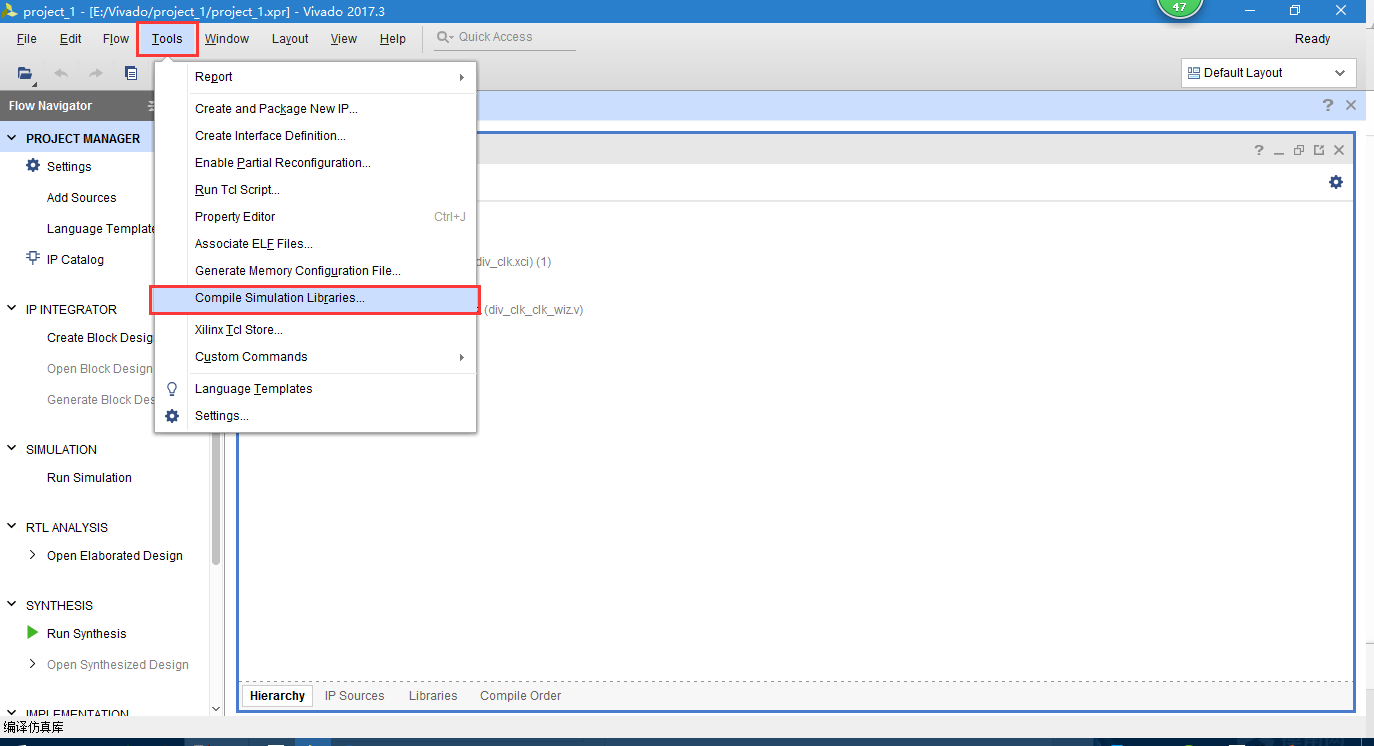

然后,打开Vivado软件,主界面菜单栏点击Tools下的Compile Simulation Libraries编译Vivado仿真库

弹出如下窗口然后按如图所示选择,1处路径为刚才我们新建的文件夹中,2处为Modelsim的运行程序路径。设置好后点击compile。

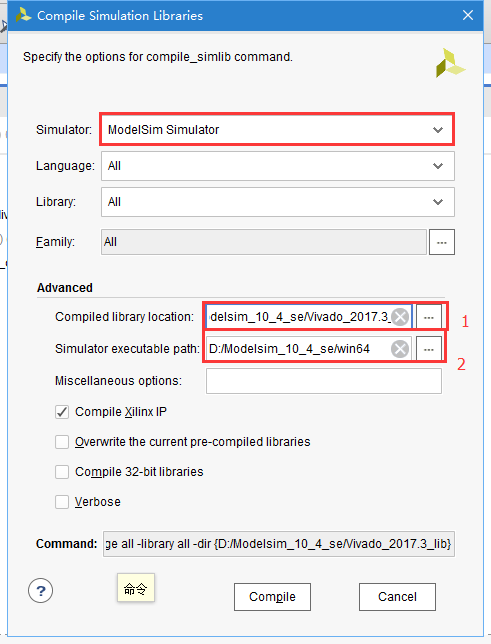

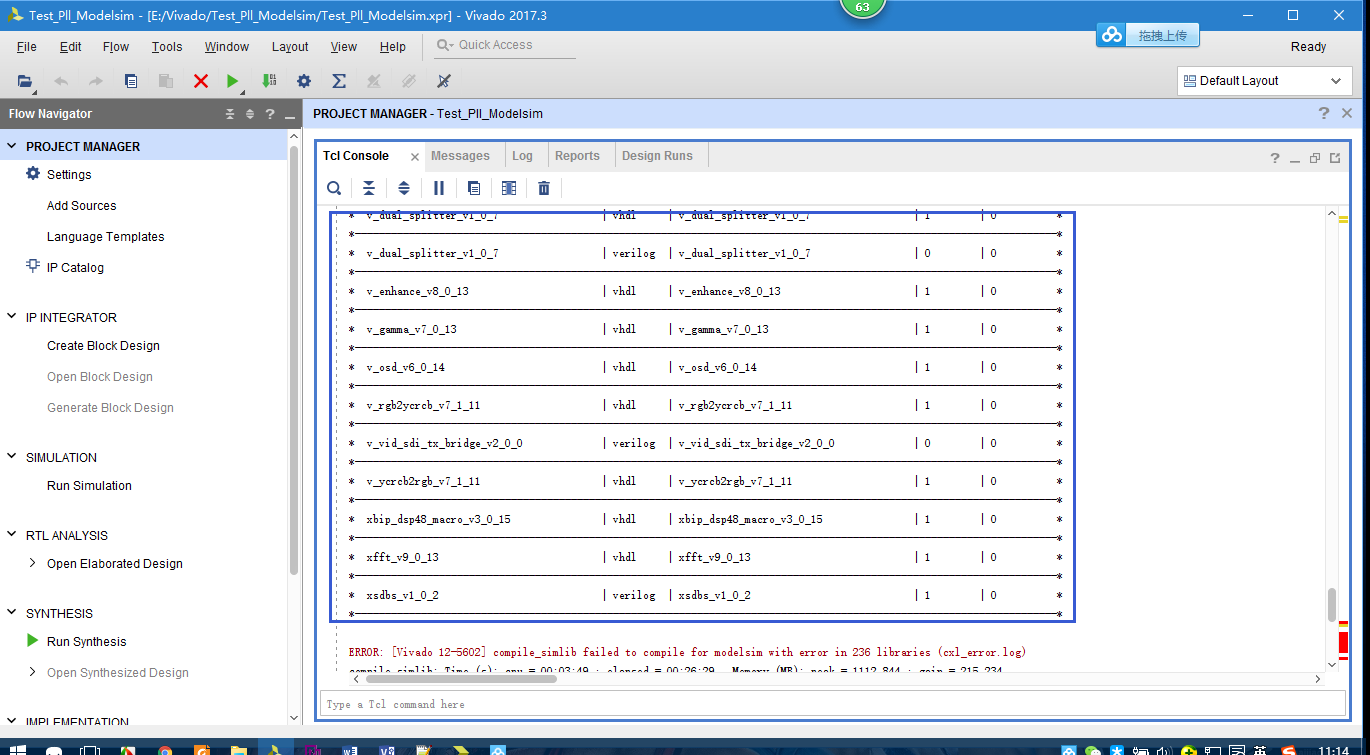

在编译的过程中窗口会打印出来如下信息。

等待一段时间,Vivado的库文件编译完成后我们可以看到文件夹下都是Vivado的库文件

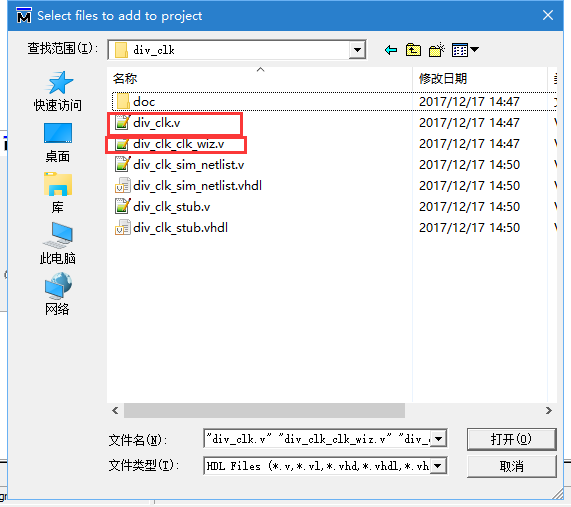

然后使用Vivado新建一个调用的Clocking Wized IP Core的工程,编写好测试文件,然后再用Modelsim新建一个仿真工程,将测试文件和顶层添加进来。这里省略掉这些步骤。这里需要将IP Core中生成的两个文件添加进来,如下图所示。

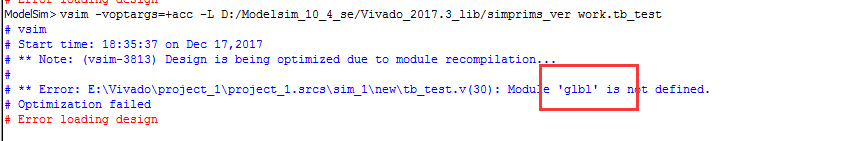

直接在work右键点击test bench文件进行仿真会出现如下错误,这是因为没有添加所仿IP Core的库文件

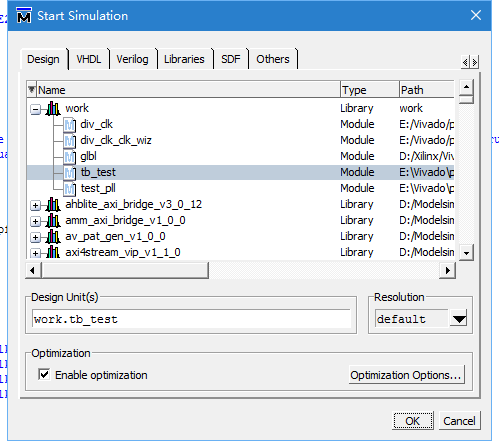

点击标题栏simulator——start simulator,在work里选中test bench。

点击libraries,点击添加所需要的库,这里只需要simprims_ver

点击这里后还是会出现错误,打印出来的信息如下,提示缺少glbl模块,

这是Xilinx的全局复位模块,该模块的路径在你Vivado的安装路径里,比如我的是D:\Xilinx\Vivado2017.3\Vivado\2017.3\data\verilog\src中,把它添加到工程里面,在test bench中如图所示例化一下这个模块,然后重新仿真一次。

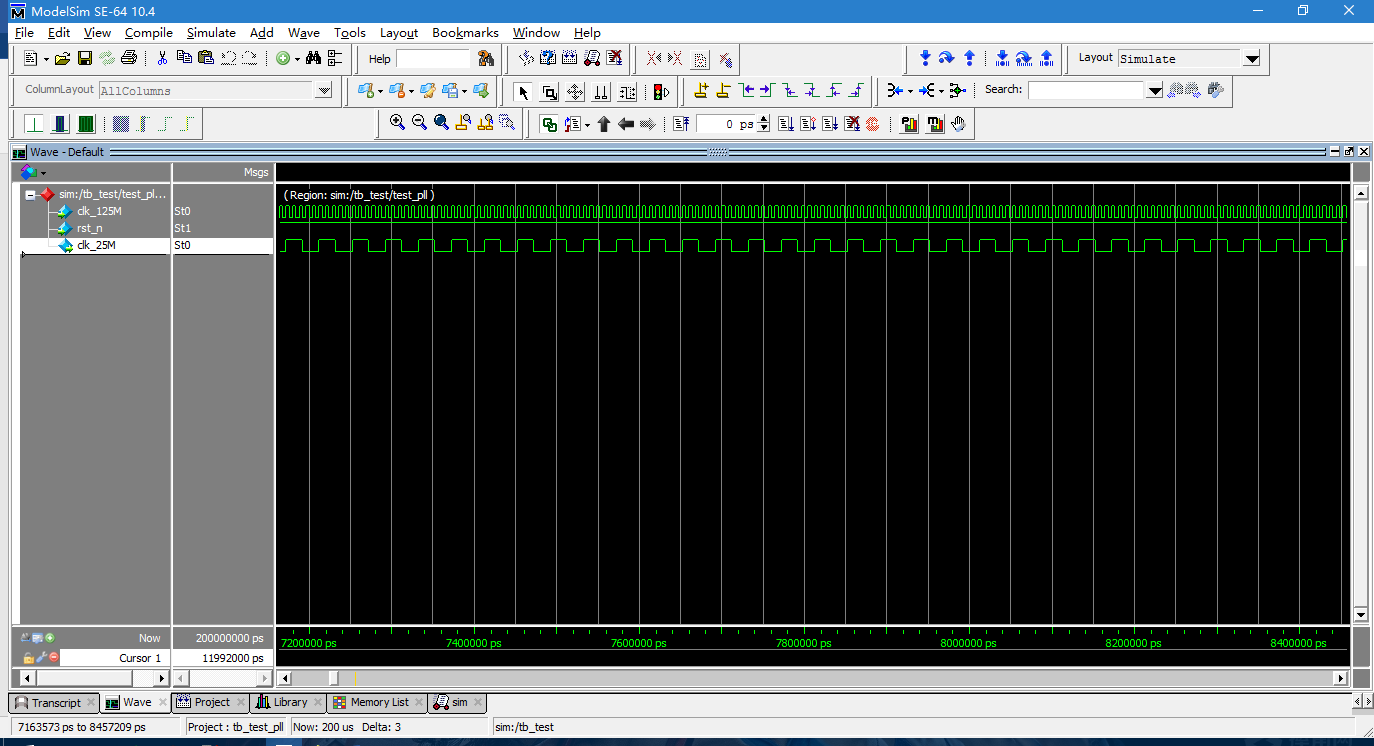

然后就可以看到波形了

我这里的测试工程师一个125Mhz分25Mhz的五分频。

接下来本人会继续尝试使用Modelsim仿真FIFO、RAM/ROM、Shift_RAM等常用IP Core,如果你有什么更加高效的方法,欢迎提出,欢迎指点。如果需要Modelsim软件请关注我的微信订阅号:开源FPGA,后台回复“Modelsim”即可获得,欢迎加入开源FPGA-交流群-I进行讨论,群号码:677163633。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan