浅谈Verilog HDL代码编写风格

消失了好久,没有写文章,也没有做笔记,因为最近再赶一个比赛,时间很紧,昨天周六终于结束了,所以趁着周末这会儿有时间,写点东西,记录下来。首先我学习FPGA才一年多,我知道自己没有资格谈论一些比较深层次的问题,对于这个行业来说可能我才是一直脚踩在门外面。所以这篇文章是写给一些刚开始学习FPGA、Verilog HDL的同学,我看过一些大神写的代码,然后尽量模仿大神写法,经过好几个大神的影响和自己的习惯摸索,最终算是总结出了一套自己的代码书写风格,当然我的代码风格还是一直在进化中。现在将自己的一些经验总结出来,希望对刚开始学习FPGA的朋友有所帮助。

首先,第一我还是要强调的是编辑器的作用,工欲善其事,必先利其器。之前整理过一篇,如何高效的编写Verilog HDL——菜鸟篇,点击查看。其中我介绍了使用notepad++的一些小技巧,当然还有很多网友使用gvim编辑器,对gVim编辑器,我也了解了很多,虽然上手比较麻烦,但是一劳永逸,我之后也是打算学习该编辑器的使用的,目前,时间比较紧,所以就暂且先用notepad++吧。熟悉verilog的人都知道,Verilog HDL设计其实使用20%的语法就可以设计出90%以上的电路,其中最长用的便是always块了,用软件自带的IDE的话编写效率其实是很差的。所以说一个好的顺手的编辑器至关重要,对于我们这些苦逼的技术工作者来说,经常看电脑屏幕一看就是一整天,然后还天天看,所以用Notepad++更换主题可以更好的为革命保护视力,

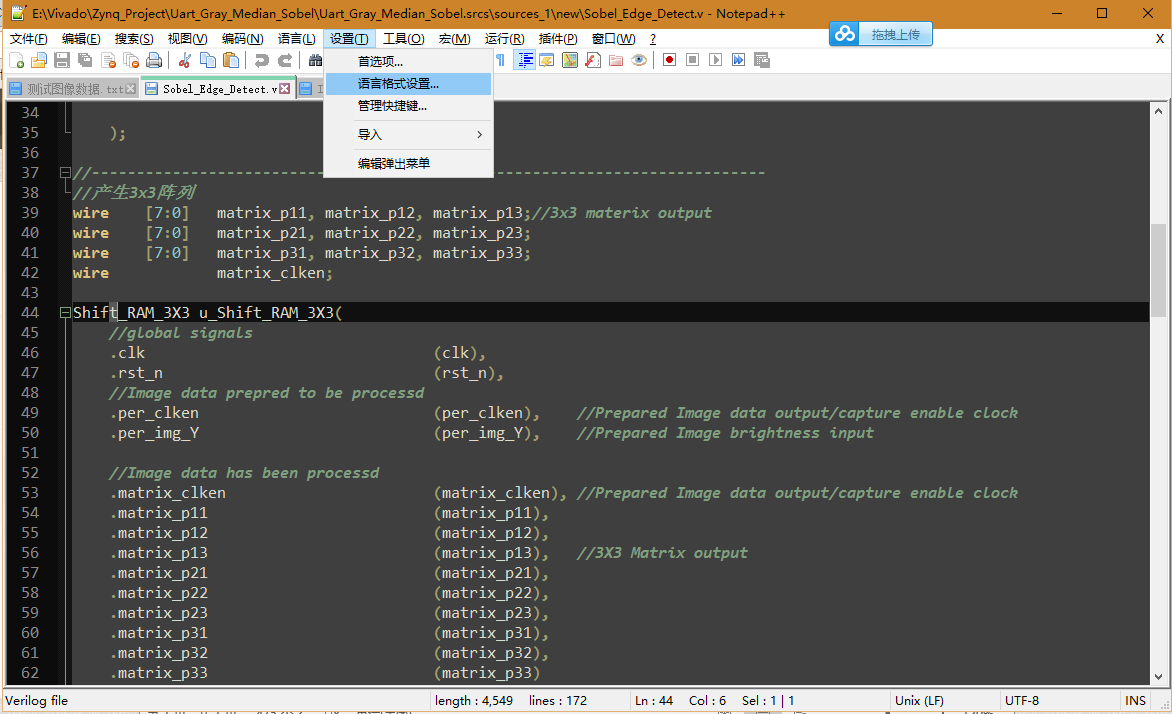

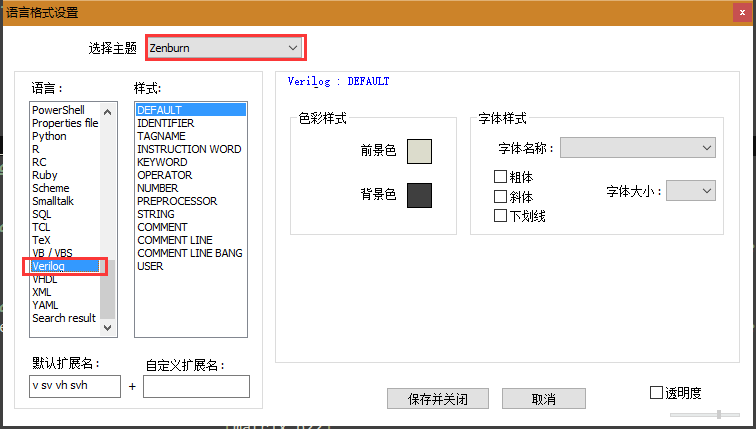

点击设置——语言格式设置,可设置编辑器主题

这里我选择的是如图所示的主题,我比较喜欢这个比较暗的颜色,

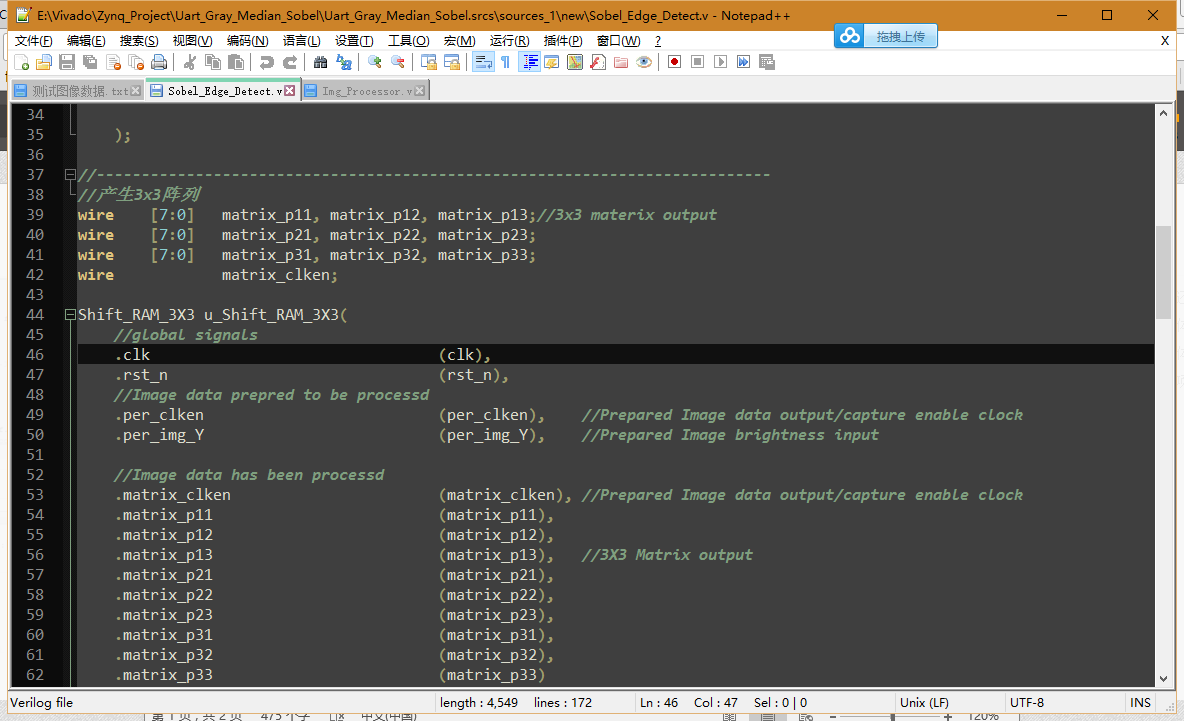

最终呈现的效果便如下图所示,是不是看起来很舒服呢!

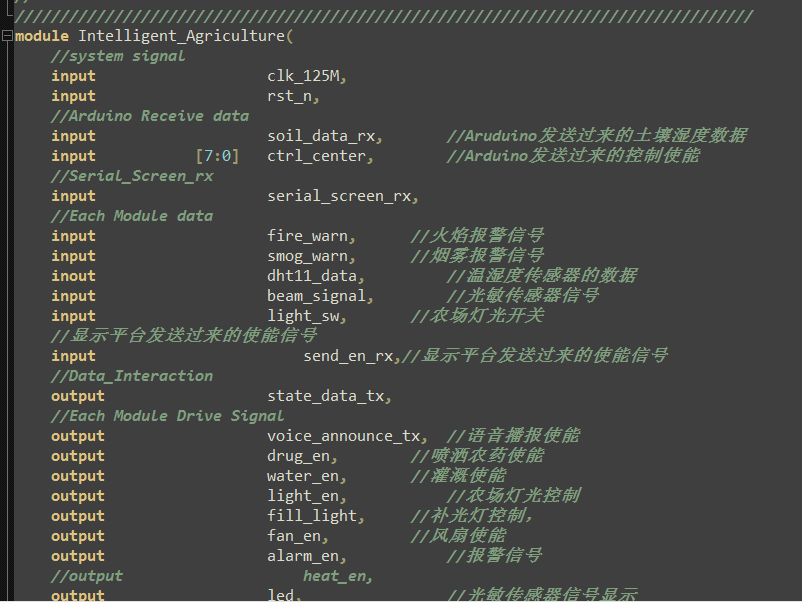

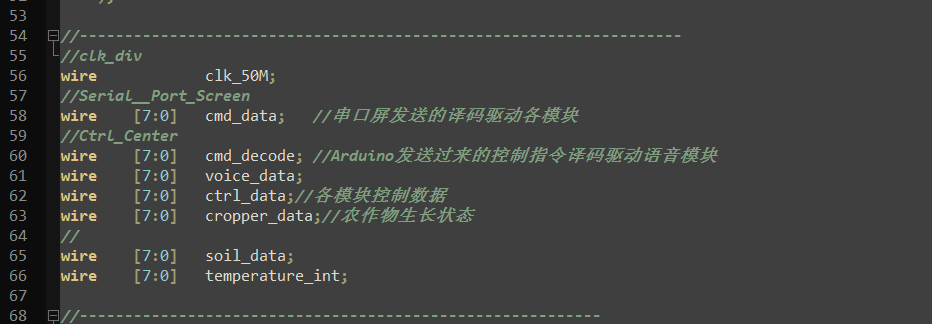

第二、代码的端口命名、内部寄存器的命名。下图是我们最近做的项目,可以看出在端口众多的情况下,端口的命名有多重要,基本上从信号的命名就可以直接联想到该信号的作用,同理,内部使用寄存器的命名也是如此。对于使用的系统时钟命令最好是用clk+后缀,加上时钟的频率。这样不仅自己看起来方便,别人看起来也方便。因为很多情况下,不同开发板的晶振是不一样的,但是编写者知道,其他人就未必知道了。我还真见过always@(posedge A or negedge B)这样写的人的,当然他也是刚开始学习了。

复位信号也直观只要,我习惯上写的而是rst+后缀,高电平有效还是低电平有效,rst_n(低电平有效negedge),rst_p(高电平有效posedge),我看过一些书上的复位信号命名的是clr,其实这两种命名的方法根本没有区别,一般情况下,我们复位都是将寄存器置数为0,也相当于清零,但也不排除,复位是给置数的情况,所以我习惯上使用rst_n来复位,及低电平复位。

其他的信号也就类似的,总结下来上就是,给信号起一目了然的名字,尽量使用缩写,不要信号的名字太长,信号的名字和功能作用中间用下划线隔开,要习惯性的给信号后面编写注释,给你编写的代码块做注释,给你编写的模块做注释,请记住你的代码不是给你一个人写的。

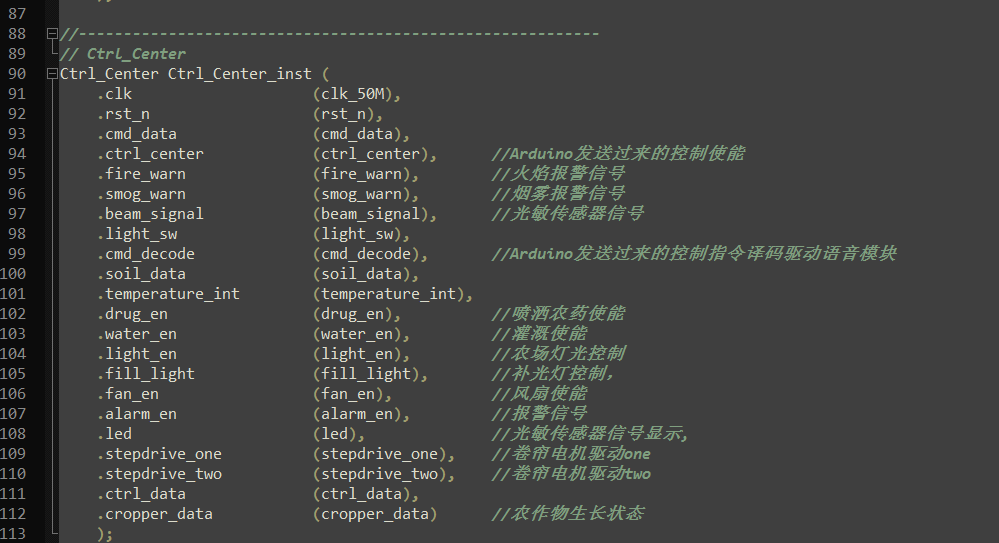

第三、代码的工整。从上图中可以看到,我在定义端口的时候是直接定义在module内部的,很多人的写法是先在module内部定义一遍端口,然后再module下面再写一遍input/output定义,其实这两种方式都可以,那么我为什么选择直接写在module内部呢,,,因为我懒啊。在编写代码的时候多用空格和TAB,把定义的信号对齐,这样写出代码是很漂亮的,每一段代码之间应该用分隔线隔开,这样整体看起来很清晰。

模块端口的实例化也是,这样的代码自己看着漂亮,别人看着也舒服,而且从顶往下看都会很明了。

第四、在设计中多实用时序逻辑,尤其是直接需要输出的端口。在我最近做的那个项目里,我使用了一些组合逻辑来做控制,但是后来发现这样会有一个弊端,每次系统上电的时候会有一段不稳定时间,在这段时间里,我的那几个控制模块就无规则的在乱启动,即使是在复位的情况下,这样可能会引起一些麻烦造成系统的不稳定,如果采用是时序逻辑的话,就完全可以避免这个问题了,在系统上电的时候,复位低有效,等上电稳定后,将复位键变为高电平。

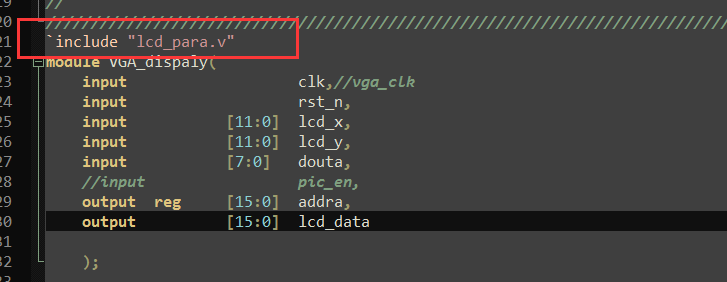

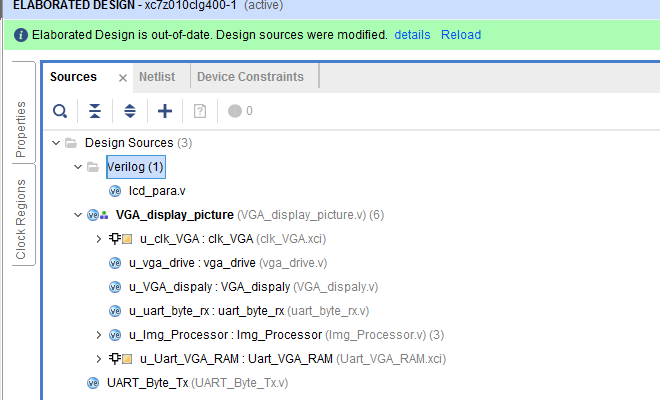

第五、如果一个工程里,同一个宏定义需要在多个文件里调用的话,建议使用调用文件。比如我在写VGA驱动的时候,行扫描、场扫描和各种颜色的定义参数需要在多个模块中使用,所以可在模块内部直接写如下图所示部分,把”`define”定义放在一个单独的文件里面,”parameter”参数定义肯定必须是在模块内部了,检查重复定义。

第六、使用异步复位、同步置数的设计思想(可以了解一下异步复位、同步释放),而且一个always块里,尽量值操作一个寄存器。一个模块的代码不要写的太多,使用模块化设计,而且在顶层文件里尽量不了写代码,为了在检查RTL图的时候比较方便明了的看出各个模块之间的连线图。模块内部不应该使用内部使用,同一个模块内的时钟应该是同一个时钟驱动下的,如果要使用别的时钟进行驱动的话,必须使用时钟使能而不是时钟触发,保持所有always块是同一个时钟上升沿触发,如果确实要使用内部时钟 门控时钟 或内部的复位信号 将它们放在顶层将这些信号的产生放在顶层的一个独立模块 这样所有的子模块分别使用单一的时钟和复位信号。对于使用if——else if——else或case语句必须把所有的情况都写上,避免生成锁存器。最重要的第一点,寄存器类型的数据应该有复位,我不习惯使用initial语句进行初始化,一般都是用异步复位来为维持系统的稳定。还有平时写代码的时候尽量不要使用for循环,当然有些必要的时候也是可以用的。

第七、如果你遇到实在不好解决的设计,那么这个时候,你就可以考虑一下状态机了。

我能想到的目前就只有这么多了,还有什么是我没有想到了和我做的可以留言告诉我。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

浙公网安备 33010602011771号

浙公网安备 33010602011771号