调试CS5343总结报告

一周前接到新任务,调试CS5343,百度一下,CS5343是一款音频采集的AD芯片,CS5343驱动代码是现成的,我的工作是提高芯片的采样速率,看了一边芯片的Datesheet,辛好东西不是很多。

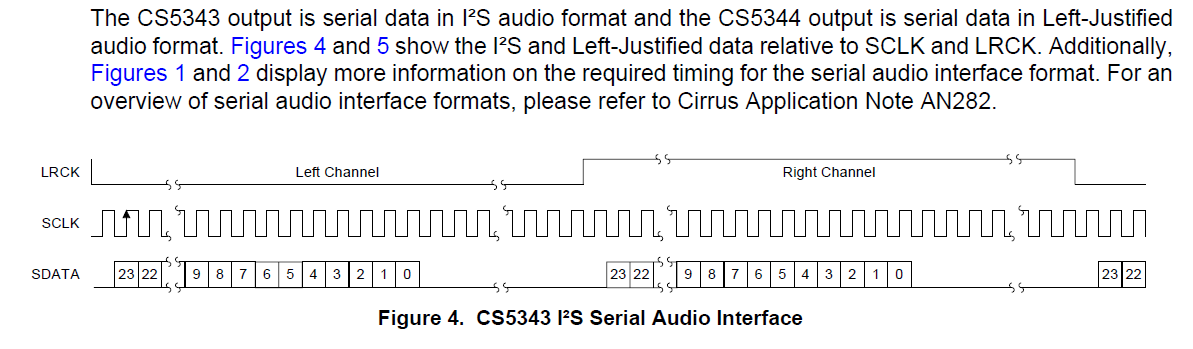

概述:CS5343是一款音频采集的AD芯片,使用I2S接口,即LR两路间隔输出。

1.文档总结

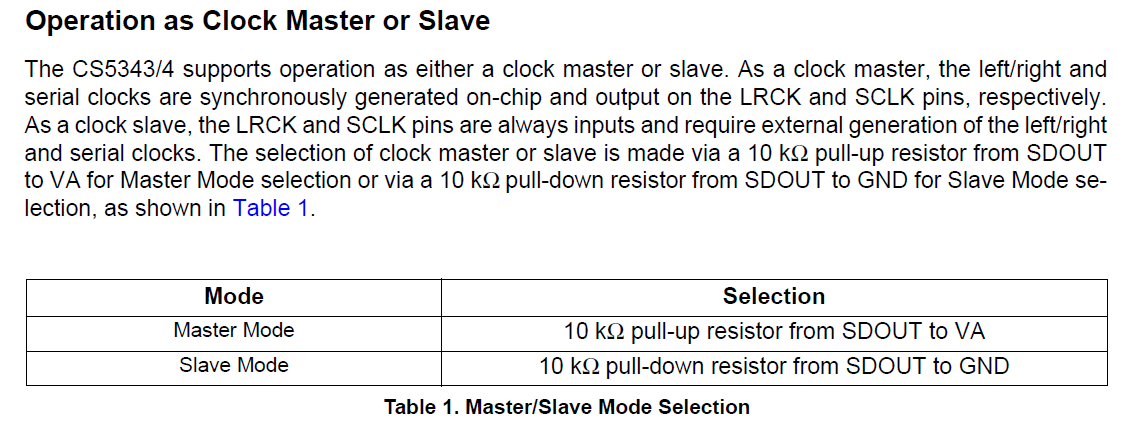

概述为:SDOUT上拉10K到VCC为主模式,下拉10K到GND为从模式。

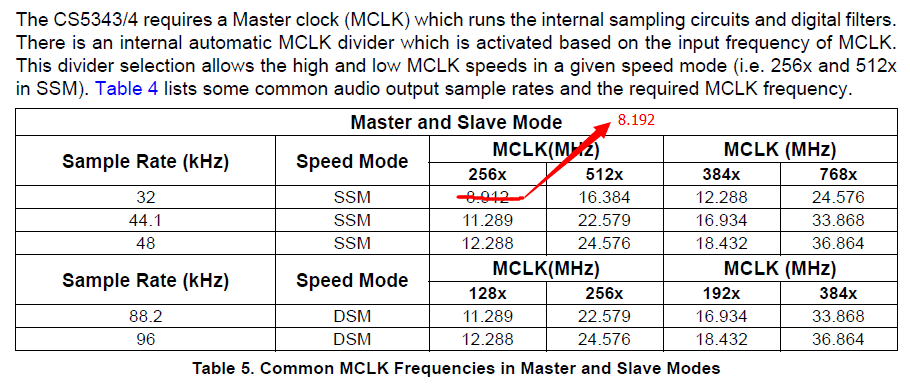

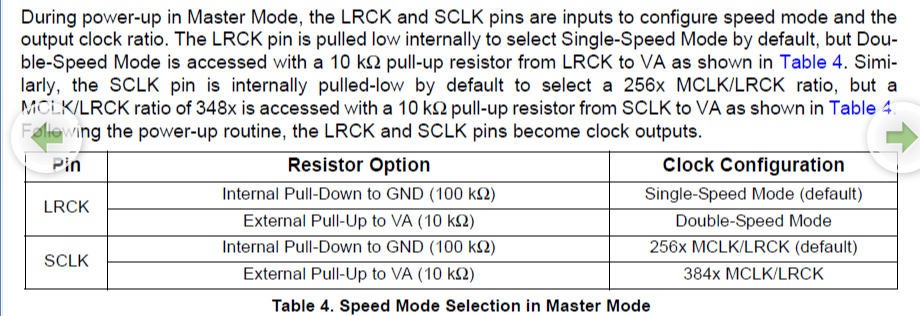

概述为:LRCK上拉10K到VCC为DSM模式,悬空(内部下拉100K到GND)时,为SSM模式.

SCLK上拉10K到VCC为192/384/768分频,悬空为128/256/512分频。

概述:

CS5343使用I2S接口,LRCK为低电平时,传输L的24bit数据;LRCK为高电平传输R路24bit数据。

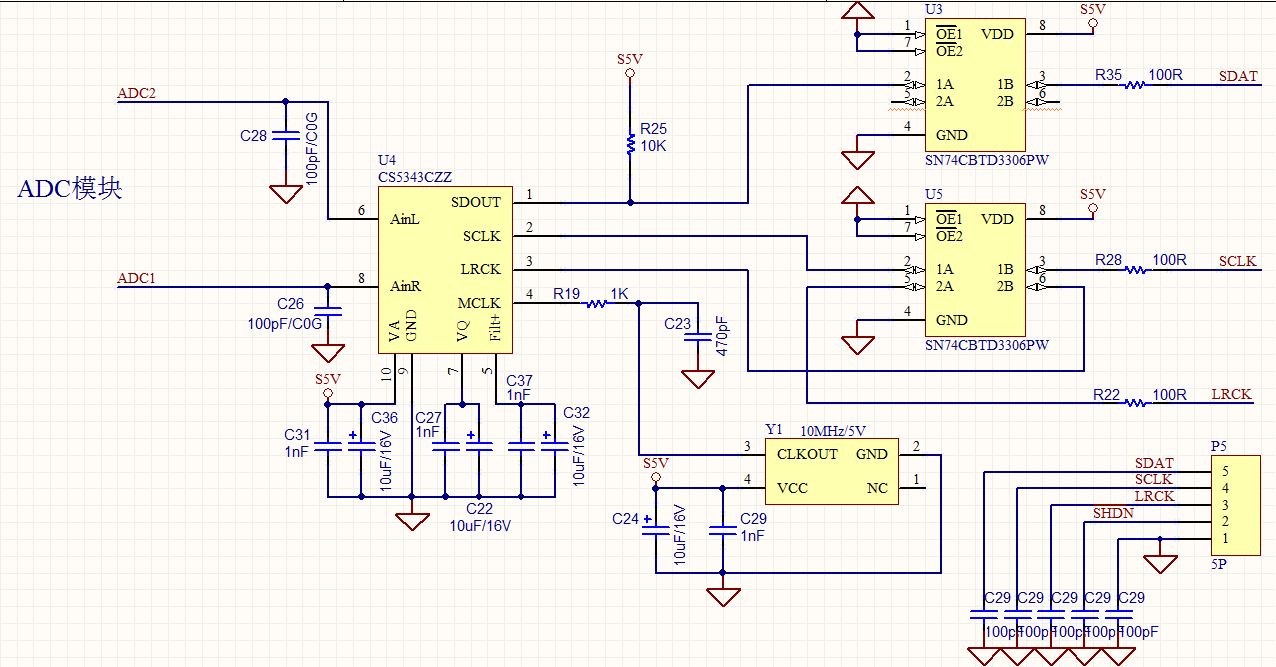

2.原理图设计

(1)A/D驱动晶振 MCLK=10MHz。

(2)数据位同步信号 SCLK=MCLK/4 = 2.5MHz

(3)双路数据的字同步信号 LRCK=SCLK/64=39.063KHz

(4)频率分析用FFT点数:N=1024

(5)数据采样频率:F = LRCK = 39.063 kHz

3.工程验证

根据硬件设计,现在CS5343工作模式为Master Mode,采用速率SSM(低速模式256分频,即10M/256 = 39.063K),I2S输出模式。

硬件修改后状况如下:SDOUT上拉10K到VCC,LRCK上拉10K到VCC,SCLK悬空,外部晶振采用10M(10M接近11.289M),硬件决定了采用DDM模式,128分频,故采样频率为Fr = 10M/128 = 78.125K,经示波器采样LRCK,发现一个78.12K的信号,所以分析是正确的。参考如下: