equalization

link第一次切换至8GT/s时,必须进行equalization。

link两端设备在初始化协商时,通过TS1/TS2广播对8GT/s的支持。

进入L0后,不管当前的速率是多少,如果需要equalization,那在equalization执行结束前,llink两端都不能发送DLLP。

Downstream端口需要将状态从L0切换成Recovery来进行equalization和切换速率至8GT/s。

Upstream端口也被允许(但不是必须)自动进行L0至Recovery的切换。

Upstream端口在收到Downstream发来的DLLP之前,不能发送DLLP。

如果自身需要,或者Upstream有请求,Downstream可以再次执行Equalization。

upstream端口可以通过TS2来请求重做equalization。

downstream端口可以通过TS1来重做equalization。

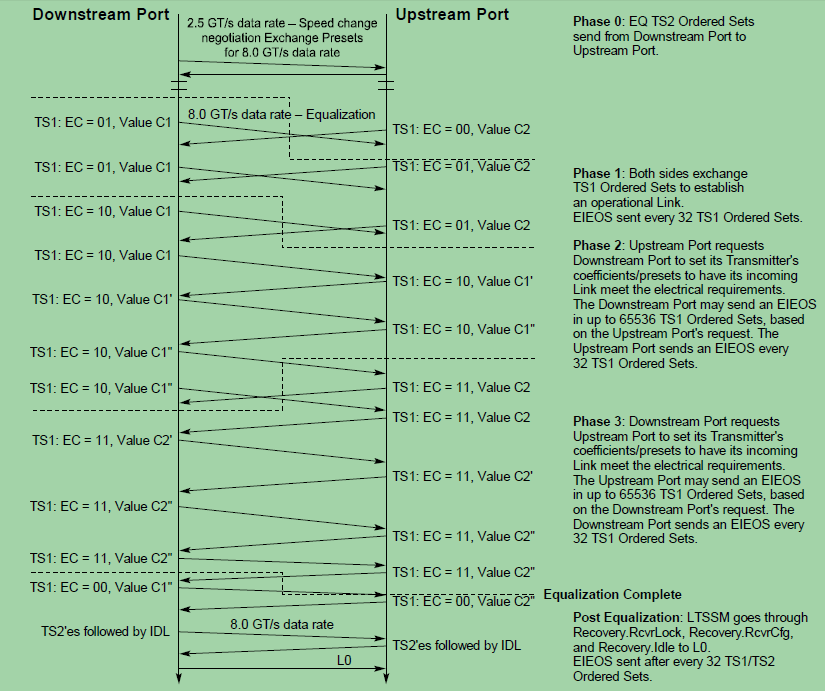

Equalization过程最多可分为4个Phase,在8GT/s速率,Phase信息通过TS1中的Equalization Control(EC)字段来传输。

Phase 0:

DS端口通过8b/10b编码发送每条lane的TX的preset值和RX的preset hint给US端口。这些值是在转换至8GT/s之前,在Recovery.RcvrCfg状态,通过EQ TS2进行发送的。

这些Preset值是提取自每条Lane的Equalization Control寄存器中的US_Port_TX_Preset和US_Port_RX_Preset_Hint字段。在数据速率变成8GT/s后,US端口通过TS1发送它收到的preset值。

Phase 1:

DS端口通过发送EC=01b的TS1来开始Phase 1,TS1中包含每条Lane的Equalization Control寄存器的DS_Port_TX_Preset和DS_Port_RX_Preset_Hint字段。

US端口根据DS发来的值,调整自己的RX,如果能继续Equalization,在收到DS的TS1之后,便也进入到Phase 1,发送EC=01的TS1。

DS端口在收到EC=01的TS1之后,判断可以继续余下的Phase,于是进行Phase 2。

Phase 2:

US端口调整DS的TX设置来匹配自己每条Lane的RX,来确保能收到符合需求的(BER<10^(-12))比特流。

DS端口通过发送EC=10的TS1来进入Phase 2。DS端口发送TX coefficients和preset。

US端口收到这些OS之后,可能会请求不同的coefficient (C0, C-1, C+1)和preset设置,并继续评估DS Lane的每个设置,直到达到最佳状态。然后,US端口发送EC=11的TS1给DS端口,并进入Phase 3。

Phase 3:

DS端口调整US的TX来匹配自己的RX设置,使用的方式是类似Phase 2的握手和evaluation过程,除了EC=11。DS发送EC=00的TS1来结束Phase 3和Equalization过程。

重复Equallization时,或在Link处于8GT/s时进行Equalization,Phase可以被跳过。因为没有必要让Link回到2.5GT/s或%。0GT/s来通过重发相同的EQ TS2来传送presets。

DS的TX fine-tuning如果不需要,那么它可以选择跳过Phase 2和Phase 3。