(原创)怎样把Altera University Program IP Core中的vga IP核挂到Nios II上

Altera University Program IP Core中有很多很受用的IP核,本人对其中的VGA核很感兴趣,却发现其并不是直接可用的(也许是我没找到),于是便写了个接口挂到了NiosII上。由于原例中在DE2开发板上实现,但其显存不能满足我的要求,于是又稍微改动使其能在DE2-70上实现。

Altera University Program IP Core中有很多很受用的IP核,本人对其中的VGA核很感兴趣,却发现其并不是直接可用的(也许是我没找到),于是便写了个接口挂到了NiosII上。由于原例中在DE2开发板上实现,但其显存不能满足我的要求,于是又稍微改动使其能在DE2-70上实现。

module vgaip_inst (

// inputs:

avs_s1_address,

avs_s1_byteenable,

avs_s1_chipselect,

avs_s1_read,

avs_s1_write,

avs_s1_writedata,

csi_clockreset_clk,

csi_clockreset_reset,

// outputs:

avs_s1_export_SRAM_ADDR,

avs_s1_export_SRAM_CE_N,

avs_s1_export_SRAM_DQ,

avs_s1_export_SRAM_LB_N,

avs_s1_export_SRAM_OE_N,

avs_s1_export_SRAM_UB_N,

avs_s1_export_SRAM_WE_N,

avs_s1_export_VGA_B,

avs_s1_export_VGA_BLANK,

avs_s1_export_VGA_G,

avs_s1_export_VGA_HS,

avs_s1_export_VGA_R,

avs_s1_export_VGA_SYNC,

avs_s1_export_VGA_VS,

avs_s1_readdata

)

;

output [ 17: 0] avs_s1_export_SRAM_ADDR;

output avs_s1_export_SRAM_CE_N;

inout [ 15: 0] avs_s1_export_SRAM_DQ;

output avs_s1_export_SRAM_LB_N;

output avs_s1_export_SRAM_OE_N;

output avs_s1_export_SRAM_UB_N;

output avs_s1_export_SRAM_WE_N;

output [ 9: 0] avs_s1_export_VGA_B;

output avs_s1_export_VGA_BLANK;

output [ 9: 0] avs_s1_export_VGA_G;

output avs_s1_export_VGA_HS;

output [ 9: 0] avs_s1_export_VGA_R;

output avs_s1_export_VGA_SYNC;

output avs_s1_export_VGA_VS;

output [ 15: 0] avs_s1_readdata;

input [ 17: 0] avs_s1_address;

input [ 1: 0] avs_s1_byteenable;

input avs_s1_chipselect;

input avs_s1_read;

input avs_s1_write;

input [ 15: 0] avs_s1_writedata;

input csi_clockreset_clk;

input csi_clockreset_reset;

wire [ 17: 0] avs_s1_export_SRAM_ADDR;

wire avs_s1_export_SRAM_CE_N;

wire [ 15: 0] avs_s1_export_SRAM_DQ;

wire avs_s1_export_SRAM_LB_N;

wire avs_s1_export_SRAM_OE_N;

wire avs_s1_export_SRAM_UB_N;

wire avs_s1_export_SRAM_WE_N;

wire [ 9: 0] avs_s1_export_VGA_B;

wire avs_s1_export_VGA_BLANK;

wire [ 9: 0] avs_s1_export_VGA_G;

wire avs_s1_export_VGA_HS;

wire [ 9: 0] avs_s1_export_VGA_R;

wire avs_s1_export_VGA_SYNC;

wire avs_s1_export_VGA_VS;

wire [ 15: 0] avs_s1_readdata;

vgaip the_vgaip

(

.avs_s1_address (avs_s1_address),

.avs_s1_byteenable (avs_s1_byteenable),

.avs_s1_chipselect (avs_s1_chipselect),

.avs_s1_export_SRAM_ADDR (avs_s1_export_SRAM_ADDR),

.avs_s1_export_SRAM_CE_N (avs_s1_export_SRAM_CE_N),

.avs_s1_export_SRAM_DQ (avs_s1_export_SRAM_DQ),

.avs_s1_export_SRAM_LB_N (avs_s1_export_SRAM_LB_N),

.avs_s1_export_SRAM_OE_N (avs_s1_export_SRAM_OE_N),

.avs_s1_export_SRAM_UB_N (avs_s1_export_SRAM_UB_N),

.avs_s1_export_SRAM_WE_N (avs_s1_export_SRAM_WE_N),

.avs_s1_export_VGA_B (avs_s1_export_VGA_B),

.avs_s1_export_VGA_BLANK (avs_s1_export_VGA_BLANK),

.avs_s1_export_VGA_G (avs_s1_export_VGA_G),

.avs_s1_export_VGA_HS (avs_s1_export_VGA_HS),

.avs_s1_export_VGA_R (avs_s1_export_VGA_R),

.avs_s1_export_VGA_SYNC (avs_s1_export_VGA_SYNC),

.avs_s1_export_VGA_VS (avs_s1_export_VGA_VS),

.avs_s1_read (avs_s1_read),

.avs_s1_readdata (avs_s1_readdata),

.avs_s1_write (avs_s1_write),

.avs_s1_writedata (avs_s1_writedata),

.csi_clockreset_clk (csi_clockreset_clk),

.csi_clockreset_reset (csi_clockreset_reset)

);

endmodule

module vgaip(

//nios port

//inputs

csi_clockreset_clk,

csi_clockreset_reset,

avs_s1_address,

avs_s1_byteenable,

avs_s1_chipselect,

avs_s1_read,

avs_s1_write,

avs_s1_writedata,

//outputs

avs_s1_readdata,

//vga port

//outputs

avs_s1_export_VGA_BLANK,

avs_s1_export_VGA_SYNC,

avs_s1_export_VGA_HS,

avs_s1_export_VGA_VS,

avs_s1_export_VGA_R,

avs_s1_export_VGA_G,

avs_s1_export_VGA_B,

//sram port

avs_s1_export_SRAM_DQ, // SRAM Data bus 16 Bits

avs_s1_export_SRAM_ADDR, // SRAM Address bus 18 Bits

avs_s1_export_SRAM_LB_N, // SRAM Low-byte Data Mask

avs_s1_export_SRAM_UB_N, // SRAM High-byte Data Mask

avs_s1_export_SRAM_CE_N, // SRAM Chip chipselect

avs_s1_export_SRAM_OE_N, // SRAM Output chipselect

avs_s1_export_SRAM_WE_N // SRAM Write chipselect

);

/*****************************************************************************

* Port Declarations *

*****************************************************************************/

input csi_clockreset_clk;

input csi_clockreset_reset;

input [17:0] avs_s1_address;

input [1:0] avs_s1_byteenable;

input avs_s1_chipselect;

input avs_s1_read;

input avs_s1_write;

input [15:0] avs_s1_writedata;

//outputs

output [15:0] avs_s1_readdata;

output avs_s1_export_VGA_BLANK;

output avs_s1_export_VGA_SYNC;

output avs_s1_export_VGA_HS;

output avs_s1_export_VGA_VS;

output [9:0] avs_s1_export_VGA_R;

output [9:0] avs_s1_export_VGA_G;

output [9:0] avs_s1_export_VGA_B;

inout [15:0] avs_s1_export_SRAM_DQ; // SRAM Data bus 16 Bits

output [17:0] avs_s1_export_SRAM_ADDR; // SRAM Address bus 18 Bits

output avs_s1_export_SRAM_LB_N; // SRAM Low-byte Data Mask

output avs_s1_export_SRAM_UB_N; // SRAM High-byte Data Mask

output avs_s1_export_SRAM_CE_N; // SRAM Chip chipselect

output avs_s1_export_SRAM_OE_N; // SRAM Output chipselect

output avs_s1_export_SRAM_WE_N; // SRAM Write chipselect

/*****************************************************************************

* Internal Wires and Registers Declarations *

*****************************************************************************/

// wire avs_s1_export_VGA_BLANK;

// wire avs_s1_export_VGA_SYNC;

// wire avs_s1_export_VGA_HS;

// wire avs_s1_export_VGA_VS;

// wire [9:0] avs_s1_export_VGA_R;

// wire [9:0] avs_s1_export_VGA_G;

// wire [9:0] avs_s1_export_VGA_B;

wire ready;

wire [29:0] data;

wire startofpacket;

wire endofpacket;

wire empty;

wire valid;

wire [15:0] SRAM_DQ; // SRAM Data bus 16 Bits

wire [17:0] SRAM_ADDR; // SRAM Address bus 18 Bits

wire SRAM_LB_N; // SRAM Low-byte Data Mask

wire SRAM_UB_N; // SRAM High-byte Data Mask

wire SRAM_CE_N; // SRAM Chip chipselect

wire SRAM_OE_N; // SRAM Output chipselect

wire SRAM_WE_N; // SRAM Write chipselect

Altera_UP_Avalon_Pixel_Buffer buffer(

// Inputs

.clk(csi_clockreset_clk),

.reset(csi_clockreset_reset),

.address(avs_s1_address),

.byteenable(avs_s1_byteenable),

.chipselect(avs_s1_chipselect),

.read(avs_s1_read),

.write(avs_s1_write),

.writedata(avs_s1_writedata),

.stream_out_ready(ready),

// Bi-Directional

.SRAM_DQ(avs_s1_export_SRAM_DQ),

// Outputs

.readdata(avs_s1_readdata),

.stream_out_data(data),

.stream_out_startofpacket(startofpacket),

.stream_out_endofpacket(endofpacket),

.stream_out_empty(empty),

.stream_out_valid(valid),

.SRAM_ADDR(avs_s1_export_SRAM_ADDR),

.SRAM_LB_N(avs_s1_export_SRAM_LB_N),

.SRAM_UB_N(avs_s1_export_SRAM_UB_N),

.SRAM_CE_N(avs_s1_export_SRAM_CE_N),

.SRAM_OE_N(avs_s1_export_SRAM_OE_N),

.SRAM_WE_N(avs_s1_export_SRAM_WE_N)

);

Altera_UP_Avalon_VGA vga(

// Inputs

.clk(csi_clockreset_clk),

.reset(csi_clockreset_reset),

.pixel_data(data),

.pixel_startofpacket(startofpacket),

.pixel_endofpacket(endofpacket),

.pixel_empty(empty),

.pixel_valid(valid),

// Bidirectionals

// Outputs

.pixel_ready(ready),

.VGA_BLANK(avs_s1_export_VGA_BLANK),

.VGA_SYNC(avs_s1_export_VGA_SYNC),

.VGA_HS(avs_s1_export_VGA_HS),

.VGA_VS(avs_s1_export_VGA_VS),

.VGA_R(avs_s1_export_VGA_R),

.VGA_G(avs_s1_export_VGA_G),

.VGA_B(avs_s1_export_VGA_B)

);

endmodule

C源码:

#include <stdio.h>

#include "system.h"

#include "io.h"

#include "rgb565_640x480.h"

int main()

{

unsigned int i;

unsigned int j,k;

for(;;){

for(i=0;i<640*480;i++){

//rdata=IORD_32DIRECT(SWITCH_PIO_BASE,0);

IOWR_16DIRECT(VGAIP_INST_BASE,i,rgb565[i]);

for(j=0;j<10;j++){

for(k=0;k<10;k++){;}

}

}

}

printf("Hello from Nios II!\n");

return 0;

}

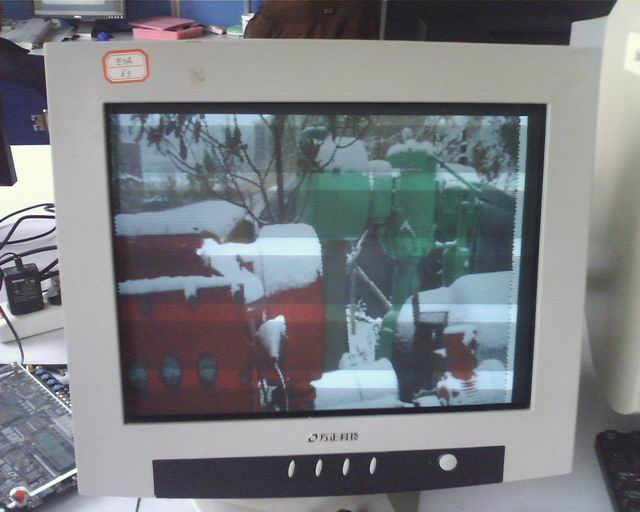

显示效果:

说明:

在DE2开发板上实现,由于DE2中的SSRAM只有512K,所以640*480*3(byte)的显存是不够的显示结果是经缩放

后的效果,具体可修改Altera_UP_Avalon_Pixel_Buffer buffer模块中的相关代码。

我把代码移植到DE2-70上后,显示的就很正常了。

Altera University Program IP Core下载地址

http://www.cnblogs.com/lunix/admin/ftp://ftp.altera.com/up/pub/University_Program_IP_Cores/80