SV仿真调度

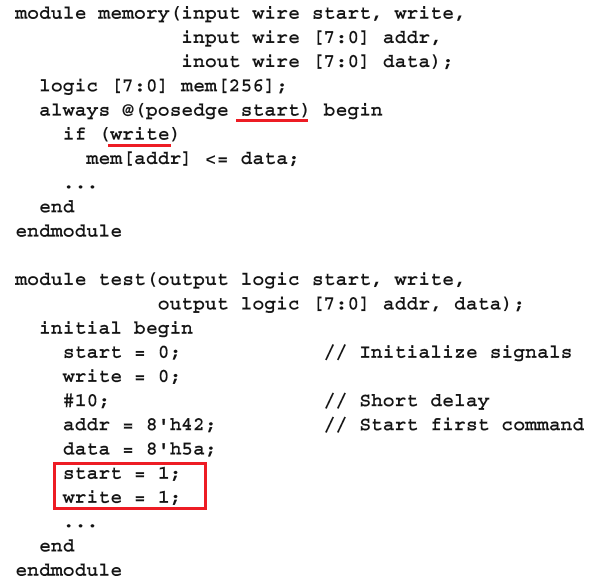

1、rtl中的信号和sv_tb中采样存在的问题:

测试平台sv_tb应该在逻辑而且在时序上也独立于设计。

一方面、测试平台在有效的时钟边沿或时钟边沿之后驱动待测设计;

一方面、在有效的时钟沿到来之前,在满足协议的前提下,尽量可能晚的采样;

上面的代码,由于测试平台先产生start信号,在产生其他信号,内存被start信号唤醒的时候,write、addr、data还保持着原来的值,这就导致了竞争状态。

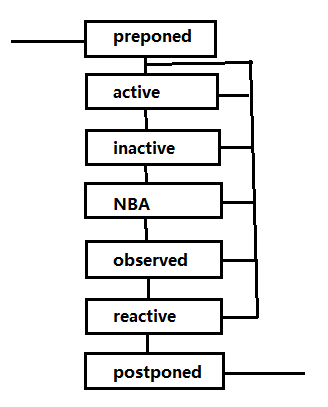

SV中通过 program block 来避免验证平台和dut中的竞争关系。

preponed:是上一个时间片进入本时间片的入口。

postponed:是入本时间片的出口,即所以event触发完毕,数据也被赋值完成。

active:执行所以处于该调度阶段的线程(always、assign、initial)。

阻塞赋值有关的操作执行完后,对应线程进入NBA区;

带#0延时操作的线程直接进入inactive区域;

observed:表示设计部分的线程已经执行完毕,接下来的区域是SV验证一侧所准备的。

reactive:经历了数据采样后,断言语句进行属性判断,同时,如果该区域再次对设计区域的变量和线网进行赋值,则被激活的线程再次迁移到active区域。

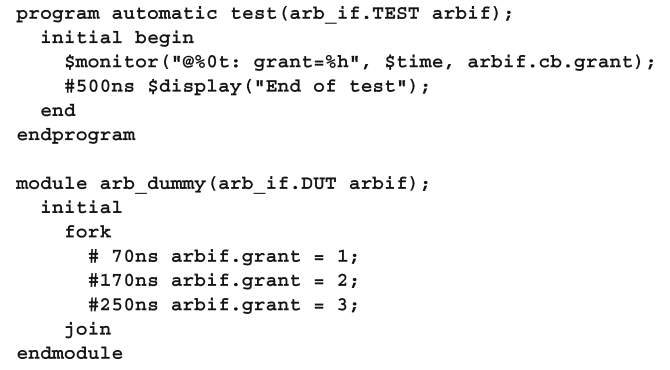

2、通过program可以避免测试平台和dut的竞争关系,如下例:

3、通过非阻塞赋值可以避免部分竞争:

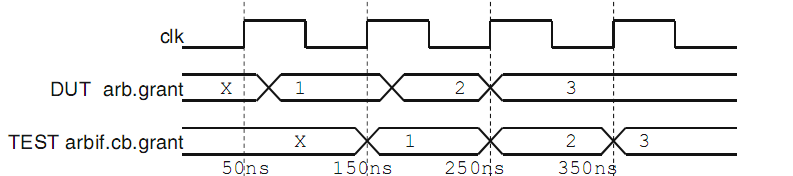

3、通过interface clocking解决时序采样和驱动信号的竞争问题:

本文来自博客园,作者:hematologist,转载请注明原文链接:https://www.cnblogs.com/littleMa/p/10841853.html

posted on 2019-05-09 23:41 hematologist 阅读(1352) 评论(0) 编辑 收藏 举报