vivado封装IP

reference: https://www.cnblogs.com/mouou/p/5851736.html

1、新建一个测试工程

工程化的设计方法是离不开工程的,第一步往往都是新建工程,后面我会学习去工程化的开发方法,可能会更加高效。

2、利用向导完成IP封装

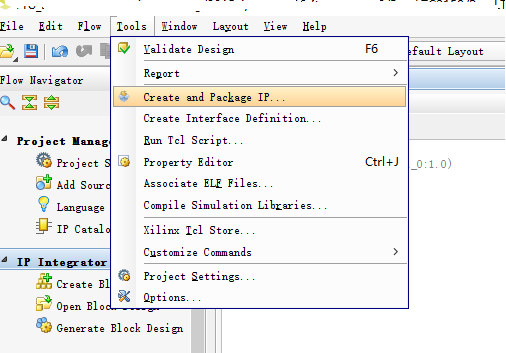

2.1、启动IP向导

方法为:ToolsàCreate and Package IP…,如图1所示。

图1 创建或者打包IP

点击Create and Package IP…命令,弹出向导,如图2所示。

图2 创建和封装IP向导

直接NEXT,进入下一界面,如图3所示。选择操作类型,我们这里不是新建IP,也不是要打包当前工程,而是要把runled_src文件夹下封装成一个IP,所以选择第2项。NEXT。

图3 选择操作类型为封装特定目录

接下来一步要注意了,选择你要打包的资源所在的文件夹,我这里是把要打包的3个文件放在了my_ip/runled_src下面,所以选择了这个路径,如图4所示。

图4 待打包资源所在文件夹

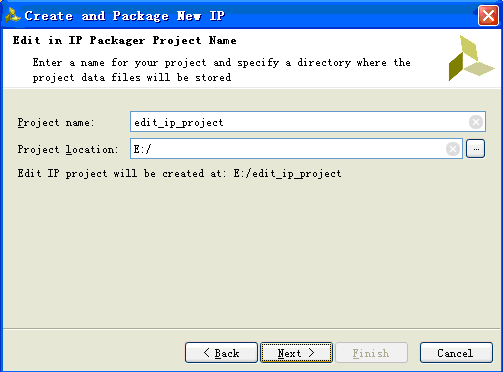

接下来,向导提示需要为IP工程制定一个名字和存储地址,如图5所示。这里采用默认名称即可,这个工程是临时的,IP封装完之后就会消失,再次编辑IP时才会再重新建立。

图5 临时工程名称、存储路径

NEXT,接下来就是最后一步了,是一些提示信息,大家可以自己看一下。点击Finish结束向导。

图6 summary

2.2、IP参数设置

注意,这里已经进入了edit_ip_project工程,是为打包IP核新建的那个工程,我们在上面指定了名称和路径(见图5). 点击:Project Manager --> IP Catalog打开如下:

对打包后的IP进行一些参数配置,如供应商,分类(默认是BaseIP,使用时要到该分类下查找我们封装的IP)等信息,这里不一一详述了,需要时,自行修改即可。

图7 IP参数设置

下一步:不做属性上的修改,直接进入最后一步(单击Review and Package),点击图8中的Package IP按钮,开始打包。

图8 开始打包

打包完成后,edit_ip_project工程会自动关闭,返回我们建立的测试工程。

3、查看IP封装结果

在Flow Navigator子窗体下找到Project Manager à IP Catalog,单击IP Catalog,右侧会弹出IP Catalog子窗体,将BaseIP目录展开,发现runled_top_v1_0已经成功导入。

到这里,封装已经完成了,本文要叙述的主题也已经完毕。

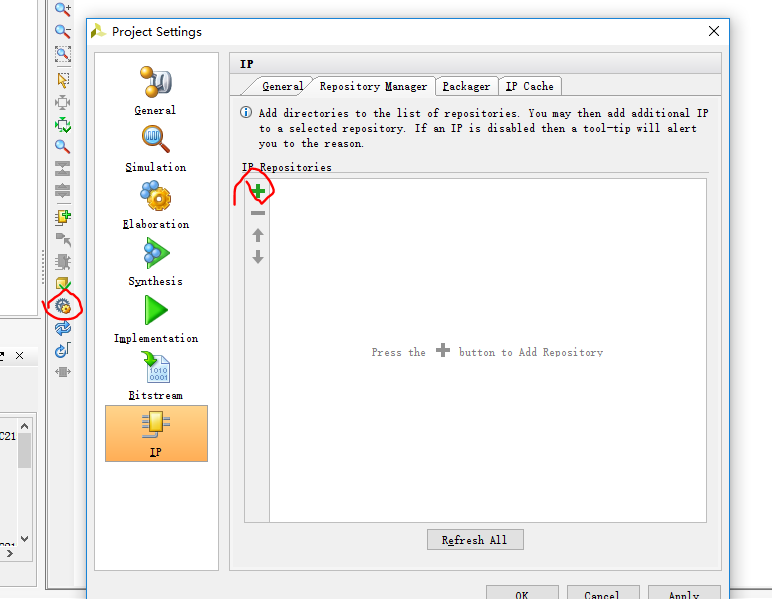

设置IP路径

------------------------------------------------------分割线---------------------------------------------------------------

但由于是第一次使用,不太放心,所以测试一下,接下爱来各小节是测试用的,不想看的可以直接略过。

4、测试

建立一个Block Design,将runled_top_v1_0添加进去,添加输入输出端口,最终结果如图9所示。

图9 Block Design

5、添加约束、综合、实现、生成Bitstream

约束文件:

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

|

#In the following the XDC constraint is matched to the origanal UCF constraint, XDC above, UCF below # Commented set_property PACKAGE_PIN Y9 [get_ports {iClk}]set_property IOSTANDARD LVCMOS33 [get_ports {iClk}] #NET GCLK LOC = Y9 | IOSTANDARD=LVCMOS33; # "GCLK" # Bank 33, Vcco = 3.3V#set_property IOSTANDARD LVCMOS33 [get_ports -filter { IOBANK == 33 } ]set_property PACKAGE_PIN T22 [get_ports {oLed[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {oLed[0]}]#NET LD0 LOC = T22 | IOSTANDARD=LVCMOS33; # "LD0"set_property PACKAGE_PIN T21 [get_ports {oLed[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {oLed[1]}]#NET LD1 LOC = T21 | IOSTANDARD=LVCMOS33; # "LD1"set_property PACKAGE_PIN U22 [get_ports {oLed[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {oLed[2]}]#NET LD2 LOC = U22 | IOSTANDARD=LVCMOS33; # "LD2"set_property PACKAGE_PIN U21 [get_ports {oLed[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {oLed[3]}]#NET LD3 LOC = U21 | IOSTANDARD=LVCMOS33; # "LD3"set_property PACKAGE_PIN V22 [get_ports {oLed[4]}]set_property IOSTANDARD LVCMOS33 [get_ports {oLed[4]}]#NET LD4 LOC = V22 | IOSTANDARD=LVCMOS33; # "LD4"set_property IOSTANDARD LVCMOS33 [get_ports {oLed[5]}]set_property PACKAGE_PIN W22 [get_ports {oLed[5]}]#NET LD5 LOC = W22 | IOSTANDARD=LVCMOS33; # "LD5"set_property PACKAGE_PIN U19 [get_ports {oLed[6]}]set_property IOSTANDARD LVCMOS33 [get_ports {oLed[6]}]#NET LD6 LOC = U19 | IOSTANDARD=LVCMOS33; # "LD6"set_property IOSTANDARD LVCMOS33 [get_ports {oLed[7]}]set_property PACKAGE_PIN U14 [get_ports {oLed[7]}]#NET LD7 LOC = U14 | IOSTANDARD=LVCMOS33; # "LD7" # Bank 34, Vcco = Vadj#set_property IOSTANDARD LVCMOS18 [get_ports -filter { IOBANK == 34 } ]set_property IOSTANDARD LVCMOS18 [get_ports {iRst_n}]set_property PACKAGE_PIN P16 [get_ports {iRst_n}]#NET BTNC LOC = P16 | IOSTANDARD=LVCMOS18; # "BTNC" |

生成Bitstream以便进行板级测试。

6、测试

利用Vivado内置的Hardware Manager向导将Bitstream烧写进FPGA,流水灯顺利出现,OK!

posted on 2019-01-03 14:14 limanjihe 阅读(2031) 评论(0) 编辑 收藏 举报