信息安全系统设计基础第七周学习总结

第六章 存储器层次结构

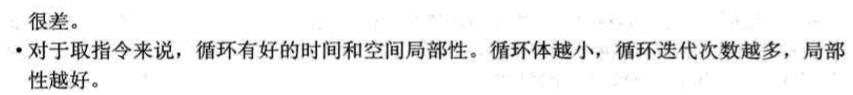

存储器系统是一个具有不同容量、成本和访问时间的存储设备的层次结构。

6.1 存储技术

一、了解三种常见存储技术:RAM/ROM/磁盘

1. 随机访问存储器:

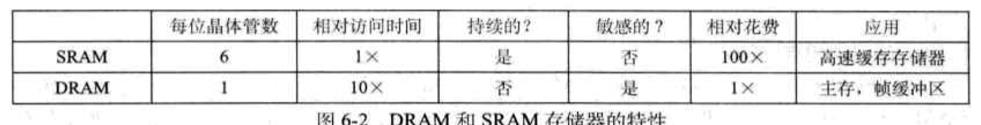

分为静态RAM和动态RAM。 静态比动态更快。

(1)静态RAM(SRAM)

将每个位存储在一个双稳态的存储器单元里。

(2)动态RAM(SRAM)

将每个位存储为对一个电容的充电。电容很小,大约有30毫微微法拉。每个单元由一个电容和一个访问晶体管组成。 DRAM对干扰非常敏感。当电容的电压被扰乱后(暴露在光线下),将永远不会恢复。

两者比较:

2.传统的DRAM芯片

传统的DRAM芯片中的单元(位)被分为d个超单元,每个超单元由w个DRAM单元组成。一个d*w位的DRAM总共存储了dw位信息。

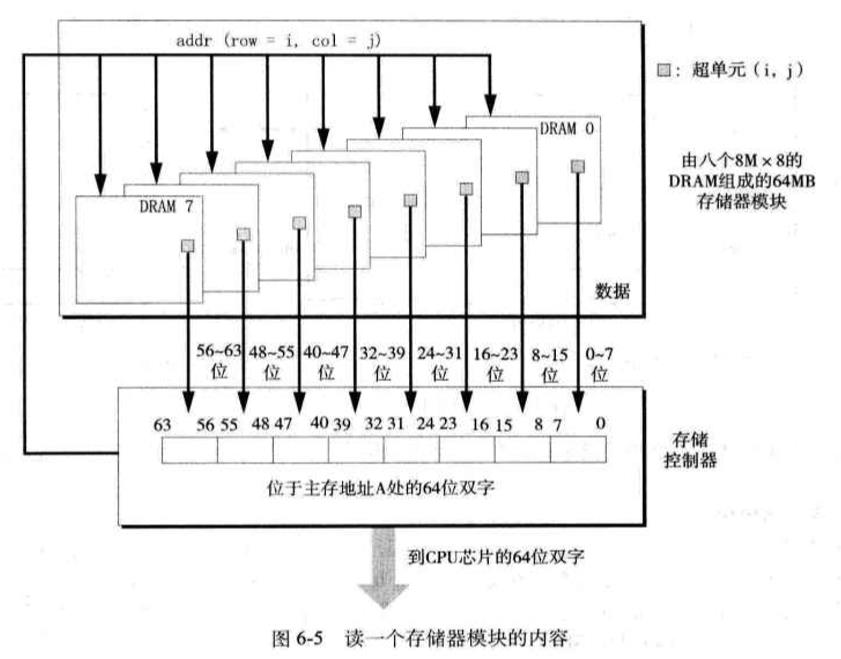

3.存储器模块

DRAM芯片芯片(插在主板的扩展槽上)包装在存储器模块中。常见的包括168引脚的双列直插存储器模块和72引脚的单列直插存储器模块,分别以64位和32位为块传送数据到存储控制器和从存储控制器中传出数据。

4.增强的DRAM

快页模式DRAM(FPM DRAM)

扩展数据输出DRAM(EDO DRAM)

同步DRAM(SDRAM)

双倍数据速率同步DRAM(DDR SDRAM)

Rambus DRAM(RDRAM)

视频DRAM(VDRAM)

5.非易失性存储器

只读存储器——ROM。

ROM是以能够被重编程(写)的次数和对他们进行重编程所用的机制来划分的。ROM有PROM,EPROM,E2PROM,FLASH。

可编程ROM(PROM),只能被编程一次。每个存储器单元有一种熔丝,它只能用高电流熔断一次。

可擦写可编程ROM(EPROM)能够被擦除和重编程的次数的数量级可以达到1000次。电子可擦除ROM(EEPROM)类似于EPROM,但可以直接在印刷电路卡上编程。

闪存——基于EEPROM。基于闪存的新型的磁盘驱动器为固态硬盘(SSD)。

固件——存储在ROM中的程序。

6.访问主存

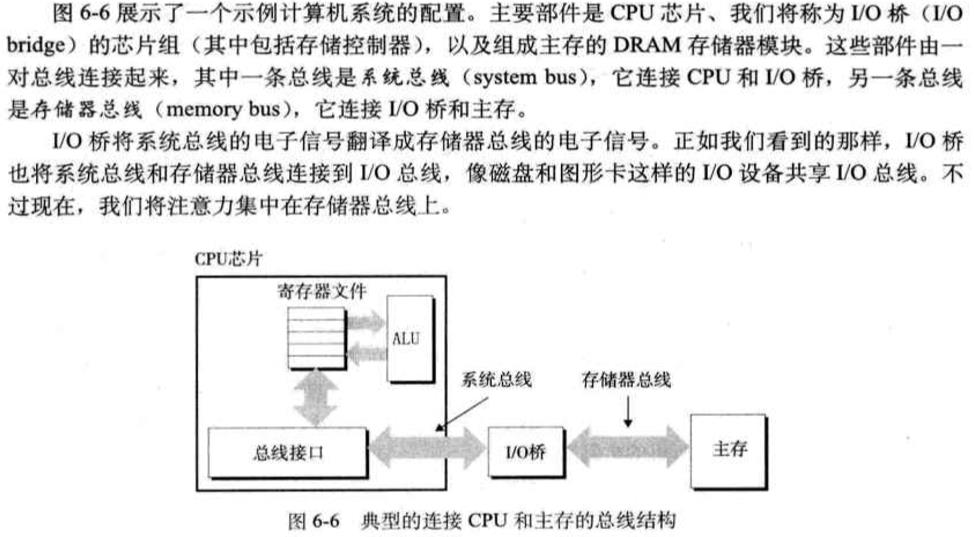

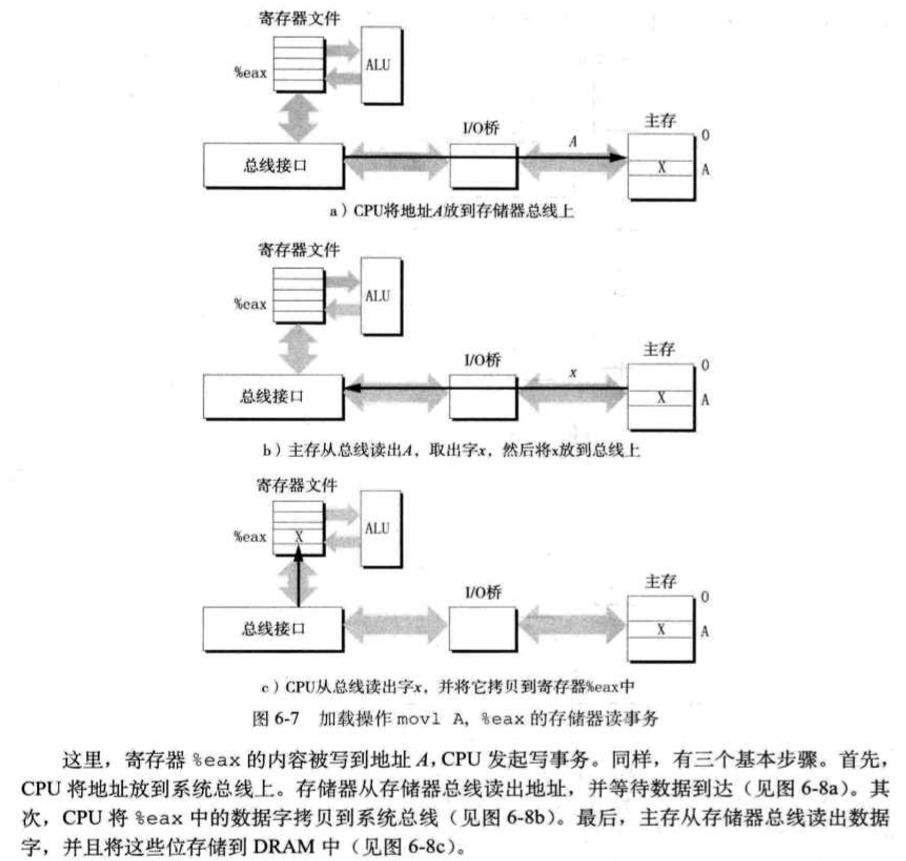

数据流通过称为总线的共享电子电路在处理器和DRAM主存之间来回。CPU和主存之间的数据传送通过一系列步骤来完成,这些步骤叫做总线事务。读事务:从主存传送数据到CPU。写事务:从CPU传送数据到主存。

!总线是一组并行的导线,能携带地址、数据和控制信号。

!重点理解:

二、磁盘存储

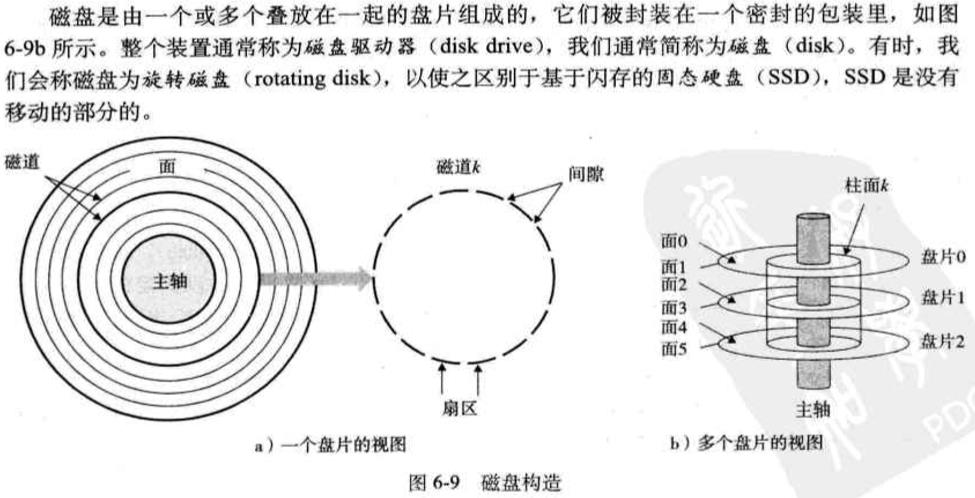

1.磁盘构造

磁盘结构:盘片、磁道、扇区、间隙、柱面;磁盘驱动器 磁盘是由盘片构成的。表面覆盖着磁性记录材料。

2.磁盘容量

3.磁盘操作

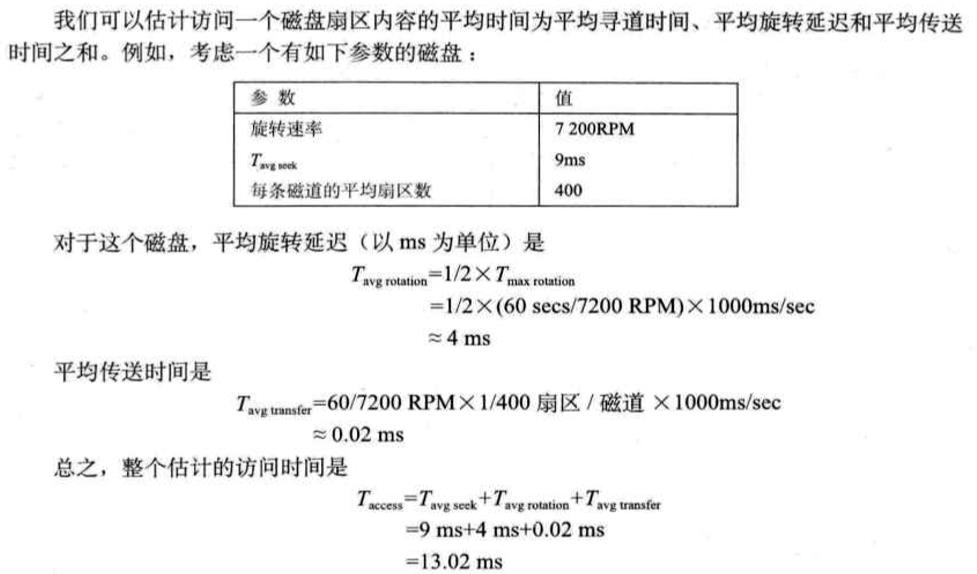

磁盘以扇区大小的块来读写数据。 对扇区的访问时间有三个主要部分:寻道时间、旋转时间和传送时间。

寻道时间:移动传动臂所需的时间成为寻道时间。其依赖于读/写头以前的位置和传动臂在盘面上移动的速度。一次寻道的最大时间可高达20ms。

旋转时间:依赖于当读写头到达目标扇区时盘面的位置和磁盘的旋转速度。最大旋转延迟是:

传送时间:依赖于旋转速度和每条磁道的扇区数目。估计一个扇区以秒为单位的平均传送时间:

4.逻辑磁盘块

(这个很重要,内存可以看成字节数组、磁盘可以看成块数组) 现代磁盘构造一个B个扇区大小的逻辑块的序列,编号0—B-1。磁盘中有一个小的硬件/固件设备,成为磁盘控制器。可将一个逻辑块号翻译成一个(盘面、磁道、扇区)三元组。

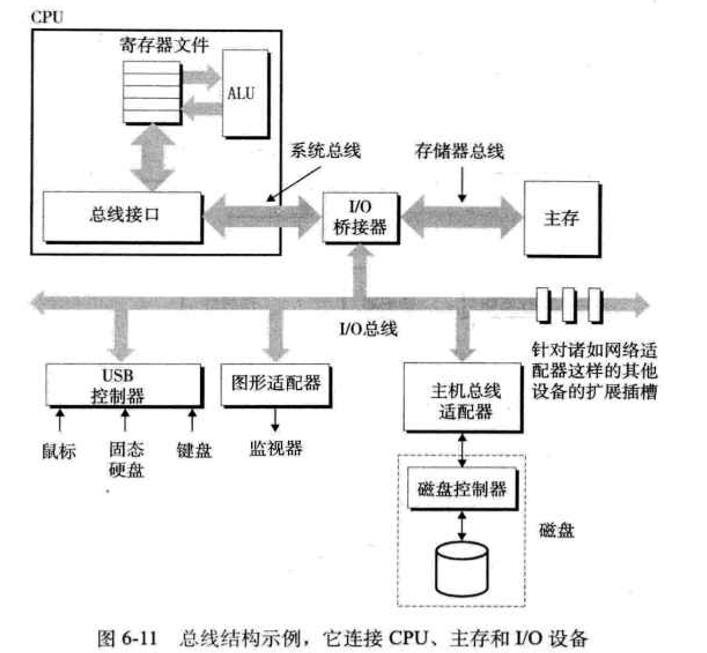

5.连接到I/O设备

系统总线和存储器总线是与CPU相关的。 I/O总线比系统总线和存储器总线慢,但可以容纳种类繁多的第三方I/O设备。三种不同的设备连接到I/O总线:

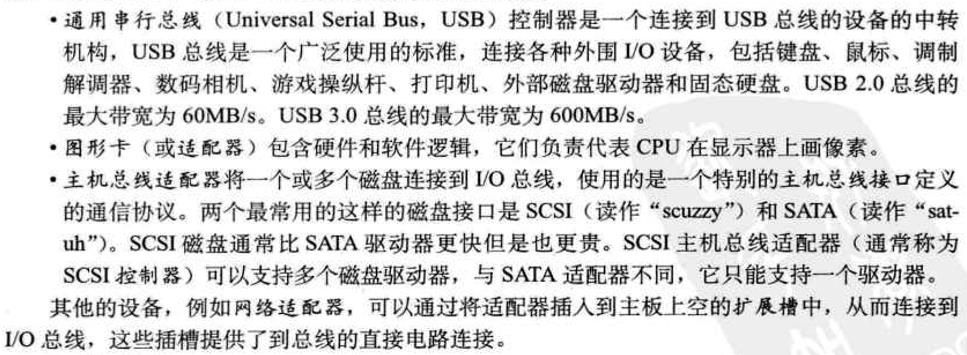

6.访问磁盘

概要描述:

直接存储器访问——设备自己执行读或写总线事务,不需要CPU的干涉。这种数据传送成为DMA传送。

三、固态硬盘

固态硬盘(SSD)是一种基于闪存的存储技术。一个SSD包由一个或多个闪存芯片和闪存翻译层(一个硬件/固件设备)组成。

随即读和写的性能差别是由底层闪存基本属性决定的。随机写慢的两个原因是: 擦除块需要将相对较长的时间;如果写操作试图修改一个包含已经有数据的页p,那么这个块中所有带有用数据的页都必须拷贝到一个新的块,然后才能进行对页p的写。

四、存储技术趋势

1.不同的存储技术有不同的价格和性能中折。

2.不同存储技术的价格和性能属性以截然不同的速率变化着。

6.2 局部性

局部性原理:一种倾向性,倾向于引用邻近于其他最近引用过的数据项的数据项,或者最近引用过的数据项本身。 局部性有两种不同的形式:时间局部性和空间局部性。在一个具有良好时间局部性的程序中,被引用过一次的存储器位置很可能在不远的将来再被多次引用。在一个具有良好空间局部性的程序中,如果一个存储器位置被引用了一次,那么程序很可能在不远的将来引用附近的一个存储器位置。

一、对程序数据引用的局部性

随着步长的增加,空间局部性下降。

二、取指令的局部性

代码区别于程序的一个重要属性是在运行时他不能被修改。当程序正在执行时,CPU只从存储器中读取他的指令,绝不会重写或修改这些指令。

三、量化评价局部性的简单原则:

6.3 存储器层次结构

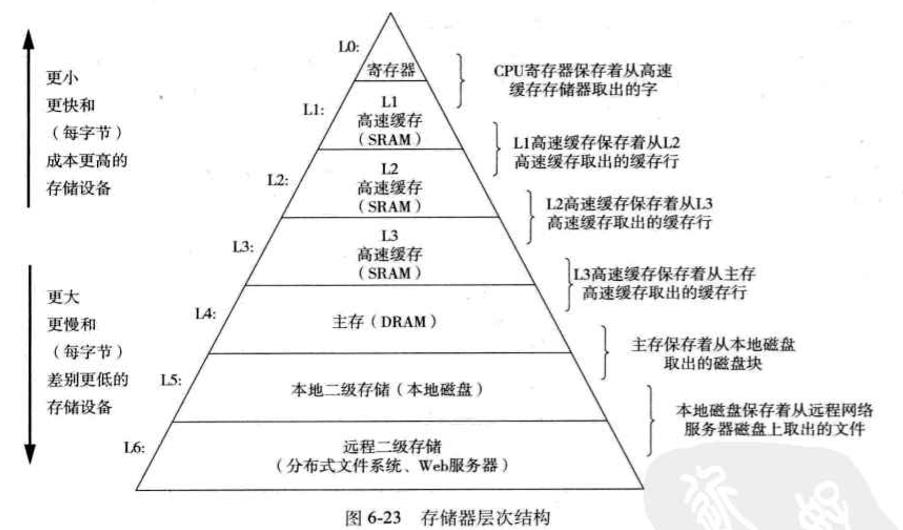

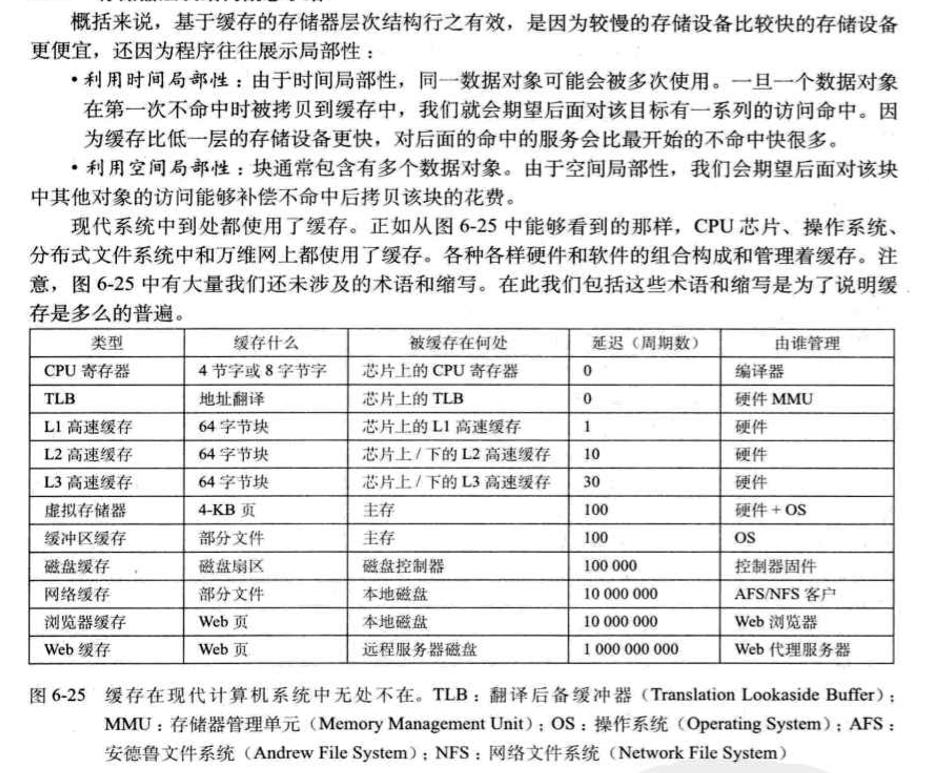

一、 存储器层次结构中的缓存

使用高速缓存的过程成为缓存。 存储器层次结构的中心思想:对于每个K,位于k层的更快更小的存储设备作为位于k+1层的更慢更大的存储设备的缓存。即每层存储设备都是下一层的“缓存”。 数据以块大小为传送单元。一般而言,层次结构中较低层的设备的访问时间较长,倾向于使用较大的快。

1.缓存命中

当程序需要k+1层的某个对象d时,他首先在当前存储在第k层的一个块中查找d。如果d刚好缓存在这层中,就是缓存命中。该程序直接从第k层读取d。

2.缓存不命中

第k层没有缓存数据对象d。此时,第k层的缓存从第k+1层缓存中取出包含d的那个块。如果第k层缓存已经满了的话,可能就会覆盖现存的一个块。

3.缓存不命中的种类

强制性不命中(或冷不命中)、冲突不命中(这个不太理解)、容量不命中。

4.缓存管理

每一层存储设备都是较低一层的缓存。 管理缓存的逻辑可是硬件、软件或是两者结合。

6.4 高速缓存存储器

早期存储器结构只有三层——CPU寄存器、DRAM主存储器和磁盘存储。后又添加L1(一级缓存,为SRAM高速缓存存储器)、L2或L3高速缓存。

高速缓存根据每个组的高速缓存行数E分类。

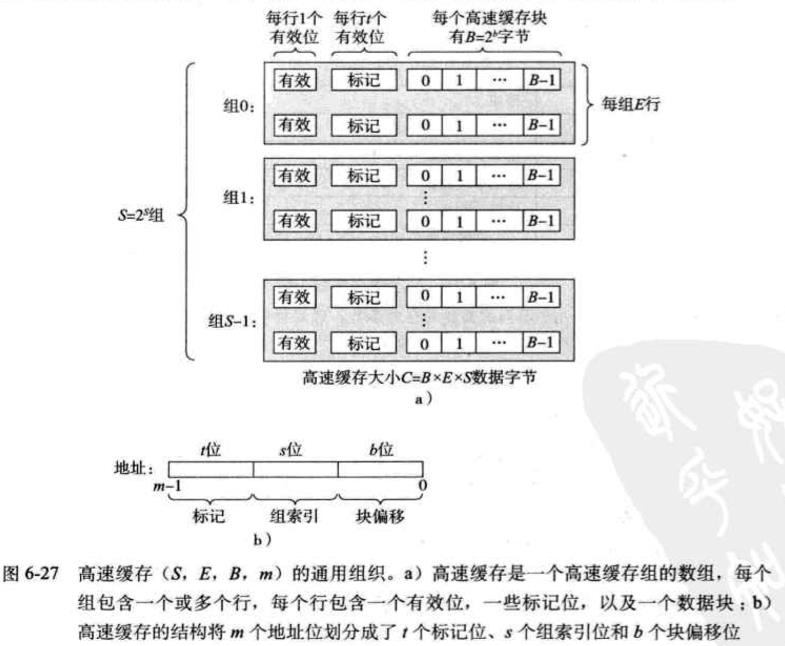

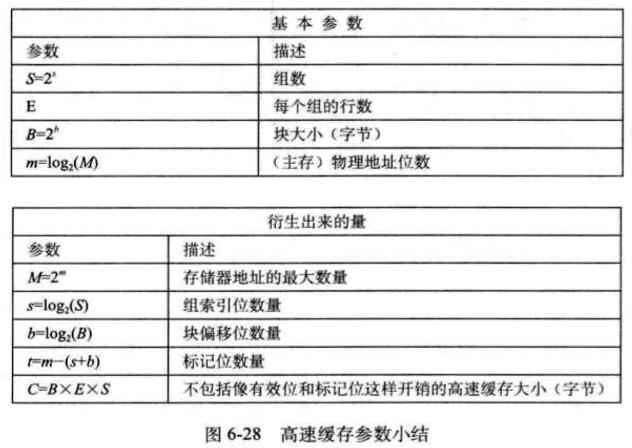

一、 通用的高速缓存存储器结构

高速缓存结构可以用元组(S,E,B,m)来描述。高速缓存的大小(容量)C指的是所有块大小的和。标记位和有效位不包括在内。因此C=SEB。

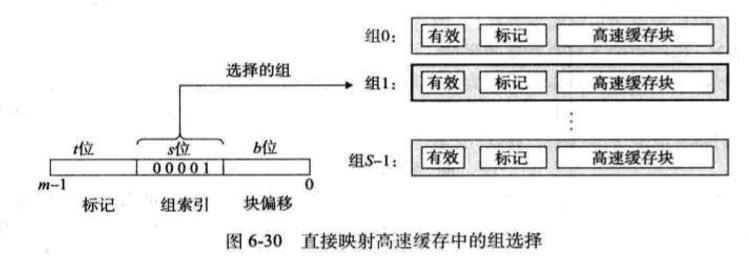

二、直接映射高速缓存

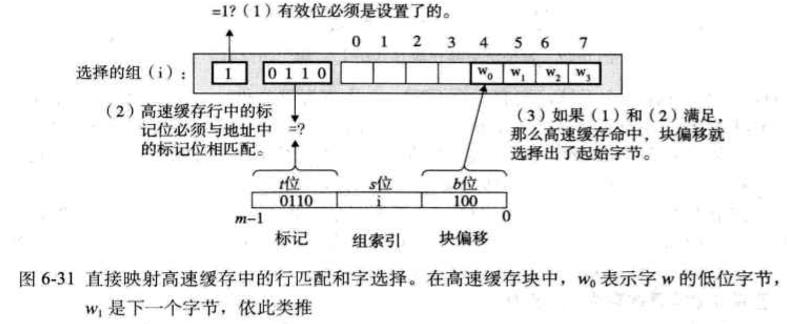

每个组只有一行(E=1)的高速缓存。 高速缓存确定一个请求是否命中,然后抽取出被请求字的过程分为三步:(1)组选择;(2)行匹配;(3)字抽取

直接映射高速缓存中不命中时的行替换:用新取出的行替换当前的行。

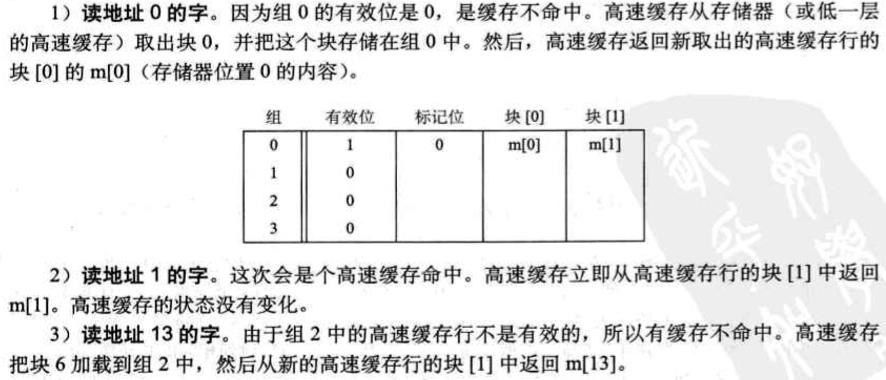

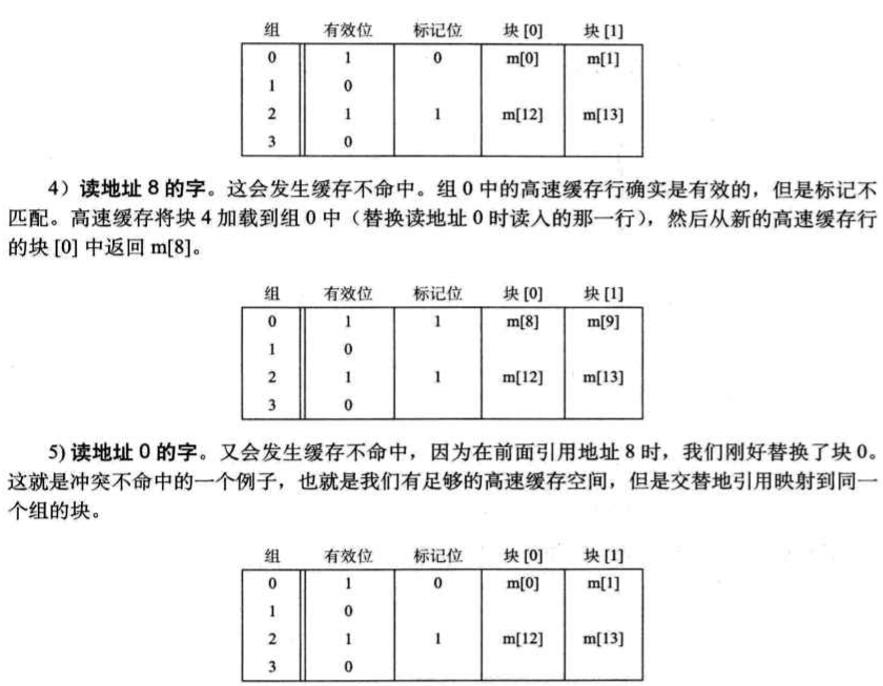

总结: 高速缓存用来选择组和标识行的机制极其简单。 ·标记位和索引位连起来唯一地标识了存储器中的每个块。 ·有8个存储器块,只有4个高速缓存组。多个块映射到同一个高速缓存组(即有相同的组索引)。 ·映射到同一个高速缓存组的块由标记位唯一地标识。 工作流程: 初始时,高速缓存是空的(即每个有效位都是0)。 理解例子:

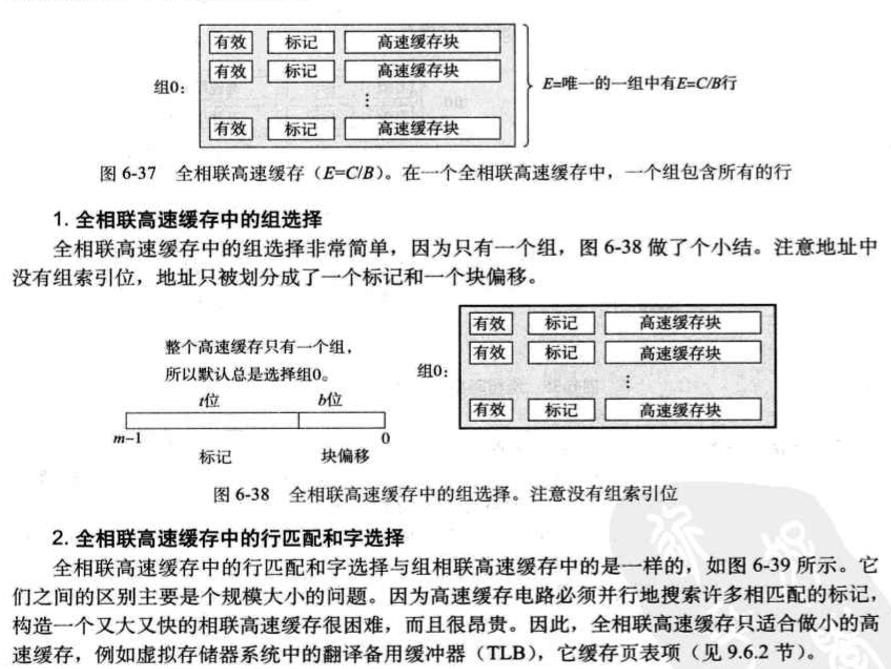

三、全相联高速缓存

由一个包含所有高速缓存行的组组成的。

遇到的问题及解决方法:

一开始看书的时候并不能完全理解有些知识,可能基础还是不太扎实。然后通过上网查找资料明白了许多,最后在做习题的过程中又加深了一遍印象。

但是对于缓存不明中中的冲突不明中不太理解:

这样的话不就没有办法进行缓存了吗。

参考资料:《深入理解计算机系统》

http://book.51cto.com/art/201412/460489.htm

http://blog.csdn.net/sunupzhou/article/details/7513418