Power Analysis是芯片设计实现中极重要的一环,因为它直接关系到芯片的性能和可靠性。Power Analysis 需要Timing Analysis 产生包含频率、transition 等时序信息的 Timing File,也需要包含Net Capacitance和Resistance信息的SPEF文件,功耗分析工具根据timing file 和RC value计算功耗或者分析IR-Drop/EM。

在介绍数字后端Power Signoff Flow之前,先大概论述一下芯片的功耗构成和基本原理。芯片功耗主要分为Static Power (静态功耗)和Dynamic Power(动态功耗)两大类。动态功耗来自于芯片晶体管的开关翻转,它取决于芯片的时钟频率和switching activity。静态功耗是指芯片晶体管的LeakagePower(泄漏功耗)。

进一步细分,动态功耗可以分为Internal Power和Switching Power.

-

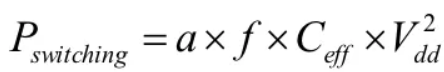

Switching power是由于芯片内instance 上的逻辑翻转对有效负载电容进行充放电所消耗的功耗。公式如下,其中,a是switching activity,f是clock frequency,Ceff是有效负载电容,Vdd是芯片电源电压。

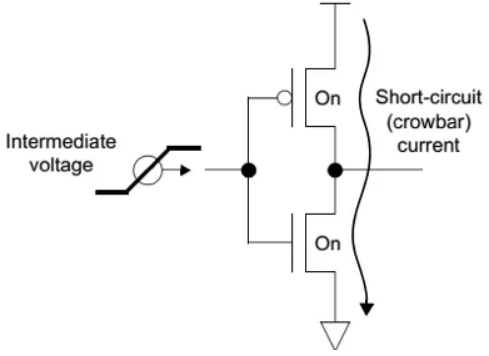

- Internal power是由于晶体管信号传输的某一个瞬间,PMOS和NMOS会同时导通的短路电流消耗的功耗。对于更低阈值电压或者transition time大的晶体管internal power会更大。

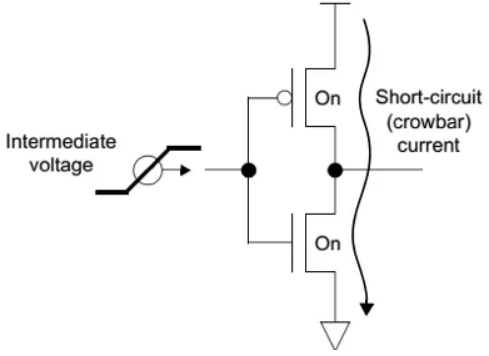

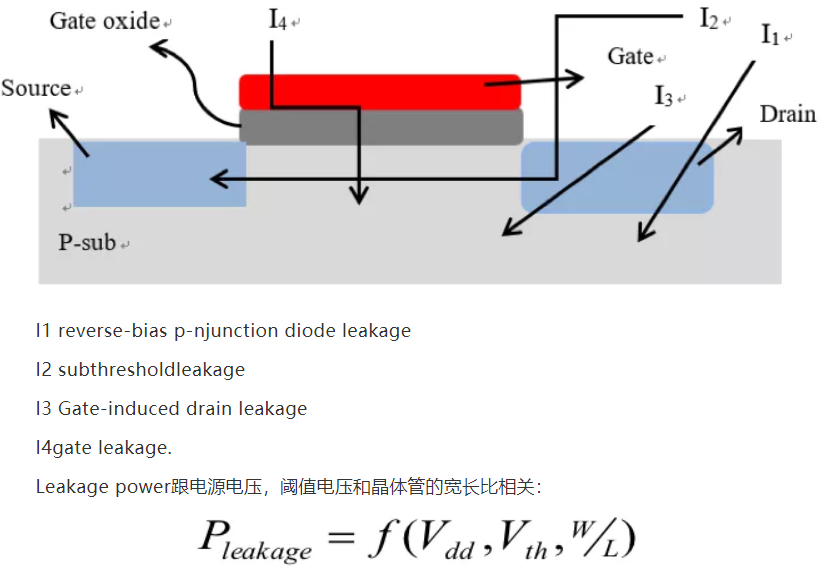

- 静态功耗,即漏电功耗(leakage power)。漏电流早期的CMOS工艺里是可忽略的,但是随着近年来器件尺寸越来越小以及阈值电压的减小使Leakage current在功耗分析中不能再被忽视。Leakage power主要由以下几个方面组成

推荐一篇论文:Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicrometer CMOS Circuits。作者是KaushikRoy.

Power Signoff

当今主流的power signoff 工具有Cadence的Voltus 和 ANSYS公司的Redhawk。限于作者工作经验,本文就基本flow 做一简单概述。

Power signoff 主要包括静态、动态功耗分析和Signal-EM分析以及基于芯片封装模型的SIPI分析等。

静态功耗分析(Static IR-drop/EM Power Analysis):这里的静态功耗分析并不是leakage 功耗,而是指一种基于芯片内部电路在直流工作模式下的功耗分析。

-

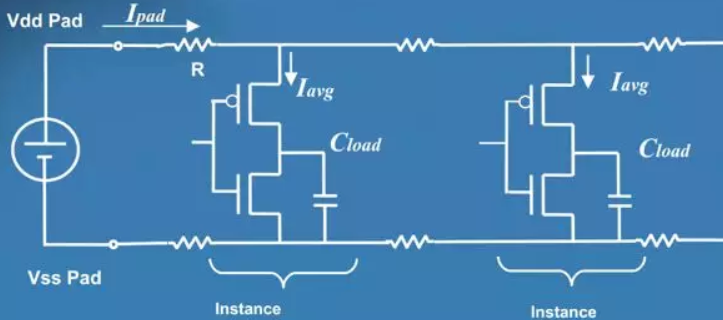

芯片上的PG网络在静态功耗分析中会近似于电阻网络

-

而且流经各个instance的电流都认为是直流电流。

|

|

-

均值电流都是在每个instance上算的,利用欧姆定律即可直接算出节点电压。电迁移值Electromigration 在电源网络分析之后会得出金属线网络的电流密度,再根据对应工艺的Tech file里对于Electromigration的极限电流密度的约束,便可以得出整个芯片的电迁移报告。报告里所有电迁移值都用百分比来表示,一般而言都是用100%来signoff芯片电迁移是否可以满足极限值。<这里涉及到不同工艺下的EM table和Chip Reliability 的内容;对于电迁移概念的理解,还有一个概念是Blech Length和Black Equation;后续会做相关分享。

-

Static IR/EM Analysis:得到芯片功耗之后,会去分析IR-drop和EM,static模式下主要check 芯片的PowerMesh 够不够强壮,有没有power/ground mesh 的short 和open;再就是memory 的channel 处standard cell 是否有足够的metal覆盖。

Static IR/EM Analysis:得到芯片功耗之后,会去分析IR-drop和EM,static模式下主要check 芯片的PowerMesh 够不够强壮,有没有power/ground mesh 的short 和open;再就是memory 的channel 处standard cell 是否有足够的metal覆盖。

动态功耗分析(Dynamic IR-drop/EM Power Analysis)

-

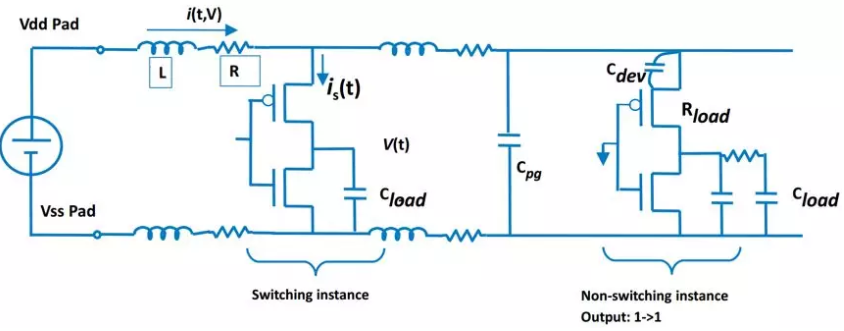

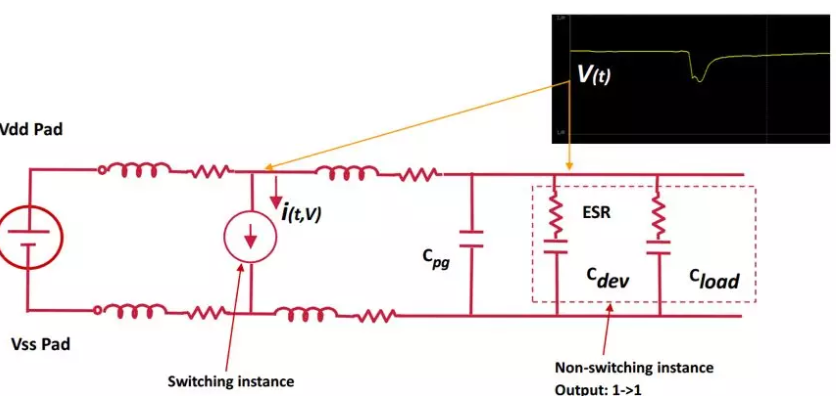

On-chip的PG mesh 被模型化成RLC网络;

-

对于有开关和状态翻转的instance cell,其电流模型是时间和电压值的函数;

-

对于没有翻转的instance cell,会分析其中有效的decoupling capacitance以及ESR (Effective Series Resistance)和leakage current。

-

每个instance的电流模型是PWL Current Model;

-

Dynamic Voltage Drop是通过在每一个电路节点的瞬态分析得到的

对于Dynamic IR-drop/EM, 要特别说一下APL file和Decoupling Capacitance。

-

APL file:通常由foundary 提供,也可以用工具自带的utility产生。APL file对于dynamic IR-drop analysis会更准确,对于device 内部的decoupling 电容可以分析进去,dynamic结果看起来更符合design实际情况。

-

Decoupling Capacitance:Decap实际上就是在Vdd和Gnd之间加入的隔离电容,可以去除很多由电源上的噪声而引起的Voltage Drop。在debug dynamic IR-drop时需要结合decap density map进行比对,看是不是这些issue points处的decap density过低。decap最好尽可能分布均匀而且在一些敏感基本单元附近有足够的decap cells。