【连载】【FPGA黑金开发板】Verilog HDL那些事儿--低级建模的基础(二)

声明:本文为原创作品,版权归akuei2及黑金动力社区共同所有,如需转载,请注明出处http://www.cnblogs.com/kingst/

第二章:低级建模的基础

2.1 顺序操作和并行操作

顺序操作和并行操作,是新手们很容易混乱的一个重点。但是为了将低级建模发挥到极限,这一点必须好好的理解。Verilog HDL 语言,虽然不同与其他高级语言的优秀结构性,但是作为硬件描述语言的它,最大的优势是并行操作。

顺序操作有如“步骤”概念,如果上一个行为没有完成,下一个行为就没有执行的意义。而并行操作最为不同的是,两个行为都是独立执行,互不影响。那么,我们从一个典型的实验“流水灯实验”,在具体上来理解它们的不同之处。

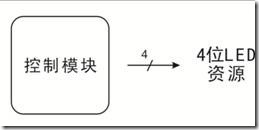

下图是两种以不同操作方式建立的“流水灯实验”。

1)点亮第一个LED,延迟一段时间。

2)点亮第二个LED,延迟一段时间。

3)点亮第三个LED,延迟一段时间。

4)点亮第四个LED,延迟一段时间。

5)重复第一个步骤。

从上面看来,我们明白“流水灯效果的产生”主要是以“顺序的方式”执行 5 个步骤。这可能是人类自然的思维方式吧,人类真的是奇怪的动物,虽然人类的大脑是并行操作的,但是人类的思维方式比较偏向“顺序操作”。为什么呢?

如果引用现实中的实例,如果四个 LED 失去了“指挥者”,那么它们就罢工了!因为它们失去“执行发号”的第二方,这样的情况就如同上面内容如果没有了“1”,“2”,“3”,“4”,“5”的数目字,那么你又如何看懂“流水灯如何产生呢?”

换一句话说,“顺序操作”的代表往往都有一个“指挥者”或者名为“控制器”东西的存在,执行着“工作的次序(步骤)”。

我相信很多学习 FPGA 的朋友都有学过单片机。学习单片机的时候,可能是 C 语言或者汇编语言的关系,所以很多朋友在不知不觉中的情况习惯了“顺序操作”这样的概念。新手们常常忽略了,FPGA 有存在着“顺序操作”和“并行操作”的概念。如果打从一开始就忽略了它们,往后的日子很难避免遇见瓶颈。

那么换成是“并行操作”的流水灯是如何的呢?结果我们从实验中理解...

实验一:永远的流水灯。

这一个实验,我们要以上图作为基础,建立一个并行操作的流水灯模块。扫描频配置定为100 Hz,而每一个功能模块在特定的时间内,将输出拉高。

示意图如下:

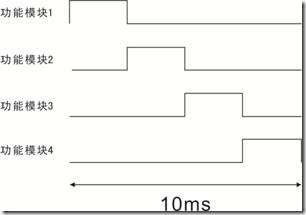

从上图我们可以看到,功能模块1在时间的第一个1/4拉高输出,功能模块2在时间的第二个1/4拉高输出,其余的两个功能模块也是以此类推。所以在一个固定的时间周期内(10ms), 每一个功能模块所占的时间都是2.5ms。

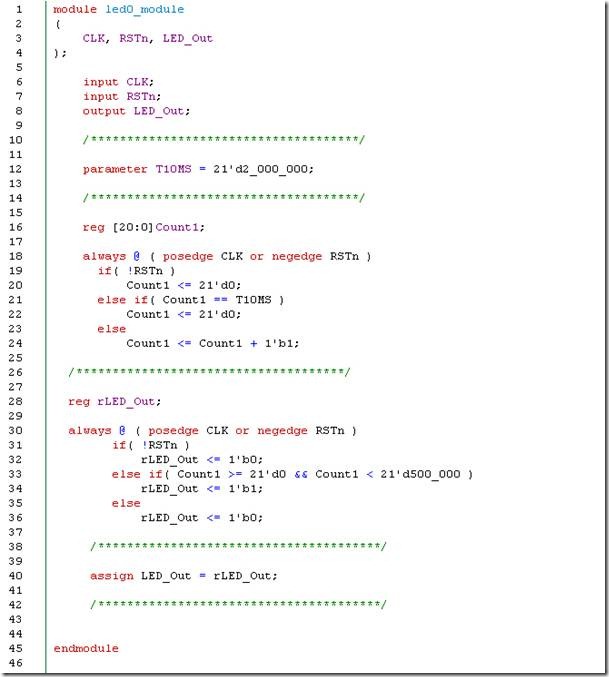

实验一源码:

实验一说明:

注:实验文件为路径 . /Experiment01/ 之下。建模过程请参考“实验一配置”。

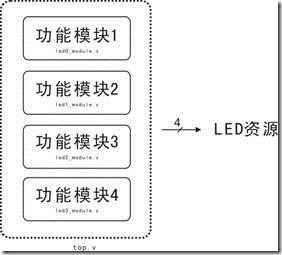

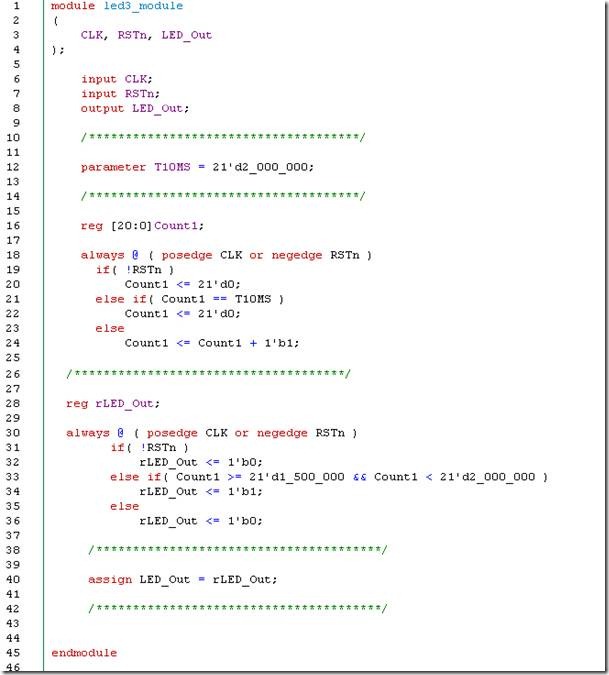

led0_module.v , led1_module.v, led2_module.v, led3_module.v,的源码都是大同小异。第12行是10ms 计数器的常量声明。第16~24行是一个计数器,计数器计数范围为10ms。而在28~36行是决定4个功能模块的不同之处。

led0_module.v 功能模块是在时间的第一个1/4 拉高输出。

led1_module.v 功能模块是在时间的第二个1/4 拉高输出。

led2_module.v 功能模块是在时间的第三个1/4 拉高输出。

led3_module.v 功能模块是在时间的第四个1/4 拉高输出。

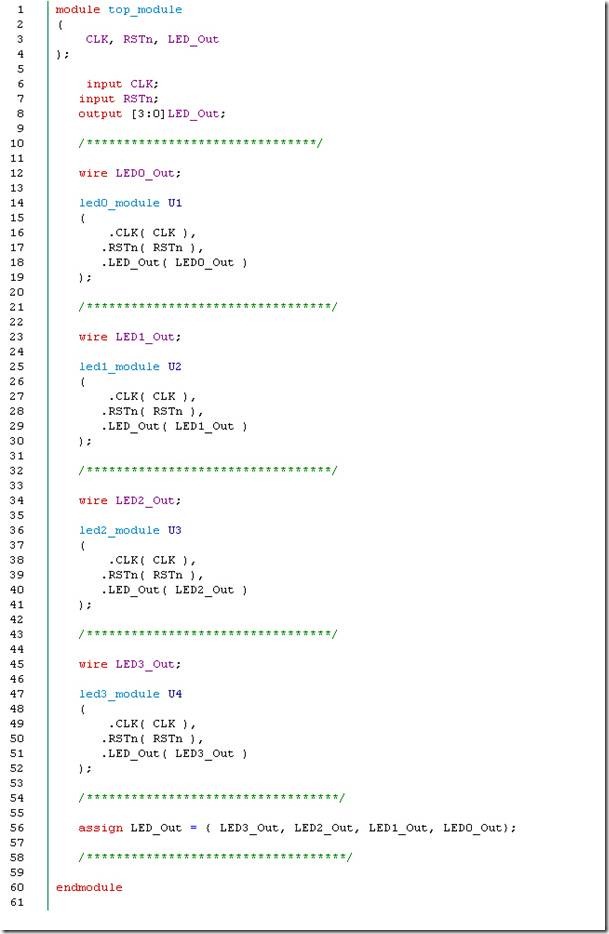

而top.v 是顶层模块,用来组织这四个功能模块。

实验一总结:

从实验的结果看来利用“并行操作”实现的流水灯,在现实的肉眼中和“顺序操作”没有任何两样。但是从“理解上”就有很大的差别。

led0_module.v 功能模块是在时间的第一个1/4 拉高输出。

led1_module.v 功能模块是在时间的第二个1/4 拉高输出。

led2_module.v 功能模块是在时间的第三个1/4 拉高输出。

led3_module.v 功能模块是在时间的第四个1/4 拉高输出。

上面的内容表示了,4个功能模块是独立操作的。由于输出在时间上不同,在肉眼中才会看到流水灯的效果。用现实的角度去思考的话,宛如有四个局内人,无不关系,各自只是按照自己的节奏完成自己的工作。在局外人的眼中,他们如同有默契般,不需要“指挥者”也能完成任务。

在这里说一点局外话。“并行操作”的建模程度虽说猥琐。但是在理解上非常适合“FPGA+Verilog HDL”的口味。平常我们在设计程序的时候,在无意识中使用了“顺序操作”的思维,如果“并行操作”也可以无意识般的使用,那么程序设计,会出现许多“可能性”。

实验一配置

黑金版的FPGA型号:CYCLONE II EP2C8Q208C8

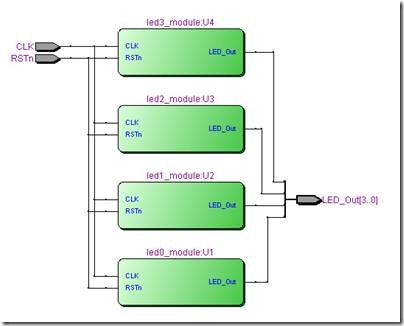

1. 实验总添加了以上左图5个.v文件。编译成功过后,层次建立会如又图。top_module文件组织

了四个其他功能模块。

2. 关于黑金版的“时钟(CLK)”和“复位(RSTn)”的电路引脚。

3. 实验一使用的硬件资源有“4位LED”

打开:Assignments => Pin Planner < Ctrl + Shift + N >

4. 引脚配置如上

5. 完成的框图

posted on 2010-08-29 10:58 FPGA黑金开发板 阅读(3603) 评论(4) 编辑 收藏 举报

![clip_image010[6] clip_image010[6]](https://images.cnblogs.com/cnblogs_com/kingst/WindowsLiveWriter/VerilogHDL_9A23/clip_image010%5B6%5D_thumb.gif)

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步