【连载】【FPGA黑金开发板】NIOS II那些事儿--NIOS II下关于无法进行寄存器方式操作PIO的问题解析(十四)

FPGA黑金开发板 by AVIC(马瑞) is licensed under a Creative Commons 署名-相同方式共享 2.5 中国大陆 License.

声明:本文为原创作品,版权归本博文作者所有,如需转载,请注明出处http://www.cnblogs.com/kingst/

最近得到大家的反馈,说用寄存器直接映射的方法不好用,点亮一个LED都不行。今天调试我的改版核心版,竟然也遇到了这样的情况。于是研究了一下,发现了问题的根源。在此给大家解释一下。

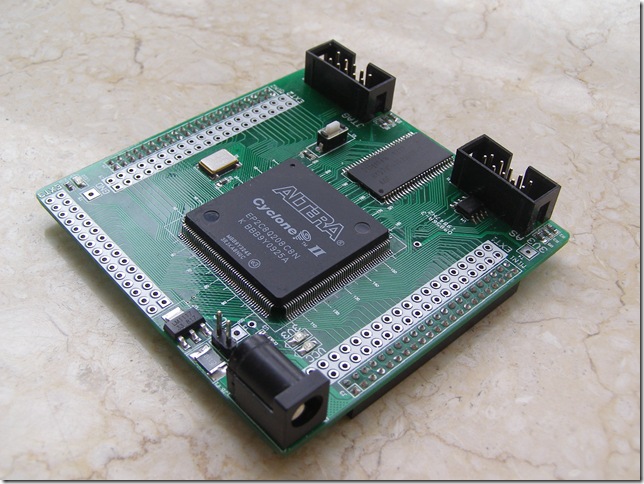

我的改版核心板用的是EP2C8,资源比我以前的EP2C5要多一些。所以,我今天我用了NIOS II/f,这个软核资源占用的最多的,但速度也是最快的,如下图所示

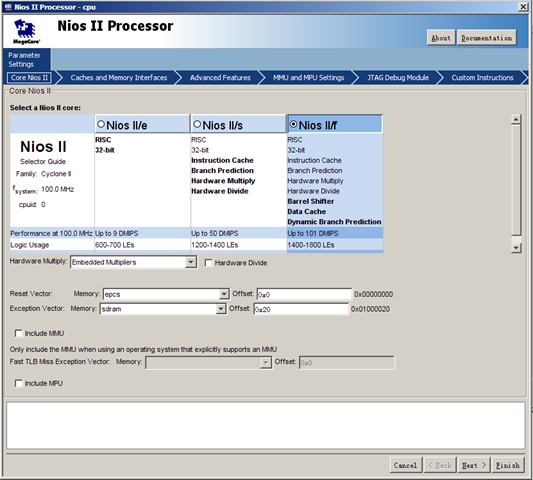

这步没有任何问题,关键是下一步,下图的红圈处,在NIOS II/f中,DATA CACHE(数据高速缓存)被打开了,在其他两种CPU中这个地方时灰的不能用的,就是说只有NIOS II/f数据高级缓存才打开的。看来就是数据高速缓存惹的祸。

那Data Cache到底是什么呢,芯片手册上是这样介绍的,(引自《n2cpu_nii5v1.pdf》的2-12页)

Cache memory resides on-chip as an integral part of the Nios II processor core. The cache memories can improve the average memory access time for Nios II processor systems that use slow off-chip memory such as SDRAM for program and data storage.

简单的说,Data Cache是像电脑的一级缓存二级缓存一样的东东,就是为了提高系统速度的。可是有个这个高速缓冲区后,我们的代码执行时间却变得不可确定了,降低了程序的实时性。我们发出的数据,放到了高速缓冲区里而没有及时的去执行才导致代码不执行,没有显示效果。想要了解Cache memory相关内容的可以参考http://www.altera.com/literature/hb/nios2/n2sw_nii52007.pdf

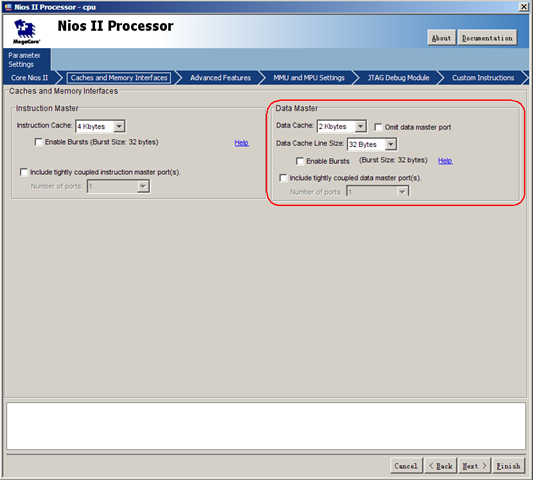

既然知道原因了,那我们该如何解决呢。方法有两个:

第一种就是在建立NIOS II/f的时候,将Data Cache设置为0,就是说关闭Data Cache。如下图所示,这样就不存在Dache Cache了,这个办法彻底吧,这就叫斩草除根,呵呵!

第二种是在开启了Data Cache前提下,通过软件来解决。http://www.altera.com/literature/hb/nios2/n2sw_nii52007.pdf这里面有所介绍,就是通过31-bit Cache bypass。什么意思呢,很简单,NIOS II将寄存器的第31位作为了Cache 开启与否的控制位,如果此位为1,则Cache关闭不启用,否则就开启。一般情况我们是不会注意到这个的,所以才会出现无法控制LED的情况。我们把最简单的程序修改一下,如下所示

#include <unistd.h> #include "system.h" #define LED *(volatile unsigned long *)(LED_BASE | (1 << 31) //这个地方要注意了,多了(1<<31),这就是bypass Cache,关闭Cache

int main(void)

{

while(1){

LED = 1;

usleep(100000);

LED = 0;

usleep(100000);

}

return 0;

}

两种方法都讲完了,我更推荐第一种,斩草除根式。大家要注意,只有使用NIOS II/f这种类型的CPU才会出现这种问题。

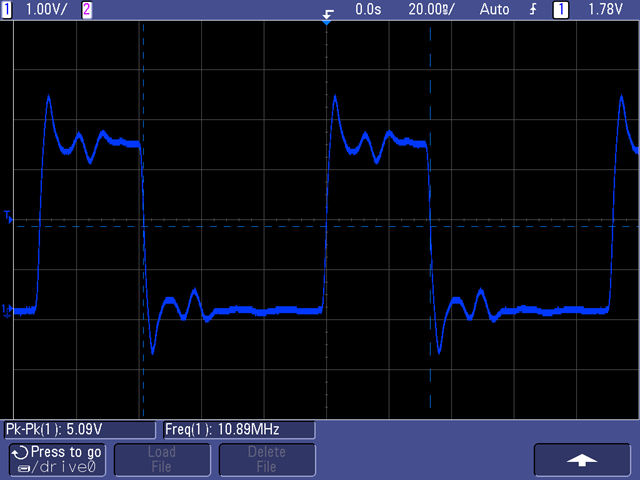

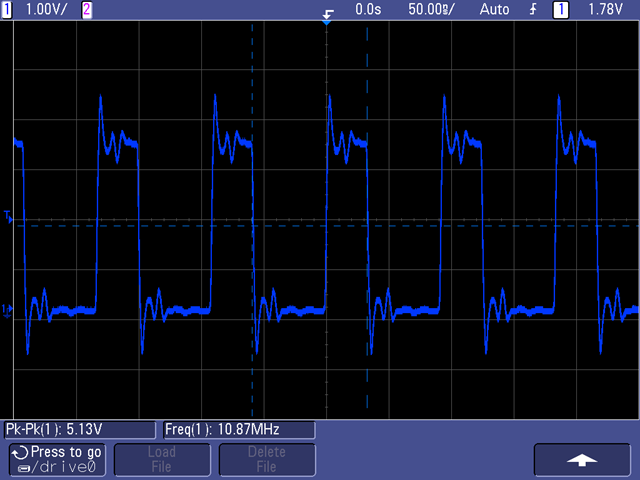

新的核心板测好以后,顺便测了下IO速度,给大家看看吧,测下来IO频率不到11MHz,呵呵

CPU:NIOS II/f

时钟:120MHz

示波器:Agilent mso6032a 300MHz 2GSa/s

浙公网安备 33010602011771号

浙公网安备 33010602011771号