【连载】【FPGA黑金开发板】NIOS II那些事儿--硬件开发(一)

声明:本文为原创作品,版权归黑金动力社区(http://www.heijin.org)所有,如需转载,请注明出处http://www.cnblogs.com/kingst/

从今天开始,NIOS的学习征途正式拉开了。对于NIOS的学习爱好者,我相信这是一个福音,我将毫无保留的将我对NIOS的研究成果分享给大家。我之所以采用博客这种方式,就是想跟大家充分的交流,大家可以给我留言,也可以在Ourdev中提出问题,我将尽我的全力为大家解决问题。由于本人水平有限,如果有我解决不了的问题,还请高手们多多帮忙,我相信能为大家解决问题是一件很快乐的事情,你不会错过的。

废话少说,我们马上进入正题。今天是第一节,我首先说一下学习NIOS都需要哪些前提条件。听到这,初学者可以会有些害怕了,难道学习NIOS还要条件?是的,需要条件,不过这些条件并不是很高,只要大家努力,这些条件都不是问题。

- 具有一定的单片机基础;

- 具有一定的C语言编程能力;

- 了解Quartus II的开发流程;

- 一块开发板;

就这么多,大家觉得难么?首先说说第一条,具有一定的单片机基础,这个条件是要有的。单片机的基础在NIOS II学习中体现在它的寄存器操作方式上,这种操作方式是通用的,不管是ARM,DSP,还是51都是一样的,你只要有一种单片机的实践经验就没问题了。再说第二条,这一条没什么可争议的,NIOS的开发完全是用C语言的,如果你没有C语言的基础,我建议你还是先学习一下C语言再考虑学习NIOS吧。第三条呢,有最好,如果没有的话也可以,我在以后的文章中都会涉及到,大家跟着学就可以了。第四条也不是必须的,不过学习NIOS不像学习Verilog/VHDL,通过仿真看看也行,NIOS的学习跟单片机很相似,最好是亲手操作硬件,这样对你的学习有更好的效率和效果。在这里推荐一下我的FPGA黑金开发板,不仅仅是广告哦,因为我以后的讲解都是以我的黑金板为基础的,大家学习起来也很方便的。

简介

NIOS是一个用户可配置的通用32位RISC嵌入式处理器,它是SOPC(System On a Programmable Chip,片上可编程系统)的核心。处理器以软核形式实现,具有高度的灵活性和可配置性。NIOS的开发包括硬件开发和软件开发两部分。硬件开发是在Quartus II中实现的,而软件开发部分是在NIOS IDE软件中实现的。我们首先来介绍NIOS的硬件开发。所谓硬件开发就是用Quartus II 和 SOPC builder来建立自己需要的软核。

软件版本:本教程基于Quartus II 9.0,NIOS IDE 9.0编写

建立工程

首先,打开Quartus II 9.0软件

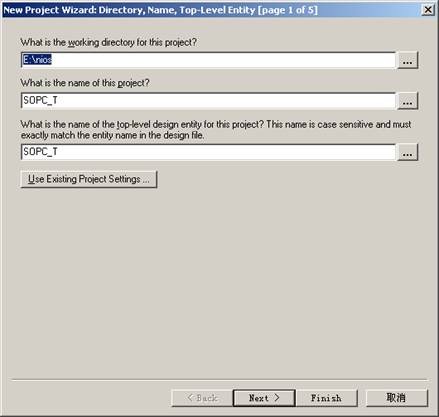

接下来,建立一个工程File->New Project Wizard

第一行是工程的路径,你选择你放置的路径即可。

第二,第三行都是是工程名,写好以后如下

点击Next,

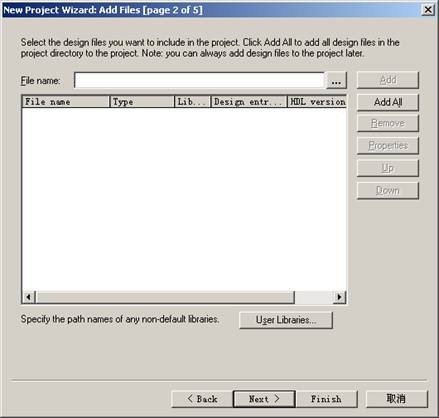

这个不用动,接着点击Next

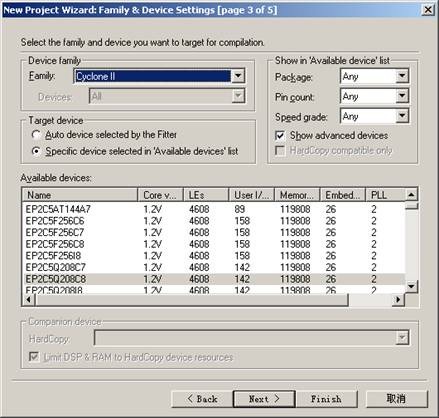

在这里,Family里选择Cyclone II,在Available devices中选择EP2C5Q208C8(具体内容根据你的芯片所定)。如上图所示。

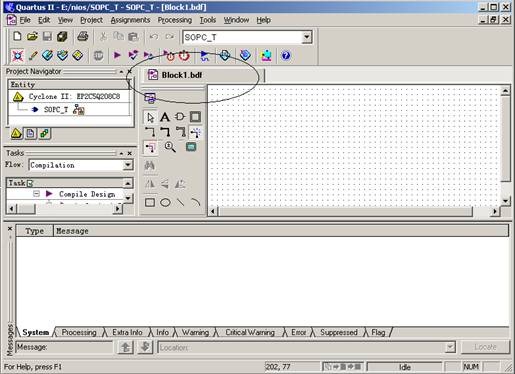

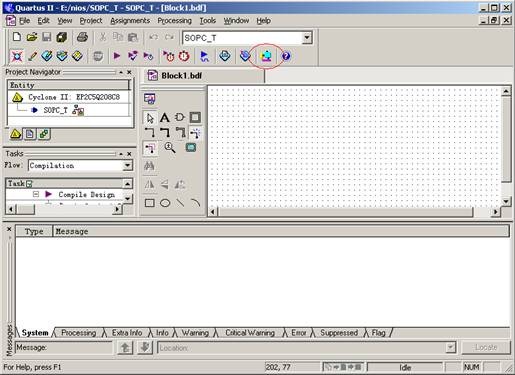

接着点击Next,不用动,点击Finish,显示如下图所示。

到此为止,工程已经建立完成。接下来,需要建立一个Block Diagram/Schematic File,点击File->New,如下图所示

点击OK,完成建立,工程中出现了一个Block1.bdf文件

建立NIOS II软核

接下来,我们进入了软核建立环节,这一步很重要,是建立软核的核心步骤。点击Tools->SOPC Builder或者下图红圈标示的图标

点击以后,SOPC Builder运行,界面如下图示

System Name中输入软核的名字:我将其命名为KERNEL。点击OK后,如下图所示

按图中标注的,clk_0为时钟名称,50.0为时钟值(单位为MHz),我们可以对他们进行修改。用鼠标点击50.0,将其改为100.0。这时候,我们的软核时钟就为100.0MHz了。这是软核建立的第一步,接下来,我们要建立Nios II Processor。

建立CPU

用鼠标点击左侧边框的Nios II Processor,如下图红框所示

点击后,将出现下图

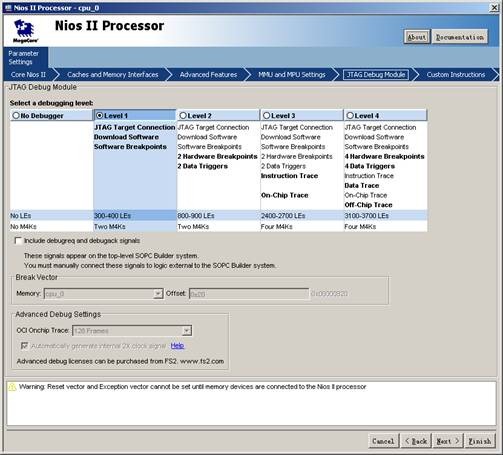

这一步我们来选择软核的类型。这里给我们提供了三种类型,Nios II/e占用资源最少600-800LEs,功能也最简单,速度最慢。Nios II/s占资源比前者多一些,功能也多了,速度也快一些Nios II/f占资源最多,功能也最多,速度就快。选择的时候要根据你的需求和你的芯片资源来决定。在这里,我选择Nios II/s,功能和速度都可以得到满足。下面的Reset Vector是复位后启动时的Memory类型和偏移量, Exception Vector是异常情况时的Memory类型和偏移量。现在还不能配置,需要SDRAM和FLASH设置好以后才能修改这里,这两个地方很重要。接下来连续点击Next,一直到下图为止

这里设置JTAG Debug Module,即JTAG调试时所用到的功能模块。功能越多,需要的资源越多,这里,我们选择Level 1即可,不需要过多其他的功能。点击Finish,结束Nios II Processor的建立后,如下图所示

建立SDRAM模块

接下来,我们要建立SDRAM控制器,点击下图红框所示的地方

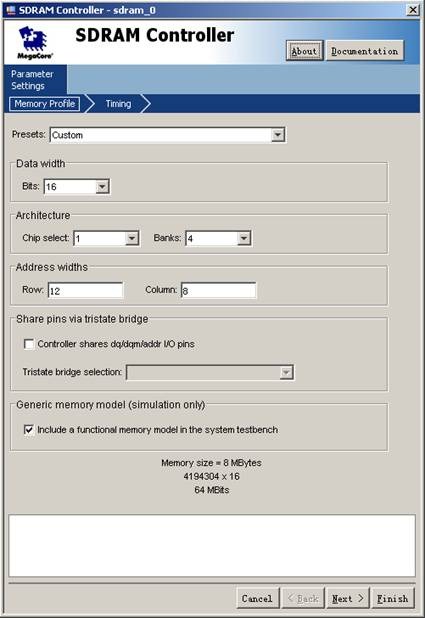

点击后,如下图所示

在Presets中选择第一项Custom,在Bits中选择16,其他项不动,点击Next,点击Finish,完成SDRAM控制器的设置。在这里之所以选择16,是因为我们用的SDRAM(HY57V641620)是16位的。

建立Avalon三态桥

接下来,我们要建立一个Avalon三态桥,在NIOS系统中,要实现与FPGA片外存储器通信,就必须在Avalon总线和连接外部存储器的总线之间添加一个桥,这个桥就是Avalon三态桥。点击下图所示红圈处

点击后,如下图所示

点击Finish后,完成三态桥的建立。

建立CFI模块

接下来,我们就建立Flash Memory Interface(CFI)模块,点击下图所示红圈处

点击后,如下图所示

其中Presets,我们选择Custom,Address Width(bits)是地址线宽度,我们选择21,Data Width(bits)数据线宽度,我们选择8位。这些的选择都是根据芯片和电路设置决定的,我们的FLASH(AM29LV1602)可以选择为8位模式和16位模式,我在设计电路的时候将其配置为8位模式,所以在此数据线宽度选择为6位,地址线宽度选择为21位。设置好以后,点击Next,出现下图所示

这里,我们需要设置三个量,Setup,Wait,Hold,我们分别将其设置为40,160,40如上图所示。这些量都是根据FLASH的芯片决定的,各个芯片都不一样,在此不具体讲了。点击Finish后,完成Flash Memory Interface(CFI)的建立。到此为止,我们已经建立了CPU,SDRAM,FLASH模块,接下来,我们还要添加一些必要的模块,System ID,JTAG UART。

建立SYSTEM ID

System ID就是一种标示符,类似校验和的这么个东西,在你下载程序之前或者重启之后,都会对它进行检验,以防止错误发生,大家知道这个东西就可以了,没太大的用处,但需要有的。点击下图所示红圈处

点击后下图所示

点击Finish,完成System ID的建立。

建立JTAG UART

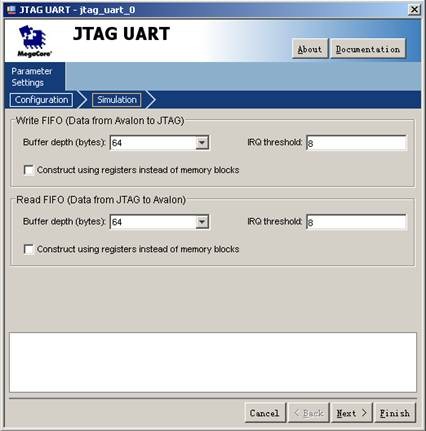

JTAG UART是实现PC和Nios II系统间的串行通信接口,它用于字符的输入输出,在Nios II的开发调试过程中扮演了重要的角色,接下来我们开始建立它的模块。点击下图所示红圈处,

点击后,如下图所示

什么都不用修改,直接点击Next->Finish完成 JTAG UART模块的建立。到此为止,最基本的NIOS系统模块就建立完成了,如下图所示

配置及编译NIOS II

我建议大家将他们的名字都改一下,将_0都去掉,看着别扭,鼠标右键点击相应名字,Rename就可以修改了。我们离成功已经很近了,再进行几步处理以后,我们就可以编译了 ,大家加油吧。大家看下图红圈处

cfi_flash还没有跟tristate_master连接,当我们把鼠标移到红圈处位置时,就出现了下图所示的情况

这时候,我们用鼠标点击红圈处的空心圆,这时候奇迹出现了,呵呵,如下图所示

空心圆变成了实心圆,这就完成了cfi_flash与三态桥的连接,大家亲手试试吧。接下来我们需要对cpu进行设置一下,双击cpu,Reset Vector处的Memeory选择cfi_flash,Exceptioni Vector选择sdram,其他不变,如下图所示出现下图所示

点击Finish,完成cpu设置。

接下来,我们需要对FLASH地址进行锁定,保证FLASH的起始地址为0x00000000,因为FLASH是系统重启后的起始位置,这样做的好处就是有利于我们操作,系统重启后从0x00000000开始也是我们的思维习惯。点击系统所示的红圈处

点击后,奇迹又出现了,看看下图吧

开着的锁合上了,ALTERA还真逗啊。

最后一步设置就是对地址自动分配,这样做是为了不浪费空间,如果有特殊要求的,也可以手动设置,点击相应的地址,就可以手动修改了,大家自己试试吧。地址自动分配操作如下,点击下图所示红圈处,SYSTEM->Auto-assign Basic Addresses

点击后,大家可以发现,各个模块的地址都有相应的变化,但CFI_FLASH基地址还是0x00000000,锁定的还算成功啊,呵呵!接下来是中断的自动分配,和地址自动分配一样,SYSTEM-> Auto-assign IRQs,如果有什么特殊需要,可以手动更改中断的优先级。之所以要自动分配一下,是因为这个软件还不够智能,当模块建好以后,有出现重复中断号的现象,编译的过程就会出现问题,自动分配了以后就不从上自下按顺序排列了。你还会发现,图片上出现的红叉也都消失了。展现我们的劳动成果最后的样子,红叉没有了吧,这时候我们就可以编译了。

点击Next,出现下图,如果需要仿真的,点击红圈处,将其选中,我一般不进行仿真,此处就不选了。

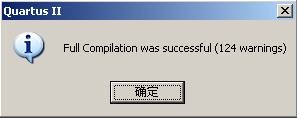

点击Generate,我们就开始编译了。想休息的赶紧休息一下,想去WC也快去吧,时间还充裕,呵呵……经过漫长的等待以后,我们的程序终于编译好,请看下图红圈处,看到successful了么?只要看到他就没问题了,软核已经好编译好了,点击Exit,回到了Quartus界面。

分配管脚

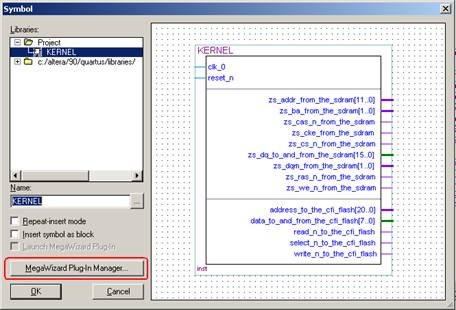

回到Quartus界面以后,在Block1.bdf界面里在空白处双击左键,会出现下图,看多了下图红圈处的地方了么,这个就是我们做好的NIOS II软核了,用鼠标双击它(或者选中以后点击OK)后,将其放到Block.bdf的空白处。

放好以后,如下图所示

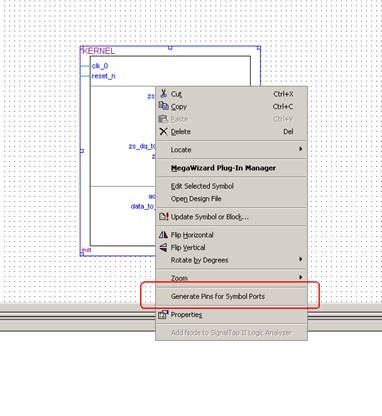

在NIOS软核KERNEL上点击右键后点击Generate Pins for symbol ports,这一步作用就是生成管脚,通过命名以后分配真是的引脚。

点击后,如下图所示,

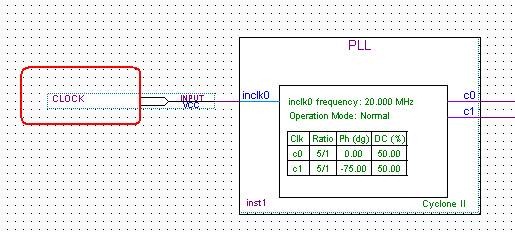

建立锁相环PLL模块

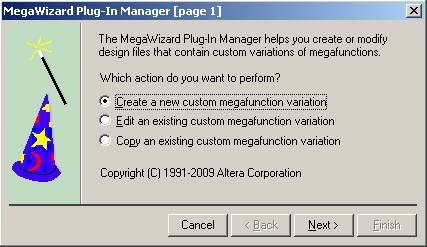

接下来的工作我们还需要建立一个锁相环,对时钟进行倍频,我们板子上是20MHz的有源晶振,我们要将其倍频到100MHz满足我们之前设定的NOIS软核的时钟,还需要为SDRAM提供100MHz的时钟。下面我们就开始锁相环PLL模块。在Block.bdf的空白处双击鼠标,点击下图所示的红圈处

出现下图后点击Next

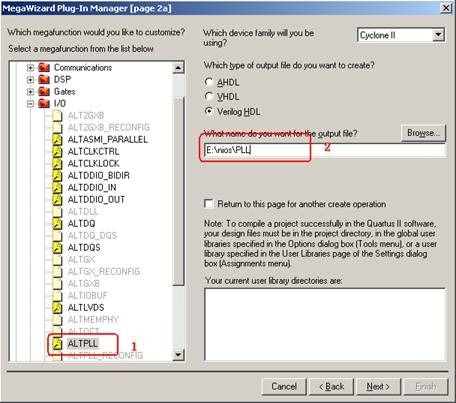

出现下图所示,用鼠标选中红圈1所在的位置ALTPLL,在红圈2所在的位置处,加上PLL,目的是将我们所要建立的锁相环命名为PLL。

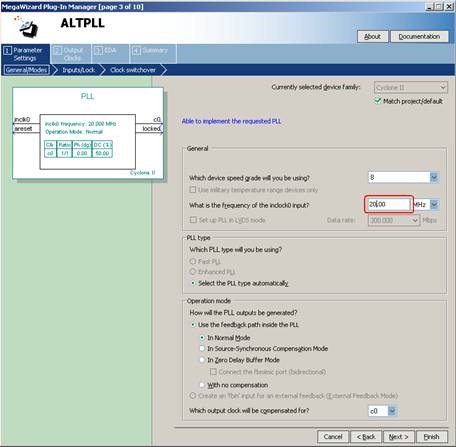

一切弄好以后,点击Next,如下图所示,将红圈处设置为20,即我们输入的晶振为20MHz

设置好以后,点击Next,将下图中选中的地方去掉后,

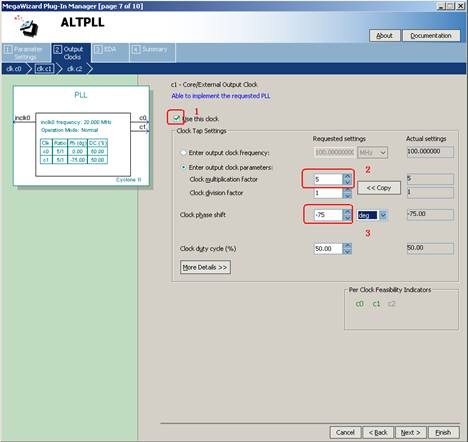

连续点击Next,等出现下图以后,将红圈处设置为5,这是c0输出的频率就设置为了100MHz,可以从Actual settings处看出来。

设置好以后点击Next,出现下图,将红圈1处选中,红圈2处修改为5,红圈3处修改为-75。这部分是给SDRAM提供时钟,我们利用锁相环PLL的c1来提供,时钟频率设置为100MHz,偏移量为-75deg(这个地方影响到SDRAM是否正常运行,我们将在以后具体讲述他的设置,在这里不详述了)。

设置好以后,连续点击Next,中间没有需要修改的,最后点击Finish,完成PLL的建立,然后点击OK,回到Quartus界面,将我们建好的PLL放到空白处。接下来的工作就是将PLL连接到NIOS软核上。如下图所示(连线方式很简单,大家自己研究一下,我就不具体说了)

接下来我们要给SDRAM的时钟分配引脚,这个就由c1完成了。首先是加一个output引脚,方法很简单,在空白处双击,出现下图,在Name处输入output,一个回车,OK了。假如你要加入input,即输入引脚,你就在Name处输入input,还有双向引脚的是bidir,常用的就这几个,大家记住了就可以了,很简单。

将其放到下图红框所示位置,连好线就OK了

调整FLASH引脚

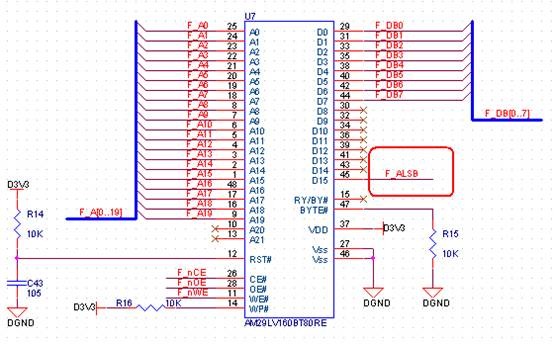

接下来,我们要对Flash连接做一下处理,因为是8位模式的解法,所以FLASH的21位地址线的最低位要跟F_ALSB相连,如下图所示红圈处,(下图为FLASH的原理图,8位模式的时候,BYTE#引脚下拉,16位模式的时候则需要上拉,请大家注意)

那么,我们就来修改一下,修改结果如下图所示

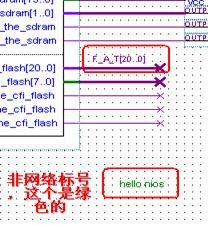

这里,需要注意红圈处的改动,将软核输出命名为F_A_T[20..0],F_A[19..0]连接的是F_A_T[20..1],F_ALSB连接的是F_A_T[0],不知大家是否能看的懂。这个地方命名方式是这样的,点击想命名的线,当被选中后,直接输入你想输入的网络标号即可,大家自己试试吧,很简单。大家要注意一下,网络标号的颜色跟线的颜色是一样的,而文字的颜色是绿色的,大家要区分开,如下图所示

TCL脚本文件

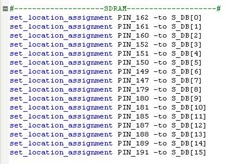

接下来就要开始分配引脚了,分配引脚有两种方式,在这里我只讲一种,也是我觉得比较好的一种,就是通过TCL脚本文件,这个文件有固定的写法,只要根据你的引脚情况修改一下就可以了,如下图示所示

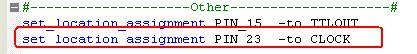

我们要命的名字就是后面那部分,PIN_*是FPGA硬件上的引脚,S_DB[*]就是对应的名字。下面我们举例说明一下吧我现在修改时钟管脚,如下图所示,将其命名为CLOCK,咱们再来看对应的TCL脚本文件

我们可以看到,CLOCK是对应PIN_23,我们再来看原理图

我们可以看到,下面的原理图中20MHz晶振X1接的就是FPGA的23脚

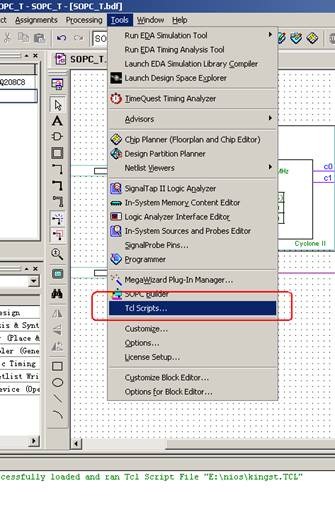

这回大家知道是怎么回事了吧,我将会提供给大家写好的TCL文件,到时候大家根据我给大家的TCL文件,将相应的管脚命名即可。下面我就将其他的管脚重命名,这是个繁琐的工作,很无趣。修改好以后,我们来看如何执行TCL脚本文件,按下图所示操作

点击以后,出现下图,我们选择第一个(前提是你将kingst.tcl放到工程文件下)

选中后点击Run,如下所示,又看见Successfully了吧,这说明我们脚本文件运行成功了。

配置工程

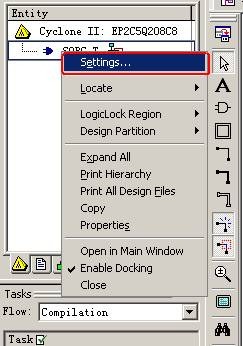

先保存一下吧,保存好以后,接下来,我们要对工程配置一下了,在左侧边框栏右键点击SOPC_T,如下图所示

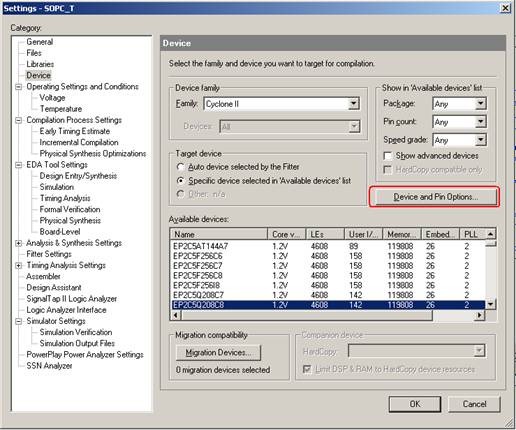

点击setting后,如下图所示,点击红圈处Device and Pin Options

点击后,如下图所示

点击后如下图所示,点击红圈处Configuration

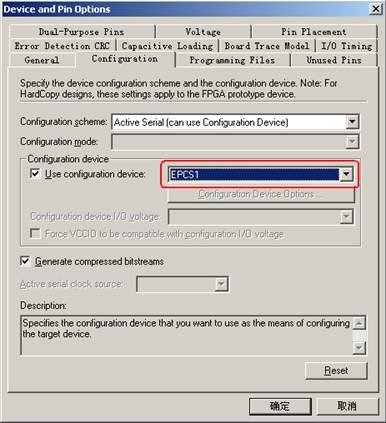

点击后,如下图所示,将红圈处改为EPCS1,然后点击Dual-Purpose Pins

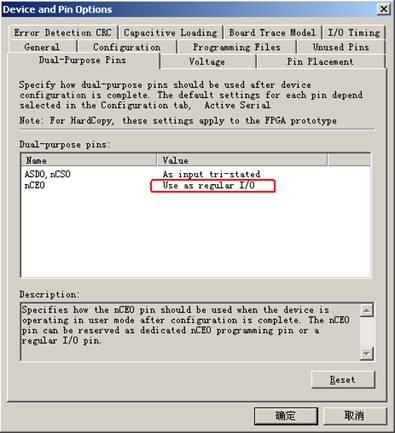

点击后,如下图所示,将红圈处改为Use as regular I/O

都修改好以后,点击确定,点击OK。接下来就开始了又一个漫长的编译过程了,大家又可以休息一会了。点击下图所示红圈处的按钮,开始编译。

经过了漫长的编译过程,如果没有问题,编译成功后将出现下面的对话框

点击确定,编译过程全部结束。我们可以通过编译报告来看看我们用了多少资源,如下图所示,红圈处可以看出,我们这个系统,用了66%的TLE。

最后,我们需要检查一下,是否每个引脚都已经分配好了,以免有个别没有分配的,影响后面的实验。回到SOPC_T.bdf,看一看是不是每个引脚都有个小“尾巴”,如下图所示

有的,说明这个引脚已经分配好了,仔细检查好每一个引脚,如果没有问题,就可以把程序下载到硬件里面了。

下载程序

编译好以后的程序会生成两种格式的文件*.sof和*.pof,*.sof文件是给通过JTAG模式下载到FPGA内部的,掉电丢失。*.pof文件是通过AS模式下载到EPCS1中的,掉电不会丢失。说到这,简单介绍一下AS模式和JTAG模式。Cyclone系列的FPGA使用SRAM单元来存储配置数据。SRAM是易失性的,每次上电之前,配置数据必须重新下载到FPGA中。Cyclone FPGA的配置方式包括:主动配置模式(AS),被动配置模式(PS)以及JTAG配置模式。我的黑金板上配置了AS和JTAG两种模式,我们通过AS口可以将程序下载到EPCS1中,如下图操作方式,点击红圈处的图标

点击后,进入下图所示界面,红圈1是模式选择,红圈2是下载器的选择,红圈3加入相应的文件。如果你通过JTAG口下载程序,就要将下载线接到JTAG口,选择JTAG模式,将*.sof文件加入到这里面。如果你通过AS口下载程序,你就要将下载线接到AS口,选择AS模式,将*.pof文件加入到这里,大家自己试试吧。最后点击Start,开始下载。现在市面上的下载线以USB-BLASTER为主,价格各有不同,贵的有200多的,便宜的50多块钱,我觉得可以用就行,贵的未必好,自己的看法啊,大家自行选择吧。

到这里,我们有关硬件开发的部分就高一段落了,如果对以上内容有问题,请大家留言,我将尽快给大家解决。

下一节,我将给你讲解NIOS II软件开发部分内容,敬请关注……

posted on 2010-03-24 18:45 FPGA黑金开发板 阅读(15638) 评论(14) 编辑 收藏 举报

![clip_image002[10] clip_image002[10]](https://images.cnblogs.com/cnblogs_com/kingst/WindowsLiveWriter/FPGANIOSII_10578/clip_image002%5B10%5D_thumb.jpg)