20135306黄韧 信息安全系统设计基础第四章学习总结

第四章 处理器体系结构

4.1 Y86指令集体系结构

程序员可见的状态

·释义:Y86程序中的每条指令都会读取或修改处理器状态的某些部分。

Y86→IA32

·8个程序寄存器

%eax,%ecx,%edx,%ebx,%esi,%edi,%esp ,%ebp

·存储器

释义:从概念上来讲就是一个很大的字节数组,保存着程序和数据。

·Y86指令

见书中图片

·Y86指令的更多细节

*IA32的movl指令分成了4个不同的指令:irmovl、rrmovl、mrmovl和rmmovl,分别显示地指明源和目的的格式。

PS:源可以是立即数(i),寄存器(r)或存储器(m)

指令名字的第一个字母就表明了源的类型,第二个字母指明了目的类型。

△同IA32一样,不允许从一个存储器地址直接传送到另一个存储器地址,也不允许将立即数传送到存储器。

*四个整数操作指令:addl、subl、andl、xorl。

*七个跳转指令:jmp、jle、jl、je、jne、jge、jg。

*六个条件传送指令:cmovle、cmovl、cmove、cmovne、cmovge、cmovg

*call指令将返回地址入栈,然后跳到目的地址。

*push1和pop1指令实现了入栈和出栈。

*halt指令停止指令的执行。

指令编码

·每条指令的第一个字节表明指令的类型。这个字节分为两个部分,每部分四位:高4位是代码部分,低4位是功能部分。

·8个程序寄存器中每个都有相应的0~7的寄存器标识符。

·程序寄存器存在CPU中的一个寄存器文件中,这个寄存器文件就是一个小的、以寄存器ID作为地址的随机访问存储器。

PS:有的指令只有一个字节长,而有的需要操作数的指令编码就更长一些。

有些指令需要一个附加的4字节常数字,这个字能作为irmovl的立即数数据,rmmovl和mrmovl的地址指示符的偏移量,以及分支指令和调用指令的目的地址。

△指令集的一个重要性质就是字节编码必须有唯一的解释。

Y86异常

- 状态码stat,停止执行指令。

4.2逻辑设计和硬件控制语言HCL

- 在硬件设计中,用电子电路来计算对位进行计算的函数,以及在各种存储器元素存储位。

- 一个数字系统需要三个主要的组成部分:1、计算对位进行操作的函数的组合逻辑。2、存储位的存储器元素。3、控制存储器元素更新的时钟信号。

逻辑门

- 逻辑门是数字电路的基本计算元素。他们产生的输出,等于他们输入位值的某个布尔函数

- And && or|| not!

组合电路和HCL布尔表达式

- 将很多的逻辑门组合成一个网,就能构成计算块,称为组合电路。

- 两条限制:

+两个或多个逻辑门的输出不能连接在一起。

+这个网必须是无环的。 - 字级的组合逻辑电路和HCL整数表达式

- 执行字级计算的组合电路根据输入字的各个位,用逻辑门来计算输出字的各个位。

- 在HCL中,我们将所有字级的信号都声明为int,不指定字的大小。HCL允许比较字是否相等。

- 画字级电路的时候,我们用中等粗度的线来表示携带字的每个位的线路,而用虚线来表示布尔信号结果。

- 组合逻辑电路可以设计成在字级数据上执行许多不同类型的操作。

集合关系

- 将一个信号与许多可能匹配的信号做比较,以此来验证正在处理的某个指令代码是否属于某一类指令代码。

存储器和时钟

- 为了产生时序电路。

- 时钟寄存器:存储单个位或字。时钟信号控制寄存器加载输入值。

- 随机访问存储器:存储多个字,用地址来选择该读或该写哪个字。

4.3 Y86的顺序实现

- SEQ处理器

将处理组织成阶段

- 1.阶段

取指→译码→执行→访问→写回→更新PC

- 2.OPl(整数和逻辑运算),rrmovl(寄存器-寄存器传送)和irmovl(立即数-寄存器传送)类型的指令所需的处理。

- 3.rmmovl和mrmovl所需要的处理。

- 4.处理pushl和popl指令所需的步骤。

- 5.跳转,call和ret三类控制转移指令的处理。

SEQ硬件结构

- 1.实现SEQ的画图惯例:(见书中图示)

(1)浅灰色方框表示硬件单元。

(2)控制逻辑快是用灰色圆角矩形表示的。

(3)线路的名字在百色椭圆中说明。

(4)宽度为字长的数据连接用中等粗度的线表示。

(5)宽度为字节或更窄的数据连接用细线表示。

(6)单个位的连接用虚线来表示。

SEQ的时序

- 1.SEQ的实现包括组合逻辑和两种存储器设备:

(1)时钟寄存器-程序计数器和条件码寄存器。

(2)随机访问存储器-寄存器文件,指令存储器和数据存储器。

(3)剩下四个:

- 条件码寄存器:只在执行整数运算指令时装载

- 数据存储器:只在执行rmmovl、pushl或call时写入

- 寄存器文件:两个写端口允许每个时钟周期更新两个程序寄存器。

- 特殊寄存器:0xF表示此端口不应执行写操作。

SEQ阶段的实现

- 在控制逻辑中必须被显式引用的常数:

(1)nop指令:PC+1,别的只经过不改变。

(2)halt指令:使处理器状态变为HLT,导致停止运行。

- 1.取指阶段:

以PC为第一个字节,读6个字节。

(1)两个逻辑块:

- 指令代码:icode

- 指令功能:ifun

(2)三个一位的信号

- instr_valid:发现不合法的指令.

- need_regids:包含寄存器指示符字节吗

- need_valC:包括常数字吗

- 2.译码和写回阶段

都需要访问寄存器文件,根据四个端口的情况,判断应该读哪个寄存器产生信号valA、valB

- 3.执行阶段

(1)包括算术/逻辑单元ALU,输出的是valE。

(2)包括条件码寄存器。

- 4.访存阶段

(1)读或者写程序数据。

(2)根据icode,imem_error,instr_valid,dmem_error,从指令执行的结果计算状态码Stat。

- 5.更新PC阶段

会产生程序计数器的新值。

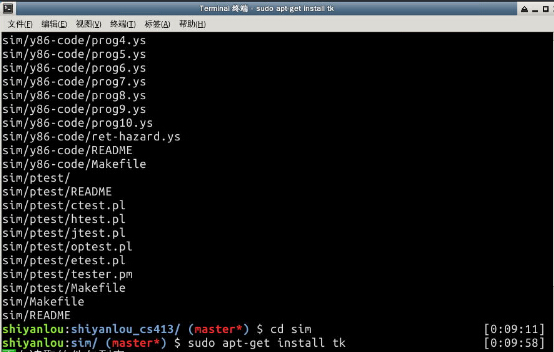

实验

构建YIS环境:

cd ~/Code/shiyanlou_cs413

wget http://labfile.oss.aliyuncs.com/courses/413/sim.tar

tar -xvf sim.tar

cd sim

sudo apt-get install tk

sudo ln -s /usr/lib/x86_64-linux-gnu/libtk8.6.so /usr/lib/libtk.so

sudo ln -s /usr/lib/x86_64-linux-gnu/libtk8.6.so /usr/lib/libtk.so

make

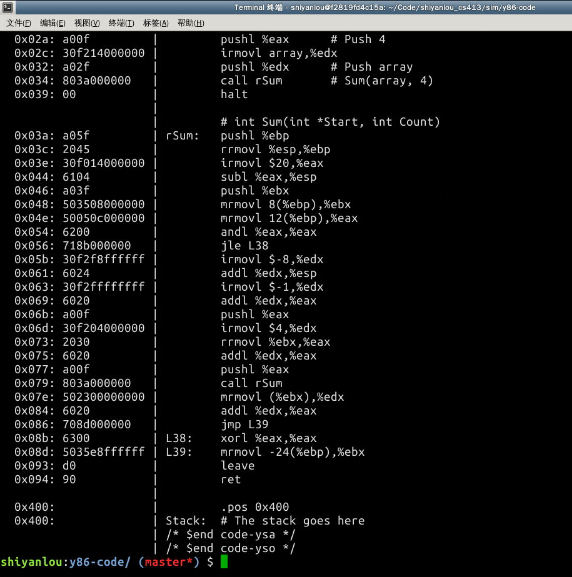

YIS测试:

cd y86-code

进入测试代码,教材p239页代码为asuml.ys,可以通过

make asuml.yo

进行汇编,asuml.yo就是汇编后的结果,见教材p238。

make all

可以汇编运行所有代码结果。

参考资料

- 教材:第四章《处理器体系结构》,详细学习指导:http://group.cnblogs.com/topic/73069.html

- 课程资料:https://www.shiyanlou.com/courses/413 实验五,课程邀请码:W7FQKW4Y

- 教材中代码运行、思考一下,读代码的学习方法:http://www.cnblogs.com/rocedu/p/4837092.html。