最近画了一块基于EP3C10E144C8N的数据采集卡,由于EP3C10和EP3C5引脚和内部配置全兼容,只是逻辑单元数量不同,所以我下面说得情况同样适用于EP3C5.

以前用过EP2C8的板子,感觉cyclone2和cyclone3代的最大区别就是电压等级降低了,核心电压为1.2V.这也是为了实现cyclone3所标榜的低功耗,在硬件设计方面,和cyclone2代没有太大的区别,cyclone3代的FPGA,引脚IO口电平可以配置为2.5V等更低的电平,但是我在应用中还是配置为了3.3V,因为毕竟外围的芯片,还是以3.3V和5V逻辑的居多.

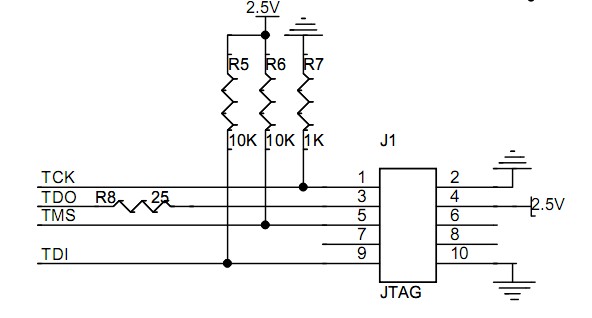

由于系统中多出了一个2.5V,所以在JTAG口的处理上,需要特别留意,JTAG接口的引脚5和引脚9需要上拉到2.5V,而不是3.3V.如下图所示:

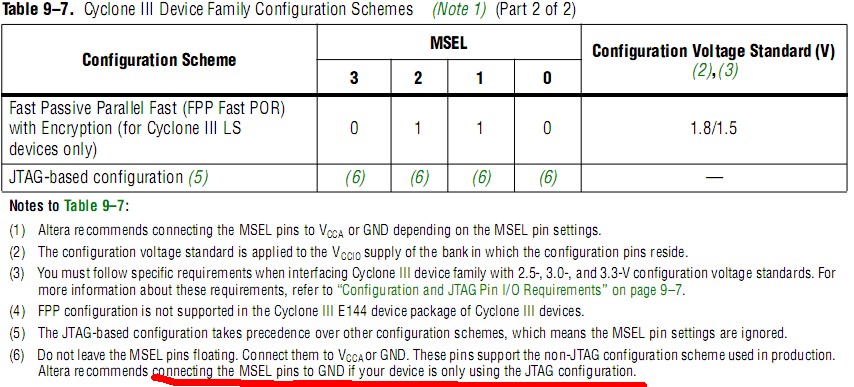

由于我这块采集板上,只留了一个JTAG口,所以只能通过JTAG口下载JIC文件的方法间接对EPCS进行编程,这种方法中,按ALTERA的官方手册中来说,应该是这样的(cyclone3_handbook.pdf的P172面)

似乎是采取最后的只用JTAG配置方式,但是其实手册的意思并不是你采取的配置的接口,而是你最终用什么方式来配置FPGA,如果你的设计中,将MSEL都接到地,那么你就只能用JTAG来配置FPGA,就不能用JTAG来间接烧写JIC到EPCS中进行配置了,因为这种方法,在FPGA内部做了一个转换电路,其本质还是AS模式的配置,因此,要想固化程序到EPCS中,必须将MSEL接成010的模式,高电平为2.5V,可以接到VCCA上,低电平为GND.

如果在这里,MSEL接成了000的模式,而又希望通过JTAG把JIC文件烧写到EPCS中,会出现:"Can't recognize silicon ID for device 1"的错误.

还有一点,在配置相关的接口中,21号引脚nCE一定要直接接到地,中间不要加下拉电阻,这一点错误很难发现,因为似乎涉及到一个电荷积累的问题,可能你加上了一个10k的下拉电阻,板子照样用着好好的,但是用着用着,你就会发现有那么几次开始JTAG开始出现问题:能检测到器件,但是没办法配置,配置的时候出现的问题是:'CONF_DONE pin failed to go high in device 1' ,然后会发现这种情况出现得越来越多,但是板子放置一段时间,或者断电后,将板子的电源和地短路泄放掉电流后,可能又可以正常配置了.

我的估计是,由于电荷的积累,在10K下拉电阻上出现了电荷的累积,导致逻辑电平发生变化,原本为低的nCE引脚变为高电平,导致配置错误.放电后可以暂时解决问题,但是由于这个引脚的这种特性,电荷积累过多,很有可能会出问题,所以一定要直接接到地.

其实只要把手册钻透,很多问题都是可以避免的,我这里写的几个我在设计中遇到的问题,希望能给大家一些参考,共同学习交流.

先记载这些,采集卡上还涉及到一些模拟电路和电源管理单元,其中的一些心得以后再写随笔记载.