使用matlab和ISE 创建并仿真ROM IP核

前言

本人想使用简单的中值滤波进行verilog相关算法的硬件实现,由于HDL设计软件不能直接处理图像,大部分过程都是可以将图像按照一定的顺序保存到TXT文档中,经过Modelsim仿真后,处理的数据再经过matlab显示图像;图像首先通过matlab或者C语言保存在TXT文档中,生成测试向量文件,然后在仿真软件中进行仿真处理,把处理后的数据保存为TXT格式,最后用matlab显示,观察结果。一般都是先创建MIF文件,将图像中的像素信息用一个ROM储存起来,然后调用ROM里面的地址进行处理,相当于制作了一个ROM查找表。

用Quartus II创建并仿真ROM的步骤:

1.在Quatus工程下生成一个ROM

2.编写.mif文件,作为ROM的初始化文件

3.将.mif文件拷贝到Modelsim工程下

4.进行Modelsim仿真

图像保存的步骤:

1.使用matlab将图像生成txt文。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | %将256位的BMP灰度图像128*128大小生成TXT文档,再生成mif文件;clcclear allclose allI_rgb = imread('lena.jpg');subplot(2, 2, 1), imshow(I_rgb), title('lena-rgb')I_gray = rgb2gray(I_rgb);subplot(2, 2, 2), imshow(I_gray), title('lena-gray')I = imresize(I_gray, 0.25);subplot(2, 2, 3), imshow(I), title('lena-qtr')fid = fopen('./lena.txt','wt');for i = 1 : size(I, 1) for j = 1 : size(I, 2) fprintf(fid, '%d ', I(i, j));%每个数据之间用空格分开% end fprintf(fid, '\n');endfid = fclose(fid);I_data = load('./lena.txt'); |

2.创建mif文件(Memory Initialization File):使用mif生成器、C语言或者matlab语言来生成;

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 | %mcode to create a mif filesrc = imread('lena.jpg');gray = rgb2gray(src);[m,n] = size( gray ); % m行 n列N = m*n; %%数据的长度,即存储器深度。word_len = 8; %%每个单元的占据的位数,需自己设定data = reshape(gray', 1, N);% 1行N列%fid=fopen('gray_image.mif', 'w'); %打开文件fid=fopen('gray_image.mif', 'w'); %打开文件fprintf(fid, 'DEPTH=%d;\n', N);fprintf(fid, 'WIDTH=%d;\n', word_len);fprintf(fid, 'ADDRESS_RADIX = UNS;\n'); %% 指定地址为十进制fprintf(fid, 'DATA_RADIX = HEX;\n'); %% 指定数据为十六进制fprintf(fid, 'CONTENT\t');fprintf(fid, 'BEGIN\n');for i = 0 : N-1 fprintf(fid, '\t%d\t:\t%x;\n',i, data(i+1));endfprintf(fid, 'END;\n'); %%输出结尾fclose(fid); %%关闭文件 |

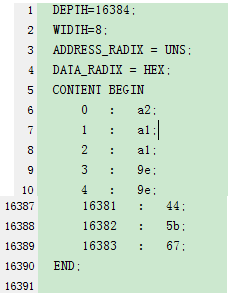

生成的mif文件如下图所示:

3.调用mif文件生成ROM(verilog文件即.v文件)

这个是Altera的方法,因为本人电脑上只安装了Xilinx软件,所以这一步没有进行实际操作。

使用Xilinx创建并仿真ROM的步骤:

1.编写.coe文件,作为ROM的初始化文件,.coe文件的格式和内容如代码所示:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 | %mcode to create a coe file%生成的数据是一行行进行读取的src = imread('lena.jpg');gray = rgb2gray(src);[m,n] = size( gray ); % m行 n列N = m*n; %%数据的长度,即存储器深度。word_len = 8; %%每个单元的占据的位数,需自己设定data = reshape(gray', 1, N);% 1行N列%fid=fopen('gray_image.mif', 'w'); %打开文件fid=fopen('lena.coe', 'wt'); %打开文件fprintf(fid, 'MEMORY_INITIALIZATION_RADIX=16;\n');fprintf(fid, 'MEMORY_INITIALIZATION_VECTOR=\n');for i = 1 : N-1 fprintf(fid, '%x,\n', data(i));%使用%x表示十六进制数endfprintf(fid, '%x;\n', data(N)); %%输出结尾,每个数据后面用逗号或者空格或者换行符隔开,最后一个数据后面加分号fclose(fid); %%关闭文件 |

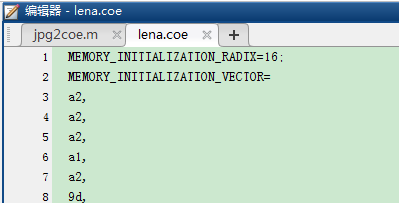

2.生成的.coe文件格式如下图所示:

3.使用Xilinx中的Core Generator完成ROM的例化(生成的.coe文件的图像数据是一行行进行读取的)。

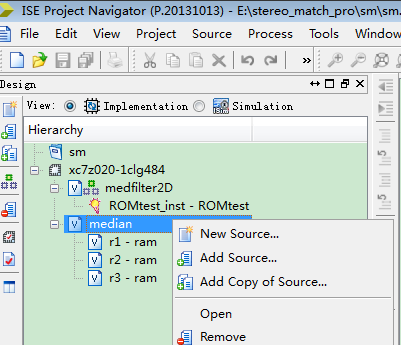

打开ISE,右键单击New Source,如下图所示:

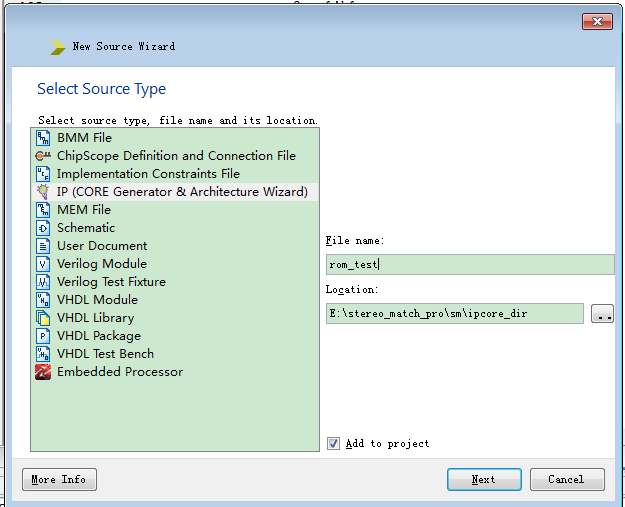

单击之后选择IP_Core_Generator,

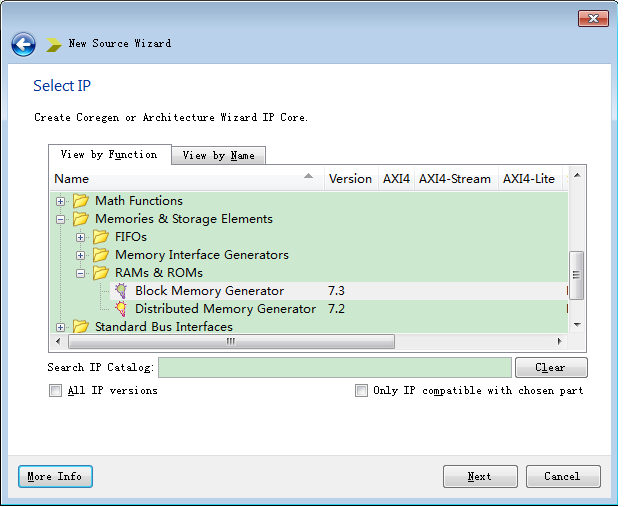

单击Next选项,选择Memories&Storage Elements->RAMs&ROMs->,选择块式存储或者分布式存储(这里根据存储数据的大小进行选择,较小的可以选择块式存储)。

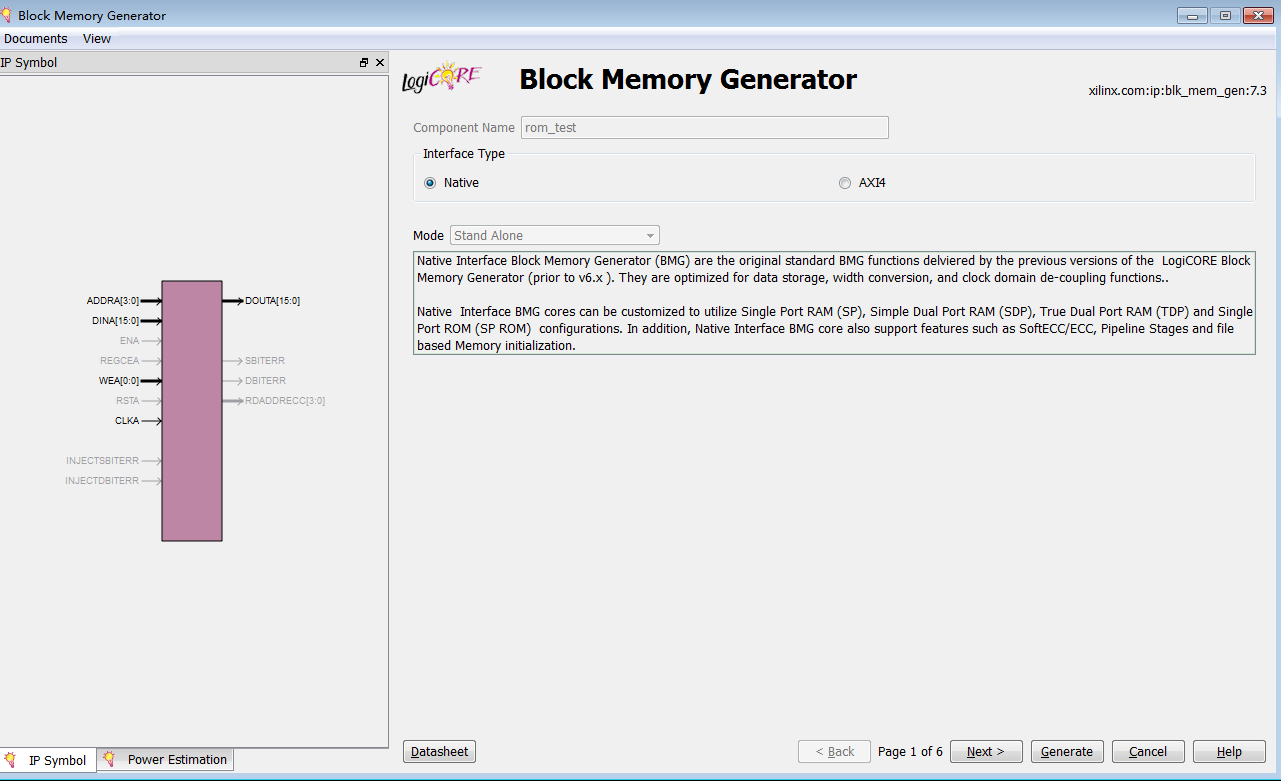

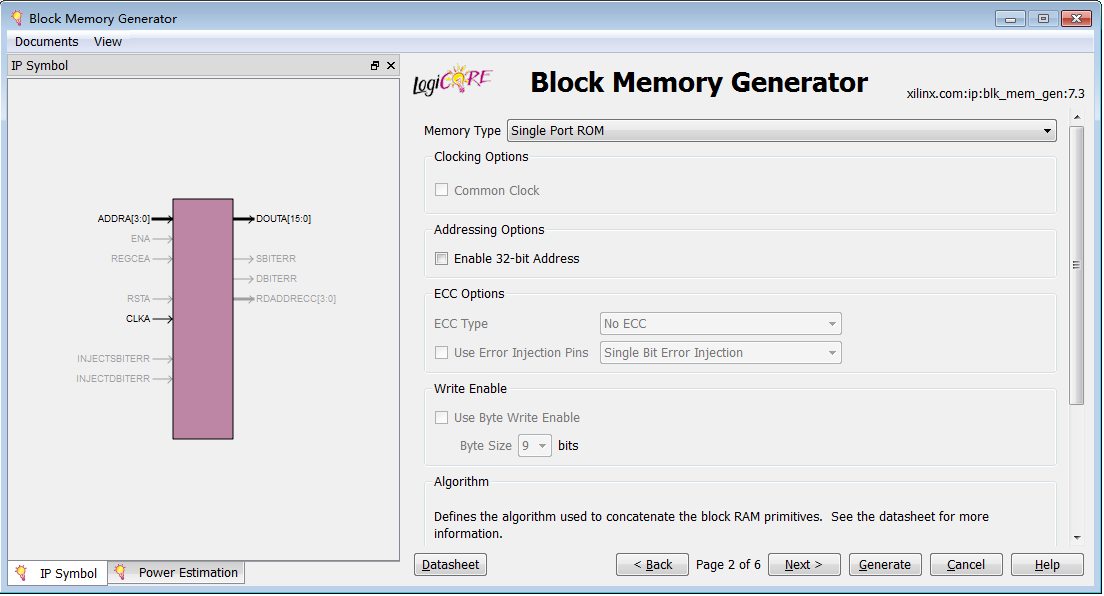

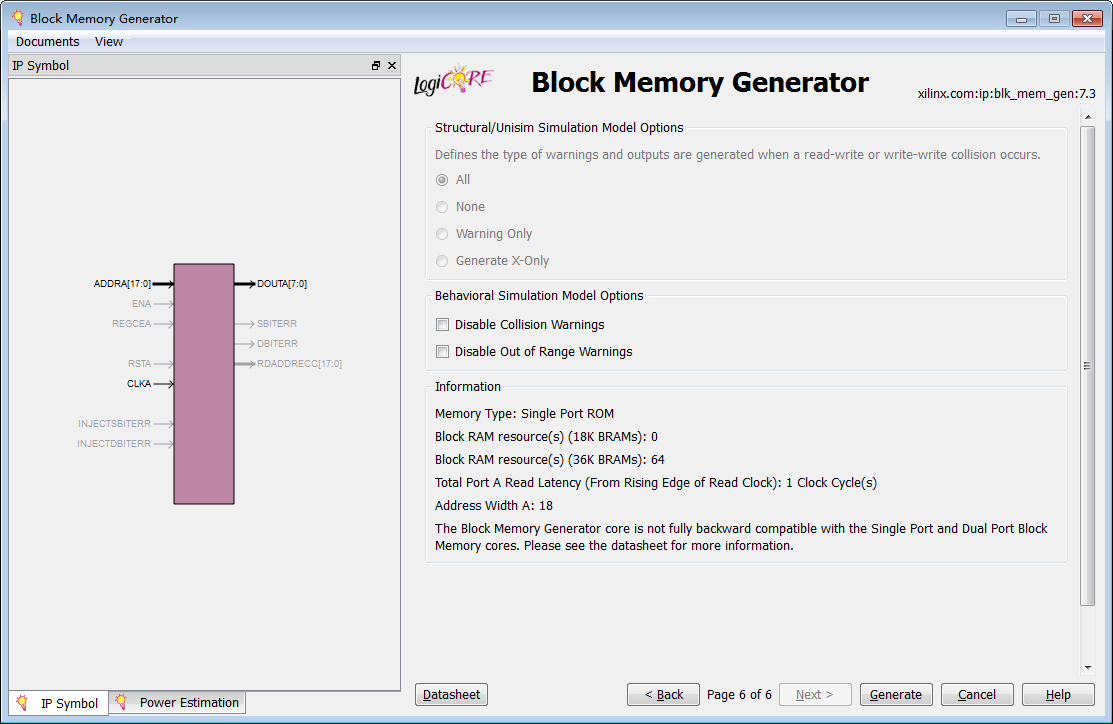

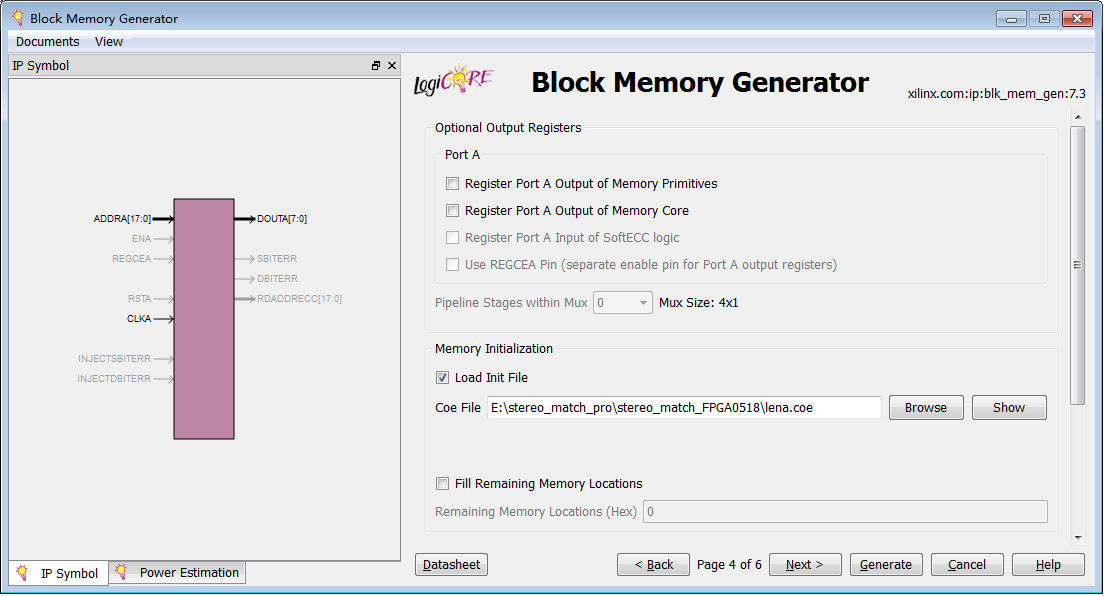

点击Next,然后Finish。然后就出现了下面的界面,一直点击Next进行ROM属性的一些设置,直至完成:

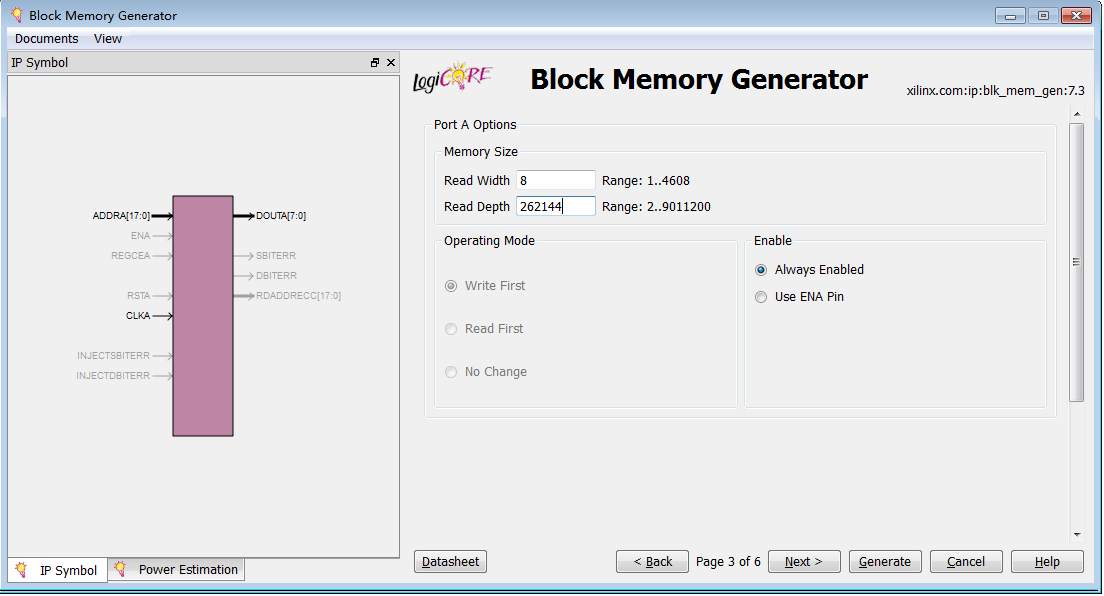

然后就要选择所需要的ROM的大小

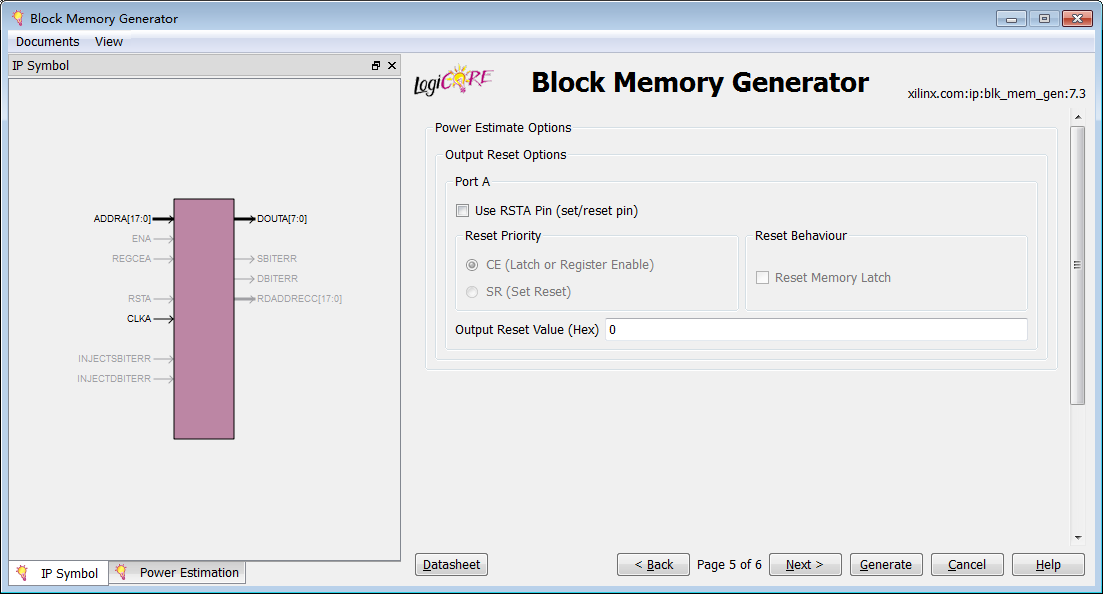

portA 表示输出要不要时钟打拍输出,这个是在mux里实现的;

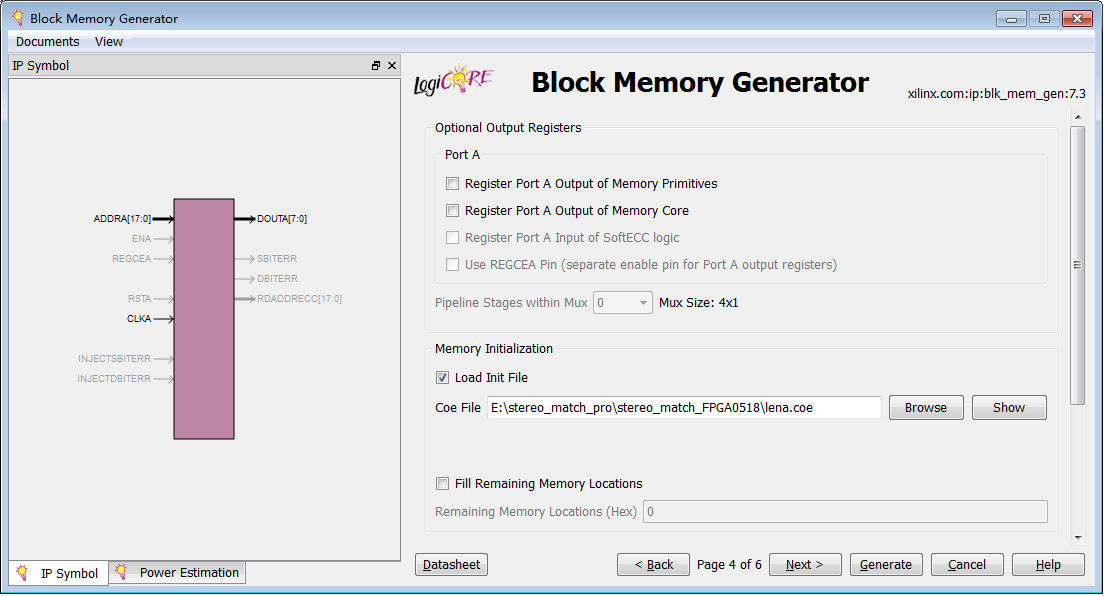

在添加初始化文件的时候,将之前matlab生成的.coe文件添加到ROM IP核中去。

一直next下去,就可以得到初始化好的ROM IP核,可以在./ipcore_dir目录下查看ROM文件,从而可以在顶层模块中对ROM进行例化。

生成的ROM文件的输入输出变量如下:

module rom_512by512( clka, addra, douta ); input clka; input [17 : 0] addra; output [7 : 0] douta;

在顶层模块中对ROM进行例化如下:

wire [7:0] rom_data; wire [17:0] rom_addr; rom_512by512 U1 ( .clka(CLK), //input clka; .addra( rom_addr), //input .douta(rom_data) //output );

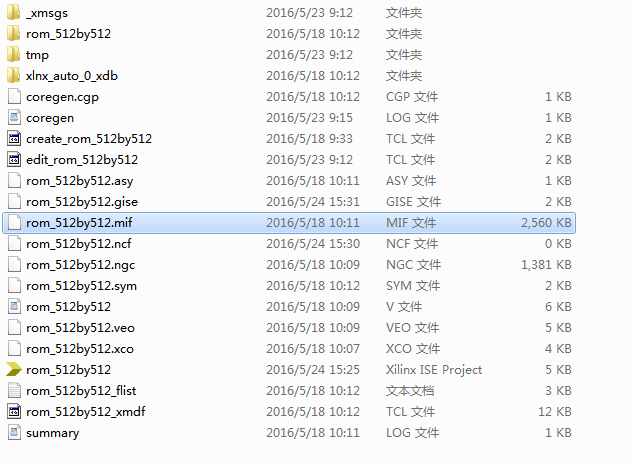

4.使用CoreGenerator完成ROM的例化后会生成一个.mif文件,这是Modelsim进行ROM仿真时需要的初始化文件,将.mif文件复制到Modelsim工程下进行仿真。

5.查看ROM模块中的初始化数据,双击Rom模块,出现如下图的界面,点击show按钮,即可查看数据;

完

心正意诚,做自己该做的事情,做自己喜欢做的事情,安静做一枚有思想的技术媛。

版权声明,转载请注明出处:https://www.cnblogs.com/happyamyhope/

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 如何编写易于单元测试的代码

· 10年+ .NET Coder 心语,封装的思维:从隐藏、稳定开始理解其本质意义

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 地球OL攻略 —— 某应届生求职总结

· 周边上新:园子的第一款马克杯温暖上架

· Open-Sora 2.0 重磅开源!

· 提示词工程——AI应用必不可少的技术

· .NET周刊【3月第1期 2025-03-02】