cacheline基本理论

2019-04-18 20:56 剑动情缥缈 阅读(2051) 评论(0) 编辑 收藏 举报一.cacheline

1.cache:解决cpu频率与内存访问之间速度差距越来越大的问题

2.cacheline:cpu cache的最小单位,主流为64B

3.指导:访问数组数据在同一个cacheline内速度很快,若跨cacheline,则速度会慢很多,因为可能存在cache miss,需要将内存数据写入cache中

二.cacheline与内存之间的映射策略

1.hash策略:hash值的计算需要10K个cycle,无法满足cache访问几个或者几十个cycle的要求

2.Fully Associative:时间问题

3.Direct Mapped:对每块内存的访问是等概率的,否则cache使用率很低,并且冲突很多

4.N-Way Set Associative:高效

a.将N个cacheline分为一组

b.每个cacheline中,根据偏移进行寻址,所以64B,需要6bit进行表示

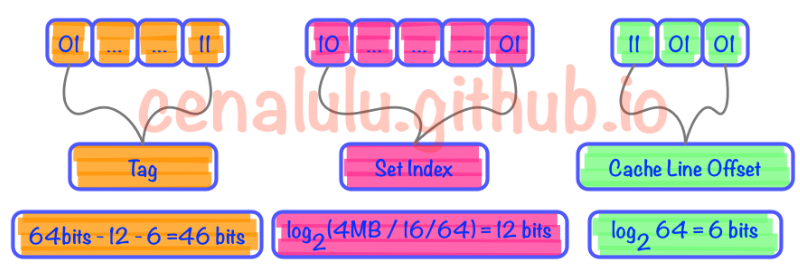

如下:4M cache,设N=16,则

①4M内存,16个64B的cacheline为一组,共有2^12组Set,用中间12bit表示

②最后6bit表示64B的cacheline内偏移

实际cache寻址过程如下:

①根据64bit表示的addr的12bit计算出set号,这样的话,只需要在本set内比较16个cacheline即可

②根据最后6bit表示的cacheline偏移,计算偏移地址

③对于set内的16个cacheline,结合前46bit,挨个比较每个cacheline中对应偏移的地址是否与addr相等

④若找到,则命中;否则cache miss

三.cacheline替换策略LRU/Random

1.LRU:最近最少使用算法,核心思想是最近被使用的内存在将来也有很大可能被使用

四、cacheline与内存对齐之间的性能问题

参考:

http://cenalulu.github.io/linux/all-about-cpu-cache/

https://en.wikipedia.org/wiki/Cache_placement_policies