摘要:

以前看datasheet,到了JTAG一章,一直奇怪为啥需要这么多篇幅来进行介绍。这段时间碰到两个JTAG问题,才把章节浏览了一遍。才理解了 TAP其实由TMS,TCK控制,有时候能扫描器件,但是不能下载是因为TMS,TCK是正常,但是其他信号不正常。才理解IR寄存器的 (instruction register)作用,以及长度的重要性。

问题的解决.感谢同事caijun的帮助

JTAG ISSUE

1) 出现JTAG CHAIN 的问题,问题描述

当进行XILINX CPLD 的JTAG下载的时候,LATTICE PM(power management)芯片(ISPPAC-POWER1220AT8)没有串在JTAG chain的链中(虽然同时接第一个TDI)。但是TDI,TMS,TCK仍然接在JTAG chain上,形成一个分叉。当采用XILINX IMPACT进行CPLD下载时,会失败。甚至get dvicecode也会失败。

问题原因:

是因为LATTICE PM的JTAG instruction 的定义和XILINX的instruction的定义不一致造成.

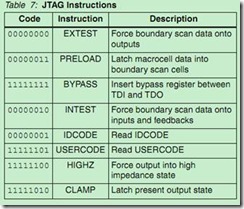

When program the CPLD by Xilinx software, it will read the every IC IDCODE, instruction signals come from TMS&TCK which are inputs for TAP.From Xilinx CPLD datasheet page12, read IDCODE instruction is 0000 0001.

and from Lattice power1220 (电源管理芯片ispPAC-POWR1220AT8)datasheet page47 JTAG instruction table, found that

they have a same IR(instruction register) length and TMS instruction 0000 0001 !!!!

因为lattice 的器件是一个电源管理芯片,所以会导致误操作lattice器件,电源异常,从而引起FPGA的问题.

另外,因为不是串在一个JTAG CHAIN上,所以无法被下载软件bypass掉

The TAP is controlled by the Test Clock (TCK) and Test Mode Select (TMS) inputs. These inputs determine whether an Instruction Register or Data Register operation is performed.

2) 问题描述:

在JTAG 链中,有lattice芯片和3片FPGA,使用chipscope的时候,出现FPGA异常,表现在initialize chain的时候,FPGA的内容似乎被删除,在trigger的时候,软件也被挂死。只有close cable(把JTAG cable关闭)才能重启

问题解决:2011-12-19

如下图,第一个器件是lattice的PM(电源管理芯片ispPAC-POWR1220AT8),其IR length(instruction register length)应该填入8。原来自己乱设为10,可能就造成了LATTICE芯片的错误,或者其他FPGA不可知的错误。 查看lattice atasheet改为8即可。修改可在menu ,JTAG CHAIN/JTAG CHAIN SETUP。其实不是电源问题,而是IR Length填写错误,写成10后,可能就把FPGA的IR指令一并带入受到影响,造成没有预料的问题。

JTAG设计小节

1)不要做分叉的JTAG CHAIN,把整个CHAIN串在一起,这样可以bypass不需要的芯片。如果是分叉结构,分叉的芯片由于扫描不到,没法做到bypass,这时虽然分叉,TDO没有接回来,但是TMS,TCK仍然接在一起,就会产生问题(当然主要是电源管理芯片)。

2)如果需要隔离一个芯片的JTAG,必须把TMS,TCK禁止掉,因为这两者才是TAP的输入信号(见JTAG的结构,TAP),由于不同公司的IR寄存器(instruction register)定义不一样,所以会出现冲突的问题(见上)。TDI也有影响。

3)对于POWER management的JTAG,要注意其输出是否影响到整个链的电源,如果影响了,可以增加跳线进行模式选择,让其直接返回。同样对于FPGA,因为涉及到内置逻辑分析仪使用,建议提供模式只有FPGA的JTAG CHAIN.

4)理解JTAG的IR寄存器(instruction register),这个很多JTAG下载软件中碰到非本公司的芯片时,会要求输入IR寄存器的长度(如chipsope,lattice下载),因为bypass命令是全1命令,所有JTAG 需要遵守的不多的命令之一。错误的IR寄存器长度,会带来意想不到的问题。由于不同公司的IR寄存器(instruction register)定义只要遵守一些基本的定义,大部分定义不一样,所以会出现冲突的问题(见第一个issue)

5)Lattice 的PM 的JTAG不支持boundary scan function 。

6)有些芯片的JTAG 管脚供电电压不是和I/O电压一样,有时采用核电压,如CYPRESS QDRII+ SRAM

以上对于JTAG工程师而言比较简单,但是对于一般不关注JTAG CHAIN硬件工程师,则会有用。

本文来自博客园,作者:{e_shannon},转载请注明原文链接:https://www.cnblogs.com/e-shannon/archive/2011/12/21/2295858.html

![clip_image002[6] clip_image002[6]](https://images.cnblogs.com/cnblogs_com/e-shannon/201112/201112211456328322.gif)