ARM Cortex-M内核中ROM table的使用

今天在博客园上注册一个账号,打算往后好好写技术博客,原来在新浪上写过几篇,不过距离上一次写是好几个月前的事情了。

突然开始做一件事情,总是有点各种各样的缘由。一条路总有分岔的地方,或者你打算自己在路上开辟一条岔道。选择走哪条岔路也好,自己开辟一条岔道也好,如果对自己负责,似乎都需要停下来,主动搜集一下各种信息,听听其他人的看法,然后再决定以何种方式前进。幸好有些人愿意和你分享自己的看法,幸好现在搜集信息不算困难,幸好无论哪种选择都会有人支持你。

ROM table是ARM 系列soc必须有的一个组件,用来识别调试组件,关于它的中文资料比较少,我主要看的就是这两篇:1.ARM CORTEX M系列中ROM TABLE原理分析。2.rom table。第一篇对我理解ROM table帮助很大。

读取ROM表,确定系统可用调试组件实现流程

读取SWD-AP寄存器中偏移地址是0XF8的寄存器,读到的值为ADD,如果ADD[0]为1,则说明ADD[31:12]表明了ROM表的基地址

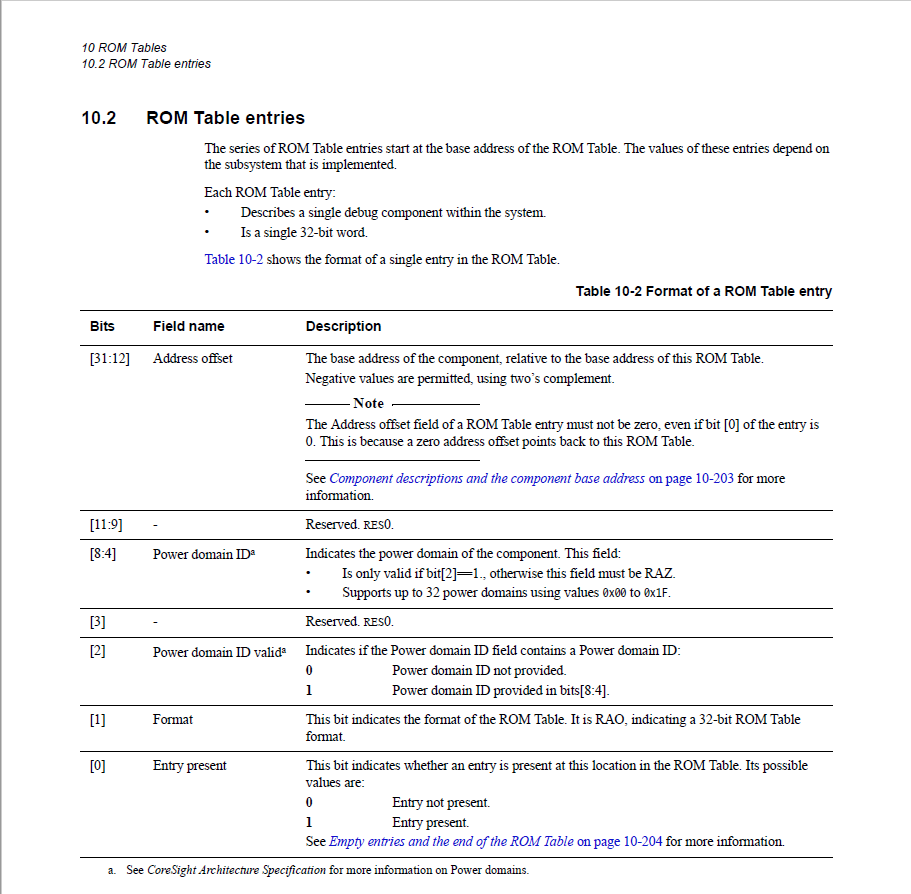

获得ROM表的基地址后可以按顺序读取ROM表(大小为4K)中的数据,每个ROM表最多有960个entry,entry的格式如图1。

图1

按顺序读取每个entry,读到的值为value1,value2 , ……,valuen 。Value[31:12]是组件的偏移地址,value[0]表明组件是否存在,value=0x00000000是ROM表结束,表示后面没有其他entry。

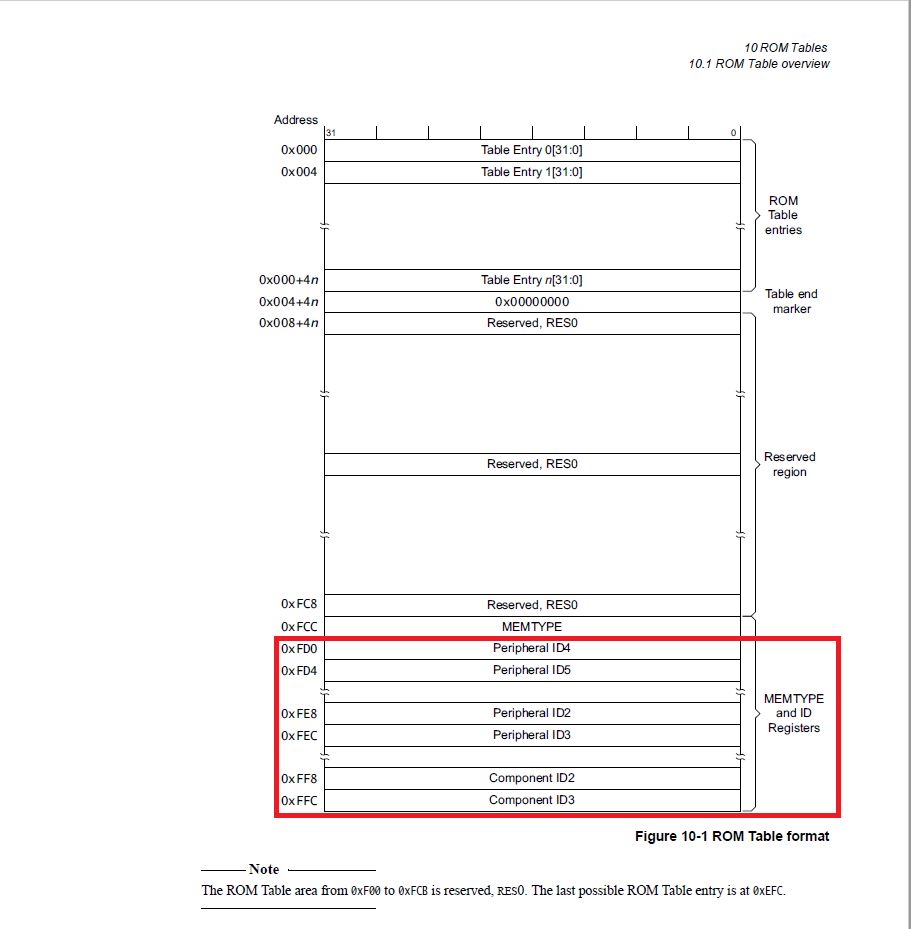

ROM表的entry读完后,还要读取ROM表最后的PID和CID,CID1[7:4]=0x1表明当前是ROM表,如果是调试组件,其值为0xe。PID和CID在ROM table中的偏移如下图2红框所示.然后根据从ROM表得到的信息(每个entry解析出来的信息),也就是每个入口指向的地址(每个4K块开头的地址,分别对应不同的调试组件),然后读4K块最后一片区域的PID,CID,根据PID,CID的值提取该调试组件的有关信息,确定该组件是否存在和可用。

图2

如果只是针对Cortex-M0核,读取ROM表并通过ROM表信息判断调试组件是否存在是相对比较简单的,点击这里,搜索“DWT M0”,点开搜索结果的第四个,里面的超链接有关于Cortex-M0内核ROM表内容的说明,包括每个组件的的识别即对应PID,CID的值是什么。Cortex-m0+在搜索结果的第六条

以上就是使用ROM表确定系统可用组件过程。

先写这样,后面会继续在这篇博客里补充细节,包括官方资料的下载链接。