第2章 ARM指令分类及其寻址方式

2.1 ARM指令集概要介绍

ARM指令集可以分为跳转指令、数据处理指令、程序状态寄存器(PSR)传输指令、Load/Store指令、协处理器指令和异常中断产生指令6类:

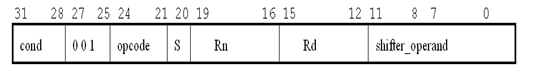

ARM指令字长为固定的32位。一条典型的ARM指令编码格式如下:

opcode 指令操作符编码。

cond 指令执行的条件编码。

S 决定指令的操作是否影响CPSR的值。

Rd 目标寄存器编码。

Rn 包含第1个操作数的寄存器编码。

shifter_operand 表示第2个操作数。

大多数ARM指令都可以条件执行,也就是根据CPSR中的条件标志位决定是否执行该指令。当条件满足时执行该指令,条件不满足时该指令被当作一条NOP指令,这时处理器进行判断中断请求等操作,然后转向下一条指令。

2.2 ARM指令寻址方式

数据处理指令的操作数的寻址方式。

字及无符号字节的Load/Store指令的寻址方式。

杂类Load/Store指令的寻址方式。

批量Load/Store指令的寻址方式。

协处理器Load/Store指令的寻址方式。

通常数据处理指令的格式如下所示:

<opcode>{<cond>}{S} <Rd>,<Rn>,<shifter_operand>

其中:

<opcode> 是指令助记符,如ADD表示算术加操作指令。

{<cond>} 表示指令执行的条件。

{S} 决定指令的操作是否影响CPSR的值。

<Rd> 表示目标寄存器。

<Rn> 表示包含第1个操作数的寄存器。

<shifter_operand> 表示第2个操作数。

2.2.1 数据处理指令的操作数的寻址方式

数据处理指令操作数的具体寻址方式有下面11种。

#<immediate>

<Rm>

<Rm>,LSL #<shift_imm>

<Rm>,LSL <Rs>

<Rm>,LSR #<shift_imm>

<Rm>,LSR <Rs>

<Rm>,ASR #<shift_imm>

<Rm>,ASR <Rs>

<Rm>,ROR #<shift_imm>

<Rm>,ROR <Rs>

<Rm>,RRX

2.2.2 字及无符号字节的Load/Store指令的 寻址方式

种类型的Load/Store指令的寻址方式由两部分组成。

一部分为一个的基址寄存器;另一部分为一个地址偏移量。

基址寄存器可以为任一个通用寄存器;

地址偏移量可以有以下3种格式。立即数 寄存器 寄存器及一个移位常数

同样,寻址方式的地址计算方法有如下3种:偏移量方法 事先更新方法 事后更新方法

LDR指令的语法格式如下所示:

LDR{<cond>}{B} {T}<Rd>,<address_mode> 其中,<address_mode>表示第2个操作数的内存地址,共有如下9种格式:

[<Rn>,#+/–<offset_12>]

[<Rn>,+/–<Rm>]

[<Rn>,+/–<Rm>,<shift>#<shift_imm>]

[<Rn>,#+/–<offset_12>]!

[<Rn>,+/–<Rm>]!

[<Rn>,+/–<Rm>,<shift>#<shift_imm>]!

[<Rn>],#+/–<offset_12>

[<Rn>],+/–<Rm>

[<Rn>],+/–<Rm>,<shift>#<shift_imm>

2.2.3 杂类Load/Store指令的寻址方式

杂类Load/Store指令包括:

操作数为半字(无符号数或带符号数)数据的Load/Store指令;

操作数为带符号的字节数据的Load 指令;双字的Load/Store指令。

这类指令的语法格式为: LDR|STR{<cond>}H|SH|SB|D <Rd>,<addressing_mode>

其中,<addressing_mode>是指令中内存单元的寻址方式,具体有以下6种格式:

[<Rn>,#+/–<offset_8>]

[<Rn>,+/–<Rm>]

[<Rn>,#+/–<offset_8>]!

[<Rn>,+/–<Rm>]!

[<Rn>],#+/–<offset_8>

[<Rn>],+/–<Rm>

2.2.4 批量Load/Store指令的寻址方式

一条批量Load/Store指令可以实现在一组寄存器和一块连续的内存单元之间传输数据。

其语法格式如下: DM|STM{<cond>}<addressing_mode> <Rn>{!}, <registers>{^} <addressing_mode>表示地址的变化方式,有以下4种方式。

IA (Increment After) 事后递增方式

IB (Increment Before) 事先递增方式

DA (Decrement After) 事后递减方式

DB (Decrement Before) 事先递减方式

2.2.5 协处理器Load/Store指令的寻址方式

一条协处理器Load/Store指令可以在ARM处理器和协处理器之间传输批量数据。

其语法格式如下: <opcode>{<cond>}{L} <coproc>,<CRd>,<addressing_mode>

其中,<addressing_mode>表示地址的变化方式,有以下4种格式:

[<Rn>,#+/–<offset_8>*4]

[<Rn>,#+/–<offset_8>*4]!

[<Rn>],#+/–<offset_8>*4

[<Rn>],<option>