SDRAM 学习(三)之command

command 模块总述

SDRAM 的 command 模块的内容包括如下:

1、对初始化请求、配置模式寄存器、读/写、刷新、预充电等命令的一个优先级的控制。

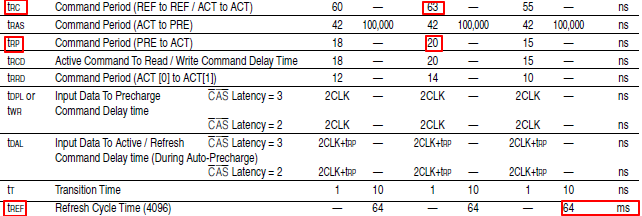

2、对命令执行时间进行控制,依据如图1,红圈框起来的都是最小值。

图1

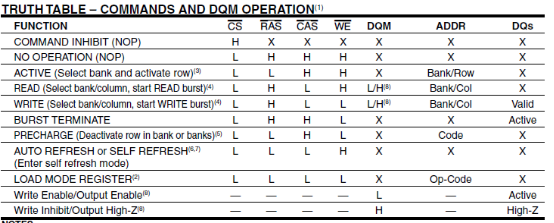

3、将相应的命令进行解码即转化成相应的控制总线,转化依据如图2:

图2

代码详解

以下代码都是我通过学习别人的代码,然后按照我自己的理解修改后的,经过验证是正确的。

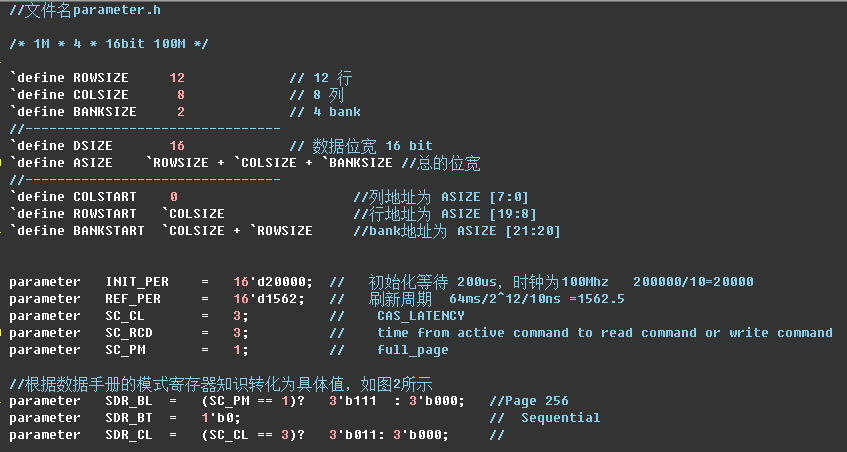

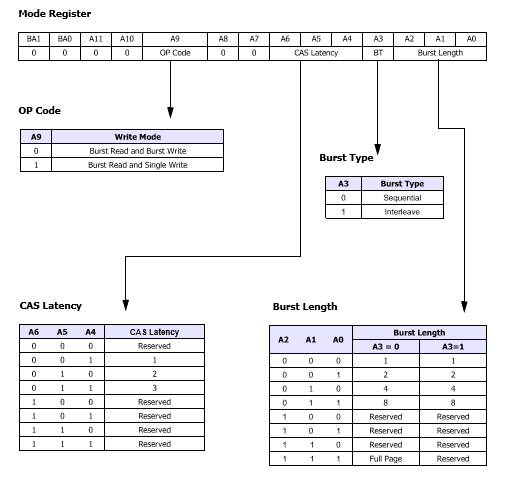

1、SDRAM 重要的参数

SDRAM 的容量为 4 * 1 M* 16 bit , 一共有 4 个 bank , 每个 bank 为 12 行、8列。 本次设计 SDRAM 为 顺序的突发读写模式、TCAS=3,TCL=3 。

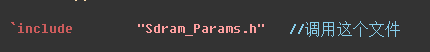

我们将这些参数定义到 parameter.h 模块中,然后通过 `include "parameter.h" 在其他文件中调用这个文件,具体如下。

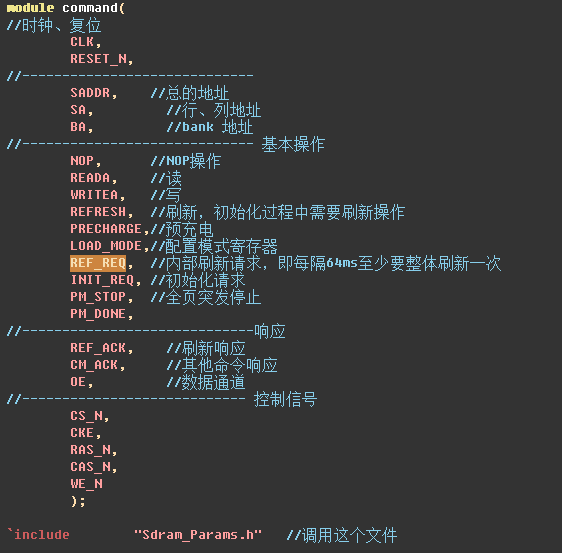

在command.v 中调用该文件。

图2

2、command.v 模块接口

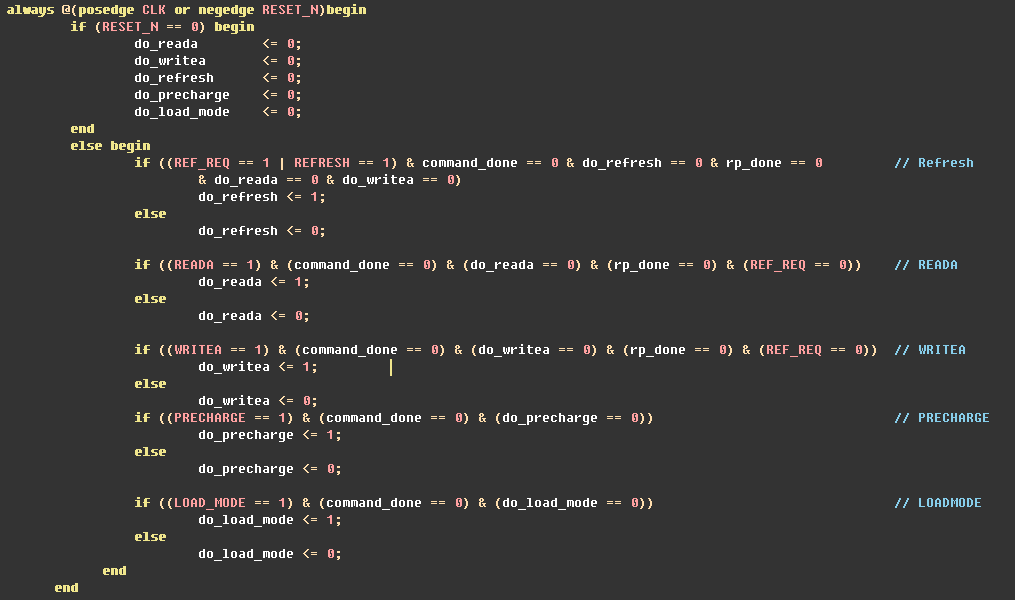

3、命令的优先级,

(1) SDRAM在每一刻只有一个指令在执行;

(2) 先到的指令先执行,即:如果刷新请求到来时,其它命令正在执行中,要等到当前命令执行完成后,才能执行刷新指令;

(3) 其它指令和刷新请求同时到来时刷新操作先执行。

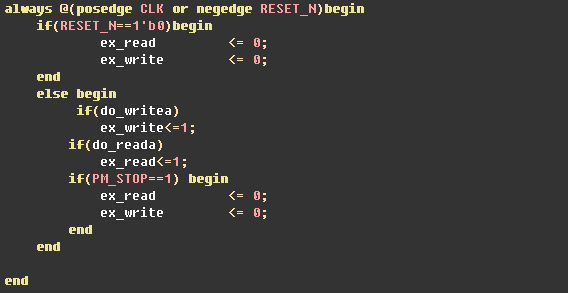

命令优先级代码:

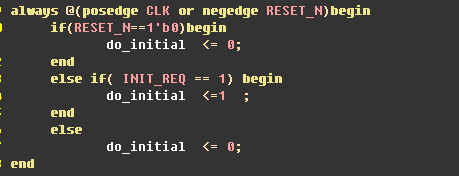

初始化命令,可以和上面的代码融合为1个代码。

初始化命令,可以和上面的代码融合为1个代码。

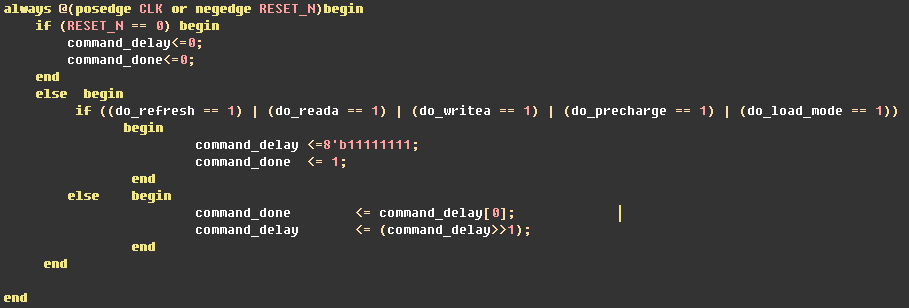

4、命令执行的延时控制

经过优先级判断后,要把指令解码成可控制SDRAM的信号,同时还要用三个移位寄存器对命令执行的延迟时间进行控制。第一个为指令延时寄存器,用来保证SDRAM有充足时间完成最终指令。例如,如果命令的执行需要9个时钟周期的时间(高手进阶—终极内存计数指南中说刷新需要9个时钟周期),则指令延时寄存器command_delay的初值设为 8 个 1 即“11111111”,同时声明一个内部信号command_done,作为指令执行完成的标志的。在指令执行期间,每一个时钟上升沿到来时,移位寄存器向右移位一次,command_delay[0]的移入command_done,同时“0” 移入最高位command_delay[7]。当command_done为“0”时,就说明指令的延迟时间已到,即通过command_done的值,就可以判断当前指令是否执行完成。要注意的是:移位寄存器的位数和初值,应该根据SDRAM的数据手册中命令完成需要的时间和系统的时钟周期来确定。

观察 图1 给出的数据手册内容得知,命令执行时间最长的是刷新命令至少63ns,我们时钟是100Mhz,至少需要7个时钟周期,因此设置为''11111111"是合适的,而对于更高工作频率的SDRAM则需要更多的时钟周期,只要满足数据手册要求就好了。

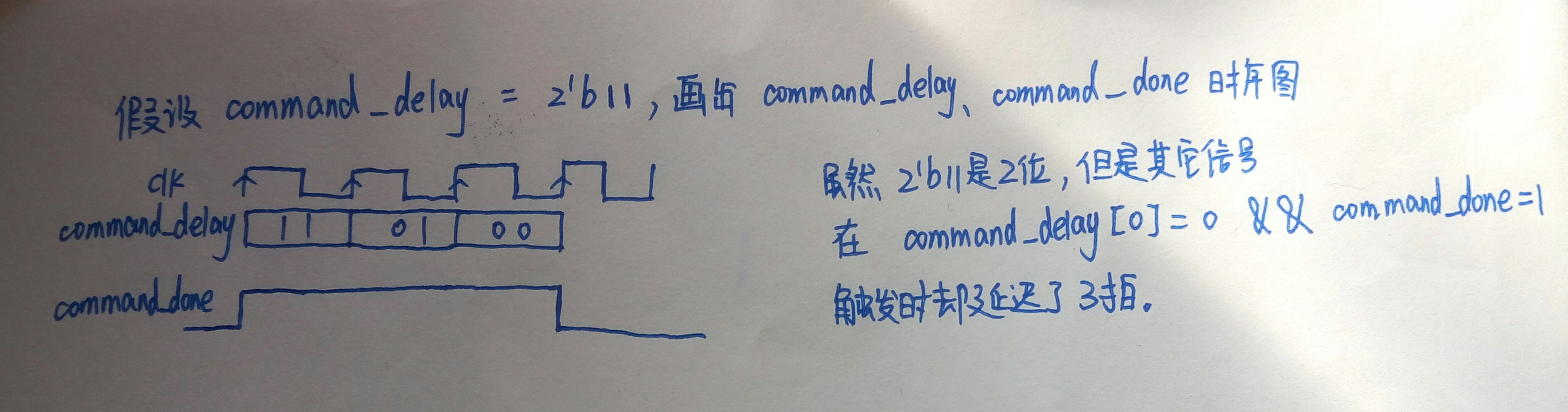

下面我将画出command_delay = 2‘b11 的时序图,以便理解。

代码:

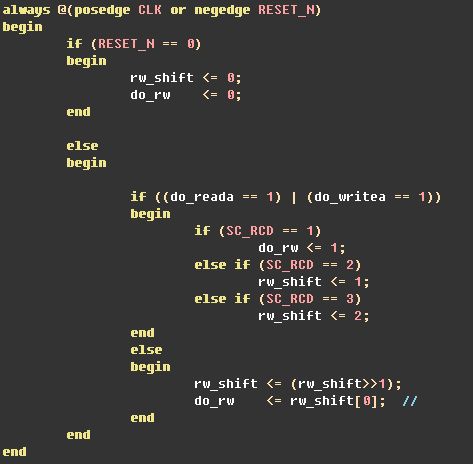

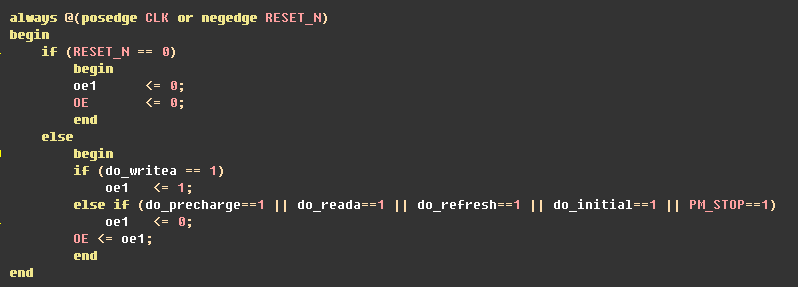

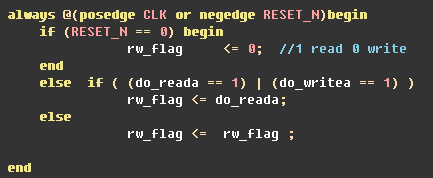

当输入的指令为writea和reada指令,行激活到列激活必须满足的时间 TRCD。所以,声明第二个移位寄存器rw_shift,来计算这两个指令的附加时间,其工作原理和第一个移位寄存器是一样的。数据通道oe,即数据输入、输出使能信号。对于非页模式的读写来说,oe保持有效的时间取决于突发长度。并且oe有效的起始时间对读操作和写操作时不同的:读操作时,oe有效的起始时间取决于CAS延时时间,而对于写操作时则在写指令开始时oe就是有效的。

刷新、读、写命令还需要一个延时,原因如下(这都是我自己的理解还请大神指点)

对于非全页模式,延迟完 9 个时钟周期后继续延时 5 个时钟周期保证命令有充足的时间执行完毕我是这样理解的,对于非全页模式的读来讲,需要的最大时间为

TRCD(3)+TCL(3)+8(突发长度为8) = 14个时钟周期。

对于全页模式则当一页数据传输完成后再延迟 5 个时钟周期,对于全页模式的读操作,Burst_STOP命令发出后,数据不是立刻停止,而是与CL有关,因此需要保护这些数据,进行一个延迟。

全页模式下ex_write、ex_read 有效时,即正在进行全页数据传输过程中,当PM_STOP指令来时,则为0,

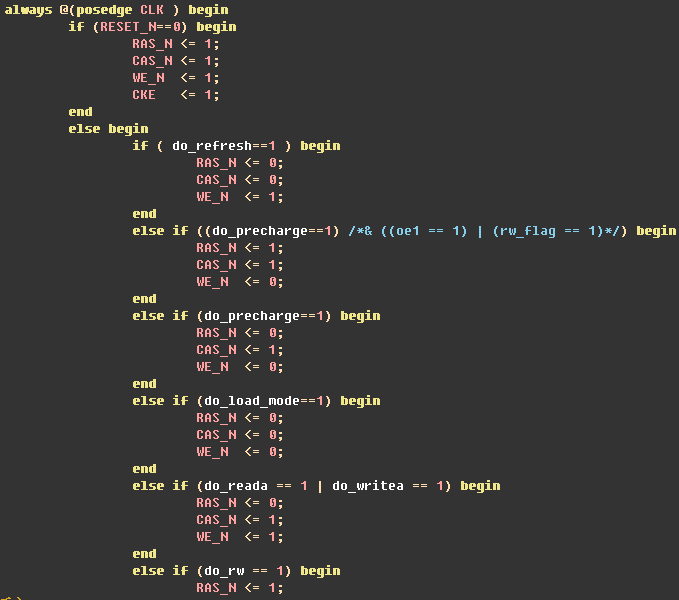

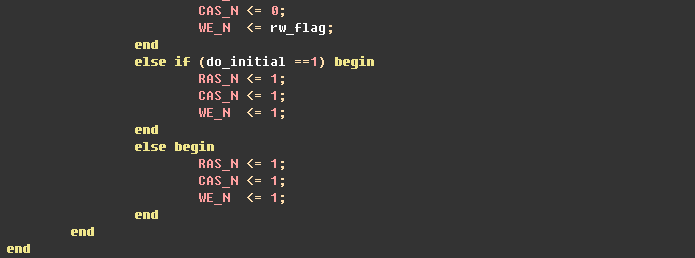

4、命令解码,将命令转化成控制信号的具体数值。

其中(do_reada| do_writea) 是指行激活

do_rw 是列激活

do_rw =1为读激活,do_rw =0 为写激活。

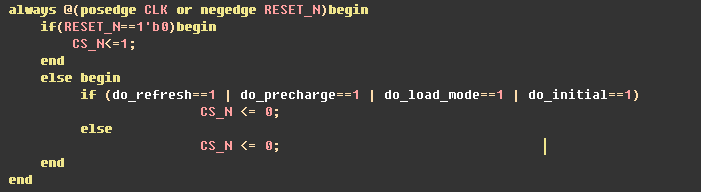

片选信号

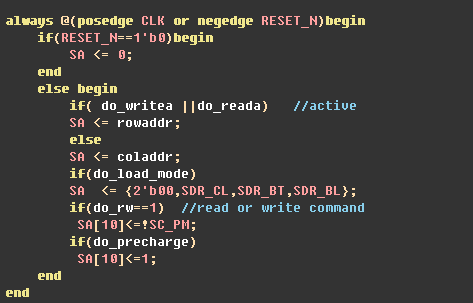

5、行列地址、bank地址

将总地址的值分开,与 SDRAM 的重要参数保持一致

行列参数,行和列地址共用数据总线

当是单独的预刷新命令,SA[10]=1是指所有bank预充电

当是do_rwdo_rw==1列激活,SA[10] =1代表执行完读写操作就自动刷新,SA[10]=0 的含义则反之,

这里需要注意的是全页模式不能设置自动刷新,即不能在全页模式读写完以后自动启动预刷新。

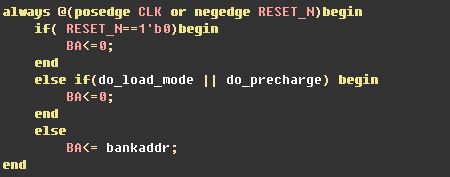

bank地址

这些都是比较重要的,简单分析做个总结怕自己忘记。SDRAM设计中有很多细节,数据手册还是要多看看,每看一遍感觉都是不一样的。

学习的过程中没人交流,只能靠自己从网上搜、各种尝试,虽然很艰难,还是挺开心的。

以上都是我自己的理解,如果有大神发现问题,还请指出,本女子感激不尽!

原文链接:http://www.cnblogs.com/aslmer/p/6031921.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号