【黑金原创教程】【FPGA那些事儿-驱动篇I 】实验二十九:LCD模块

实验二十九:LCD模块

据说Alinx 301支持 7”TFT,好奇的朋友一定疑惑道,它们3.2”TFT以及7”TFT等两者之间究竟有何区别呢?答案很简单,前者自带控制器也有图像内存。换之,后者好似缩小版台式的液晶,它除了接口以外什么也没有。

图29.1 7”TFT的引脚。

如图29.1所示,这只7“TFT拥有840 * 480的分辨率,应用VGA接口,所以左边才有熟悉的 HSYNC以及 VYSNC信号。LCD_CLOCK是像素时钟,最大为50Mhz,并且没有下限。LCD_RED/GREEN/BLUE 为 18位RGB,颜色支持范围是 218 = 262K。右边的DE为Data Enable拉高表示数据输入有效,LR/UD为扫描次序,例如自左向右,由高至下就是 2’b10,结果如表29.1所示:

表29.1 TFT的扫描次序。

| LR | UD | 扫描次序 |

| 0 | 0 | 自右向左,由上至下 |

| 0 | 1 | 自右向左,由下至上 |

| 1 | 0 | 自左向右,由上至下 |

| 1 | 1 | 自左向右,由下至上 |

根据手册,它支持两种模式,MODE拉低表示传统的VGA模式,MODE拉高则是DE模式。老实说,什么是DE模式,笔者真有点搞不懂,手册也没有详细注明,所以MODE信号必须拉低。这只7”TFT自带背光,我们可以经由PWM信号调节背光的亮度,具体内容请浏览手册,我们一般都是常年拉高。

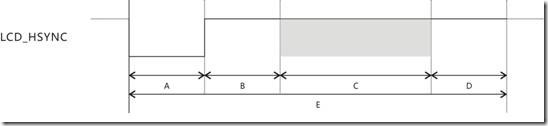

图26.4 VGA时序。

如图29.2所示,HSYNC以及VSYNC均为五段,具体长度如表29.2所示:

表29.2 显示标准800 × 480。

| 信号 | A | B | C | D | E |

| VGA_HSYNC | 48 | 40 | 800 | 40 | 928 |

| 信号 | O | P | Q | R | S |

| VGA_VSYNC | 3 | 29 | 480 | 13 | 525 |

笔者曾前面说过,折尺7”TFT应用VGA接口,驱动方法与实验二十六差不多。所以说,懒惰的笔者就直接沿用实验二十六的资源。

图29.3 128×96大小的小可爱。

图29.3是我们要显示的小可爱 ... 啊,不管怎么看,比卡丘最可爱了!完后,我们让我们建模去吧。

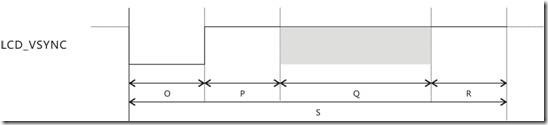

图29.4 LCD基础模块的建模图。

图29.4是LCD基础模块的建模图,内容包括储存模块以及的功能模块。相对PLL模块将时间分频为25Mhz,因为像素时钟是任意的。

lcd_funcmod.v

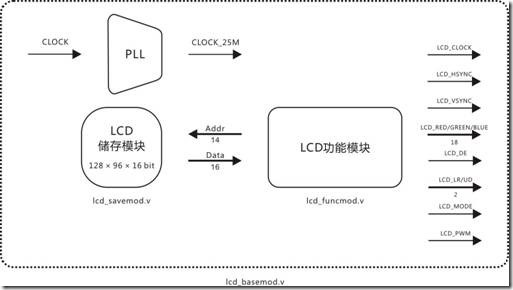

图29.5 LCD 功能模块。

图29.5是LCD功能模块的建模图,读者可能很好奇控制模块去哪儿了?非呀,控制模块已经被整合进去了。

1. module lcd_funcmod

2. (

3. input CLOCK, RESET,

4. output LCD_CLOCK,

5. output LCD_HSYNC, LCD_VSYNC,

6. output [5:0]LCD_RED,LCD_GREEN,LCD_BLUE,

7. output LCD_DE,

8. output LCD_UD, LCD_LR,

9. output LCD_MODE,

10. output LCD_PWM,

11. output [13:0]oAddr,

12. input [15:0]iData

13. );

14. parameter SA = 11'd48, SB = 11'd40, SC = 11'd800, SD = 11'd40, SE = 11'd928;

15. parameter SO = 11'd3, SP = 11'd29, SQ = 11'd480, SR = 11'd13, SS = 11'd525;

16.

以上内容为相关的出入端声明以及常量声明。

17. reg [10:0]CH;

18. always @ ( posedge CLOCK or negedge RESET )

19. if( !RESET )

20. CH <= 11'd0;

21. else if( CH == SE -1 )

22. CH <= 11'd0;

23. else

24. CH <= CH + 1'b1;

25.

26. reg [9:0]CV;

27. always @ ( posedge CLOCK or negedge RESET )

28. if( !RESET )

29. CV <= 10'd0;

30. else if( CV == SS -1 )

31. CV <= 10'd0;

32. else if( CH == SE -1 )

33. CV <= CV + 1'b1;

34.

以上内容为列计数与行计数的周边操作。

35. reg H;

36. always @ ( posedge CLOCK or negedge RESET )

37. if( !RESET )

38. H <= 1'b1;

39. else if( CH == SE -1 )

40. H <= 1'B0;

41. else if( CH == SA -1 )

42. H <= 1'b1;

43.

44. reg V;

45. always @ ( posedge CLOCK or negedge RESET )

46. if( !RESET )

47. V <= 1'b1;

48. else if( CV == SS -1 )

49. V <= 1'b0;

50. else if( CV == SO -1 )

51. V <= 1'b1;

52.

以上内容为列控制以及行控制的周边操作。

53. parameter XSIZE = 8'd128, YSIZE = 8'd96, XOFF = 10'd0, YOFF = 10'd0;

54.

55. wire isX = ( (CH >= SA + SB + XOFF -1 ) && ( CH <= SA + SB + XOFF + XSIZE -1) );

56. wire isY = ( (CV >= SO + SP + YOFF -1 ) && ( CV <= SO + SP + YOFF + YSIZE -1) );

57. wire isReady = isX & isY;

58.

59. wire [31:0] x = CH - XOFF - SA - SB -1;

60. wire [31:0] y = CV - YOFF - SO - SP -1;

61.

以上内容为图像信息的常量声明,有效行列,以及地址转换等即时声明。

62. reg [31:0]D1;

63. reg [15:0]D2;

64.

65. always @ ( posedge CLOCK or negedge RESET )

66. if( !RESET )

67. begin

68. D1 <= 18'd0;

69. D2 <= 16'd0;

70. end

以上内容为相关的寄存器声明以及复位操作。D1暂存图像的地址信息,D2暂存图像信息。

71. else

72. begin

73.

74. // step 1 : compute data address and index-n

75. if( isReady )

76. D1 <= (y << 7) + x;

77. else

78. D1 <= 14'd0;

79.

80. // step 2 : reading data from rom

81. // but do-nothing

82.

83. // step 3 : assign RGB_Sig

84. D2 <= isReady ? iData : 16'd0;

85.

86. end

87.

以上内容为核心操作。它是流水操作,步骤1转换图像信息地址至D1,步骤2等待图像信息反馈,步骤3暂存图像信息至D2。

88. reg [1:0]B1,B2,B3;

89.

90. always @ ( posedge CLOCK or negedge RESET )

91. if( !RESET )

92. { B3, B2, B1 } <= 6'b11_11_11;

93. else

94. begin

95. B1 <= { H,V };

96. B2 <= B1;

97. B3 <= B2;

98. end

99.

以上内容为对此行列延迟的周边操作。

100. assign LCD_CLOCK = CLOCK;

101. assign { LCD_HSYNC, LCD_VSYNC } = B3;

102. assign LCD_RED = { D2[15:11],1'b0};

103. assign LCD_GREEN = D2[10:5];

104. assign LCD_BLUE = { D2[4:0],1'b0};

105. assign LCD_DE = 1'b1;

106. assign {LCD_LR, LCD_UD} = 2'b10;

107. assign LCD_MODE = 1'b0;

108. assign LCD_PWM = 1'b1;

109. assign oAddr = D1[13:0];

110.

111. endmodule

以上内容为相关的输出驱动声。注意LCD_RED/BLUE 都是舍弃最低位,LCD_LR/UD为2’b10,LCD_MODE拉低,LCD_DE常年拉高。

lcd_savemod.v

内容基本上与实验二十六一样。

lcd_basemod.v

连线部署请参考图29.5。

1. module lcd_basemod

2. (

3. input CLOCK, RESET,

4.

5. output LCD_CLOCK,

6. output LCD_HSYNC, LCD_VSYNC,

7. output [5:0]LCD_RED,LCD_GREEN,LCD_BLUE,

8. output LCD_DE,

9. output LCD_UD, LCD_LR,

10. output LCD_MODE,

11. output LCD_PWM

12. );

以上内容为相关出入端声明。

13. wire CLOCK_25M;

14.

15. pll_module U1

16. (

17. .inclk0 ( CLOCK ),

18. .c0 ( CLOCK_25M )

19. );

20.

以上内容为PLL的实例化。注意,7”TFT除了最大像素时钟是50Mhz以外,余下可以任意设置。

21. wire [13:0]AddrU2;

22.

23. lcd_funcmod U2

24. (

25. .CLOCK( CLOCK_25M ),

26. .RESET( RESET ),

27. .LCD_CLOCK( LCD_CLOCK ),

28. .LCD_HSYNC( LCD_HSYNC ),

29. .LCD_VSYNC( LCD_VSYNC ),

30. .LCD_RED( LCD_RED ),

31. .LCD_GREEN( LCD_GREEN ),

32. .LCD_BLUE( LCD_BLUE ),

33. .LCD_DE( LCD_DE ),

34. .LCD_LR( LCD_LR ),

35. .LCD_UD( LCD_UD ),

36. .LCD_MODE( LCD_MODE ),

37. .LCD_PWM( LCD_PWM ),

38. .oAddr( AddrU2 ),

39. .iData( DataU3 )

40. );

41.

以上内容为功能模块的实例化。

42. wire [15:0]DataU3;

43.

44. lcd_savemod U3

45. (

46. .CLOCK( CLOCK_25M ),

47. .RESET( RESET ),

48. .iAddr( AddrU2 ),

49. .oData ( DataU3 )

50. );

51.

52. endmodule

以上内容为储存模块的实例化。

图29.6 显示效果。

完后,综合程序并且下载进去,如果7”TFT的左上角出现一群小可爱,结果如图29.6,那么表示实验成功。

细节一:完整的个体模块

本实验的LCD基础模块只是演示7”TFT如何驱动而已。

posted on 2015-06-24 10:49 ALINX官方博客 阅读(3903) 评论(0) 编辑 收藏 举报