stm32之RCC寄存器学习

RCC(Reset Clock Controller) —— 复位与时钟控制

一、复位

STM32F10xxx支持三种复位形式,分别为系统复位、上电复位和备份区域复位。

系统复位:除了时钟控制器的RCC_CSR寄存器中的复位标志位和备份区域中的寄存器以外,系统

复位将复位所有寄存器至它们的复位状态。

电源复位:将复位除了备份区域外的所有寄存器。

备份区域复位:备份区域拥有两个专门的复位,它们只影响备份区域。

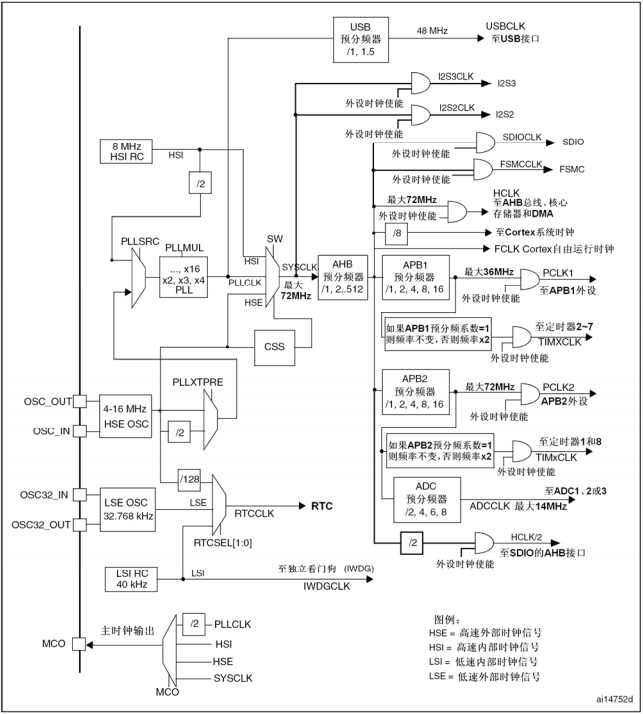

二、时钟

有四种时钟:高速外部时钟信号(HSE)—— HSE外部晶体/陶瓷谐振器 、HSE用户外部时钟

高速内部时钟信号(HSI)—— 由内部8MHz的RC振荡器产生

低速外部时钟信号(LSE)—— 32.768kHz的低速外部晶体或陶瓷谐振器

低速内部时钟信号(LSI)—— LSI时钟频率大约40kHz(在30kHz和60kHz之间)

时钟的输出:微控制器允许输出时钟信号到外部MCO引脚。 可以时钟配置寄存器来选择输出的时钟。

其中:

PLLMUL 用于设置 STM32 的 PLLCLK, STM32 支持 2~16 倍频设置。我们常用

的是 8M 外部晶振+9 倍频设置,刚好得到 72Mhz 的 PLLCLK。

SW 是 STM32 的 SYSCLK(系统时钟)切换开关,从上图可以看出, SYSCLK 的

来源可以是 3个:HSI、PLLCLK和 HSE。

CSS是时钟安全系统,可以通过软件被激活。一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被

使能,并在HSE时钟关闭后关闭 。

三、时钟启动过程

1、开机或复位时使用内部时钟

2、用软件进行切换,尝试开启外部时钟

3、如果开启成功,则使用外部时钟,否则使用内部

四、配置时钟的步骤

1、APB1、APB2的外设接口复位结束(即RESET),关闭APB1、APB2的外设时钟

打开内部8MHz振荡器,复位RCC->CFGR中的SW[1:0]、HPRE[3:0]、PRE1[2:0]、PRE2[2:0]、ADCPRE[2:0]、MCO[2:0]

复位RCC->CR中的HSEON、CSSON、PLLON、HSEBYP

复位RCC->CFGR中的PLLSRC、PLLXTPRE、PLLMUL[3:0]、USBPRE

关闭RCC->CIR中的所有中断

2、使能外部高速时钟晶振HSE

3、等待外部高速时钟晶振工作稳定

4、设置AHB时钟的预分频(在这之前要先执行FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable); FLASH_SetLatency(FLASH))

5、设置APB1时钟的预分频

6、设置APB2时钟的预分频

7、设置PLL的时钟源以及PLL的倍频数,然后使能PLL

8、等待PLL工作稳定

9、选择SYSCLK的时钟源

10、判断PLL是否是系统时钟(若选择SYSCLK的时钟源是PLL的话)

11、打开要使用的外设时钟

五、代码

void RCC_Init(void) { RCC->APB1RSTR = 0x00000000; //APB1、APB2复位结束 RCC->APB2RSTR = 0x00000000; RCC->AHBENR = 0x00000014; //睡眠模式时闪存和 SRAM 时钟使能,其他关闭(其实可以注释掉,因为AHBENR复位的值就是该值) RCC->APB1ENR = 0x00000000; //关闭APB1、APB2的外设时钟 RCC->APB2ENR = 0x00000000; RCC->CR |= 0x00000001; //使能内部时钟HSI RCC->CFGR &= 0xF8FF0000; //复位RCC->CFGR中的SW[1:0],HPRE[3:0],PRE1[2:0],PRE2[2:0],ADCPRE[2:0],MCO[2:0] RCC->CR &= 0xFEF2FFFF; //复位HSEON、CSSON、PLLON、HSEBYP RCC->CFGR &= 0xFF80FFFF; //复位RCC->CFGR中的PLLSRC,PLLXTPRE,PLLMUL[3:0],USBPRE RCC->CIR &= 0x00000000; //关闭所有中断[12:0] RCC->CR |= (1<<16); //使能HSE while(!(RCC->CR & (1<<17))); //等待HSE稳定 FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable); // 预取指缓存使能 FLASH_SetLatency(FLASH_Latency_2); //FLASH_Latency_2 2延时周期 RCC->CFGR |= 0x00000400; //AHB不分频,APB1二分频,APB2不分频 RCC->CFGR |= 0x001D0000; //配置PLL:HSE为输入时钟,HSE不分频,9倍频输出 RCC->CR |= (1<<24); //使能PLL while(!(RCC->CR & (1<<25))); //等待PLL锁定 RCC->CFGR |= 0x00000002; //选择PLL输出作为SYSCLK while(!(RCC->CFGR & (2<<2))); //等待 PLL 作为系统时钟设置成功 //下面就是打开所要用的外设时钟(RCC_AHBENR、RCC_APB1ENR、RCC_APB2ENR) }

仿真结果为:

浙公网安备 33010602011771号

浙公网安备 33010602011771号