EFM32G232F64时钟树

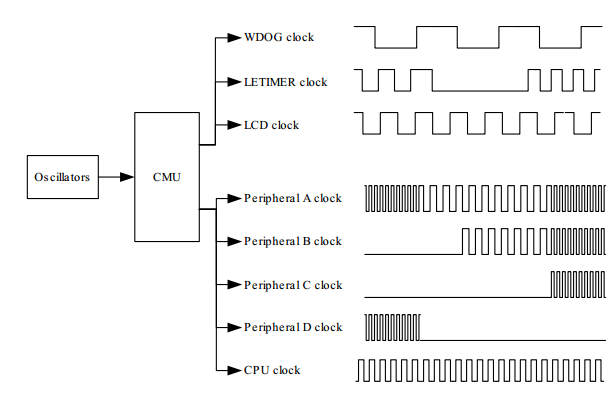

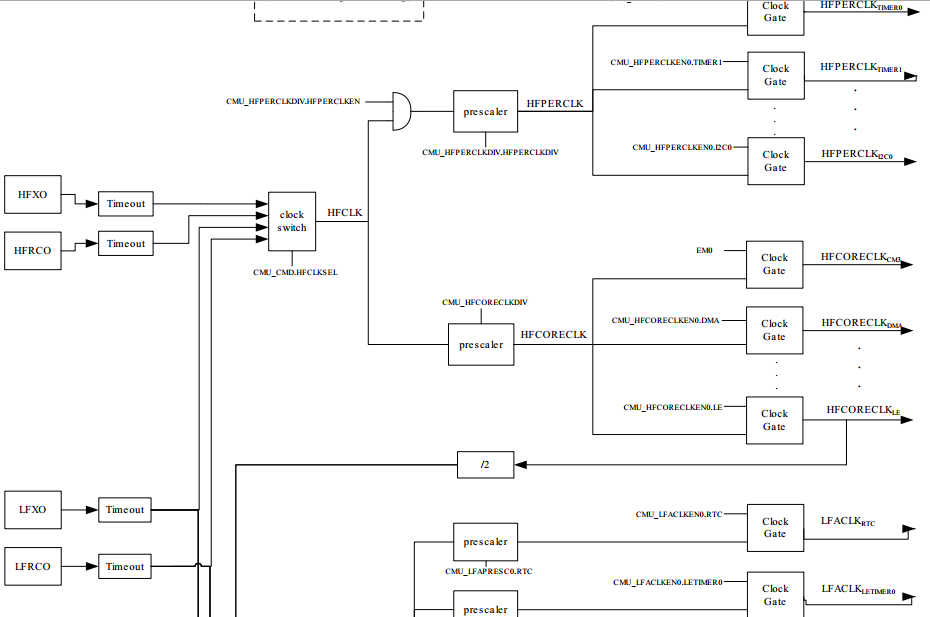

1.为了熟悉MCU的时钟树,先看看EFM32G232F64的CMU(ClockManagementUnit)

时钟管理单元(CMU)用于管控晶振(时钟源)和各个时钟节点。出于降低功耗和启动时间的目的,EFM32G的时钟源支持数个不同规格的晶振。另外还有一个独立的RC振荡器用于烧写Flash和调试。当然,时钟管理单元也从硬件级别上支持RC振荡器的校准。

晶振和系统时钟树,对于降低MCU的系统功耗有巨大意义。有了低功耗的晶振再结合弹性的时钟控制策略,就可以在各种应用场合下降低功耗。不使用的外设就关掉它的时钟源以节能。

时钟管理单元,能够配置选择不同的时钟源,使能和失能单个时钟分支和所有外设的时钟源,还能为不同的时钟分支设置预分频系数。短的晶振启动时间使得从非低功耗模式(active)到低功耗模式(EM2~EM4)的占空比变得非常高效。RC震荡校准特性保证了其高精度的RC震荡频率。

CMU_ClockSelectSet(cmuClock_LFB, cmuSelect_LFXO); //使能时钟分支

CMU_ClockEnable(cmuClock_LEUART0, true); //使能某个外设的时钟

1.1逻辑图

1.2 实际图

2.

从公司的硬件工程师那里得知,项目的PCB原理图上只外接了32.768KHz的低速晶振到15和16脚,那个13.56MHz的晶振不是给EFM32G232F64用的,而是给射频芯片THM3070射频芯片用的。所以,可以推测,EFM32G还是用了内部自带的高速时钟源。

2.1 从代码里找时钟树的配置细节

找时钟树配置是从公司的某个项目代码中找的。参考了以下博文,没有明显发现,但是博文还是值得一看。

2.2 CMU外设库函数 - CMU_ClockSelectSet

void CMU_ClockSelectSet(CMU_Clock_TypeDef clock, CMU_Select_TypeDef ref)中,clock是时钟分支,ref是外界的时钟输入源。

《EMF32G-RM》page97上说,默认HFCLK分支的时钟来源选择HFRCO,但是在多数应用时,推荐使用高频晶振,可以修改 HFCLKSEL in CMU_CMD(寄存器)去配置HFCLK的时钟源。

也就是说,在为各个时钟分支选好时钟源之后,剩下的就是配置各个时钟分支的分频系数了。这里没有发现PLL。选择时钟源使用函数CMU_ClockSelectSet。

补充:

周立功的资料上说,默认所有的外设时钟都是关闭的。

2. 常见问题解答

2.1 EFM32 系列MCU

1. 当我向某个控制寄存器写入数据然后读此寄存器,发现全部是 0,不知是什么原

因?

A:默认情况下, EFM32 系列 MCU 内部外设的时钟都是关闭的。如果要设置某个外设

的 寄 存 器 , 必 须 先 通 过 CMU_HFPERCLKEN0 、 HFCORECLKEN0 、 LFACLKEN 或

LFBCLKEN 来使能相关外设的时钟。若使用低频外设,还需在 CMU_HFCORECLKEN0 寄

存器中使能 LE 时钟。

附录

[转发]在main()之前,IAR都做了啥?

【原文链接】http://www.cnblogs.com/mssql/archive/2011/01/29/tt146.html

最近要在Cortex-M3上写一个简单的操作系统,打算使用IAR,为了写好启动代码,花了一些时间了解了IAR在main()以前做了些什么事。

首先系统复位时,Cortex-M3从代码区偏移0x0000'0000处获取栈顶地址,用来初始化MSP寄存器的值。

接下来从代码区偏移0x0000'0004获取第一个指令的跳转地址。这些地址,是CM3要求放置中断向量表的地方。

这里是一个程序的启动区的反汇编:

__vector_table:

08004000 2600

08004002 2000

08004004 7E1D

08004006 0800

这个程序是由IAP程序来启动的,IAP程序获取0x0800'4000处的MSP值(0x20002600),并设置为MSP的值,即主堆栈最大范围是0x2000'0000~0x2000'25FF。接下来IAP程序获取0x0800'4004处的Reset_Handler的地址(0x0800'7E1D),并跳转到Reset_Handler()执行。

IAP在这里完全是模仿了Cortex-M3的复位序列,也就是说,在没有IAP的系统上,CM3只能从0x0800'0000获取MSP,从0x0800'0004获取第一条指令所处地址。而IAP就存在在0x0800'0000这个地址上,IAP的启动,已经消耗掉了这个复位序列,所以IAP要启动UserApp程序的时候,也是完全模仿Cortex-M3的复位序列的。

接下来我们看看复位后第一句指令——Reset_Handler()函数里有什么。

若我们使用的是ST公司标准外设库,那么已经有了现成的Reset_Handler,不过他是弱定义——PUBWEAK,可以被我们重写的同名函数覆盖。一般来说,我们使用的都是ST提供的Reset_Handler,在V3.4版本的库中,可以在startup_stm32f10x_xx.s中找到这个函数:

PUBWEAK Reset_Handler

SECTION .text:CODE:REORDER(2)

Reset_Handler

LDR R0, =SystemInit

BLX R0

LDR R0, =__iar_program_start

BX R0

看来ST没有做太多的事,他只调用了自家库提供的SystemInit函数进行系统时钟、Flash读取的初始化,并把大权交给了__iar_program_start这个IAR提供的“内部函数”了,我们就跟紧这个__iar_program_start跳转,看看IAR做了什么,上面一段代码的反汇编如下:

Reset_Handler:

__iar_section$$root:

08007E1C 4801 LDR R0, [PC, #0x4]; LDR R0, =SystemInit

08007E1E 4780 BLX R0;BLX R0

08007E20 4801 LDR R0, [PC, #0x4];LDR R0, =__iar_program_start

08007E22 4700 BX R0;BX R0

08007E24 6C69

08007E26 0800

08007E28 7D8D

08007E2A 0800

细心的观众会发现地址是0x0800'7E1C,比我们查到的0x0800'7E1D差了1,这是ARM家族的遗留问题,因为ARM处理器的指令至少是半字对齐的(16位THUMB指令集 or 32位ARM指令集),所以PC指针的LSB是常为0的,为了充分利用寄存器,ARM公司给PC的LSB了一个重要的使命,那就是在执行分支跳转时,PC的LSB=1,表示使用THUMB模式,LSB=0,表示使用ARM模式,但在最新的Cortex-M3内核上,只使用了THUMB-2指令集挑大梁,所以这一位要常保持1,所以我们查到的地址是0x0800'7E1D(C=1100,D=1101),放心,我们的CM3内核会忽略掉LSB(除非为0,那么会引起一个fault),从而正确跳转到0x0800'7E1C。

从0x0800'7E20处的加载指令,我们可以算出__iar_program_start所处的位置,就是当前PC指针(0x0800'7E24),再加上4,即0x0800'7E28处的所指向的地址——0x0800'7D8D(0x0800'7D8C),我们跟紧着跳转,__iar_program_start果然在这里:

__iar_program_start:

08007D8C F000F88C BL __low_level_init

08007D90 2800 CMP R0, #0x0

08007D92 D001 BEQ __iar_init$$done

08007D94 F7FFFFDE BL __iar_data_init2

08007D98 2000 MOVS R0, #0x0

08007D9A F7FDFC49 BL main

我们看到IAR提供了__low_level_init这个函数进行了“底层”的初始化,进一步跟踪,我们可以查到__low_level_init这个函数做了些什么,不是不是我们想象中的不可告人。

__low_level_init:

08007EA8 2001 MOVS R0, #0x1

08007EAA 4770 BX LR

__low_level_init出乎想象的简单,只是往R0寄存器写入了1,就立即执行"BX LR"回到调用处了,接下来,__iar_program_start检查了R0是否为0,为0,则执行__iar_init$$done,若不是0,就执行__iar_data_init2。__iar_init$$done这个函数很简单,只有2句话,第一句是把R0清零,第二句就直接"BL main",跳转到main()函数了。不过既然__low_level_init已经往R0写入了1,那么我们还是得走下远路——看看__iar_data_init2做了些什么,虽然距离main只有一步之遥,不过这中间隐藏了编译器的思想,我们得耐心看下去。

__iar_data_init2:

08007D54 B510 PUSH {R4,LR}

08007D56 4804 LDR R0, [PC, #0x10]

08007D58 4C04 LDR R4, [PC, #0x10]

08007D5A E002 B 0x8007D62

08007D5C F8501B04 LDR R1, [R0], #0x4

08007D60 4788 BLX R1

08007D62 42A0 CMP R0, R4

08007D64 D1FA BNE 0x8007D5C

08007D66 BD10 POP {R4,PC}

08007D68 7C78

08007D6A 0800

08007D6C 7C9C

08007D6E 0800

看来IAR迟迟不执行main()函数,就是为了执行__iar_data_init2,我们来分析分析IAR都干了些什么坏事~

首先压R4,LR入栈,然后加载0x0800'7C78至R0,0x0800'7C9C至R4,马上跳转到0x0800'7D62执行R0,R4的比较,结果若是相等,则弹出R4,PC,然后立即进入main()。不过IAR请君入瓮是自不会那么快放我们出来的——结果不相等,跳转到0x0800'7D5C执行,在这里,把R0指向的地址——0x0800'7C78中的值——0x0800'7D71加载到R1,并且R0中的值自加4,更新为0x0800'7C7C,并跳转到R1指向的地址处执行,这里是另一个IAR函数:__iar_zero_init2:

__iar_zero_init2:

08007D70 2300 MOVS R3, #0x0

08007D72 E005 B 0x8007D80

08007D74 F8501B04 LDR R1, [R0], #0x4

08007D78 F8413B04 STR R3, [R1], #0x4

08007D7C 1F12 SUBS R2, R2, #0x4

08007D7E D1FB BNE 0x8007D78

08007D80 F8502B04 LDR R2, [R0], #0x4

08007D84 2A00 CMP R2, #0x0

08007D86 D1F5 BNE 0x8007D74

08007D88 4770 BX LR

08007D8A 0000 MOVS R0, R0

__iar_data_init2还没执行完毕,就跳转到了这个__iar_zero_inti2,且看我们慢慢分析这个帮凶——__iar_zero_inti2做了什么。

__iar_zero_inti2将R3寄存器清零,立即跳转到0x0800'7D80执行'LDR R2, [R0], #0x4',这句指令与刚才在__iar_data_init2见到的'LDR R1, [R0], #0x4'很类似,都为“后索引”。这回,将R0指向的地址——0x0800'7C7C中的值——0x0000'02F4加载到R2寄存器,然后R0中的值自加4,更新为0x0800'7C80。接下来的指令检查了R2是否为0,显然这个函数没那么简单想放我我们,R2的值为2F4,我们又被带到了0x0800'7D74处,随后4条指令做了如下的事情:

1、将R0指向的地址——0x0800'7C80中的值——0x2000'27D4加载到R1寄存器,然后R0中的值自加4,更新为0x0800'7C84。

2、将R1指向的地址——0x2000'27D4中的值——改写为R3寄存器的值——0,然后R1中的值自加4,更新为0x2000'27D8。

3、R2自减4

4、检查R2是否为0,不为0,跳转到第二条执行。不为,则执行下一条。

这简直就是一个循环!——C语言的循环for(r2=0x2F4;r2-=4;r!=0){...},我们看看循环中做了什么。

第一条指令把一个地址加载到了R1——0x2000'27D4 是一个RAM地址,以这个为起点,在循环中,对长度为2F4的RAM空间进行了清零的操作。那为什么IAR要做这个事情呢?消除什么记录么?用Jlink查看这片内存区域,可以发现这片区域是我们定义的全局变量的所在地。也就是说,IAR在每次系统复位后,都会自动将我们定义的全局变量清零0。

清零完毕后,接下来的指令"LDR R2, [R0], #0x4"将R0指向的地址——0x0800'7C84中的值——0加载到R2寄存器,然后R0中的值自加4,更新为0x0800'7C88。随后检查R2是否为0,这里R2为0,执行'BX LR'返回到__iar_data_init2函数,若是不为0,我们可以发现又会跳转至“4指令”处进行一个循环清零的操作。

读到这里,我们应该可以猜到IAR的意图了:__iar_data_init2一开始加载了0x0800'7C78至R0,0x0800'7C9C至R4,[R0,R4]就是一段启动代码区,在这个区域内保存了要“处理”的所有地址与信息——执行的函数地址或者参数,实际上,这片区域也有一个名字,叫做:Region$$Table$$Base。在这个区域内,程序以R0为索引,R4为上限,当R0=R4,__iar_data_init2执行完毕,跳转至main()函数。

好了,保持我们这个猜想,继续跟踪我们的PC指针——我们回到了__iar_data_init2函数中,第一件事就是比较R0,R4的值,可惜的是,仍然不相等,我们又被带到了0x0800'7D5C,至此,我们应该能看出这是一个__iar_data_init2的“主循环”,这也验证了我们对IAR意图的猜想~

__iar_data_init2中的“主循环”:

08007D5C F8501B04 LDR R1, [R0], #0x4

08007D60 4788 BLX R1

08007D62 42A0 CMP R0, R4

我们可以等价写为:for(r0=0x0800'7C78,r4=0x0800'7C9C;r0!=r4;r0+=4){...}

此时,我们的R0为0x0800'7C88,经过“指令1”,R0变为0x0800'7C8C,R1为0x0800'7C55。我们来看看,7C55处,IAR又要执行何种操作。

__iar_copy_init2:

08007C54 B418 PUSH {R3,R4}

08007C56 E009 B 0x8007C6C

08007C58 F8501B04 LDR R1, [R0], #0x4

08007C5C F8502B04 LDR R2, [R0], #0x4

08007C60 F8514B04 LDR R4, [R1], #0x4

08007C64 F8424B04 STR R4, [R2], #0x4

08007C68 1F1B SUBS R3, R3, #0x4

08007C6A D1F9 BNE 0x8007C60

08007C6C F8503B04 LDR R3, [R0], #0x4

08007C70 2B00 CMP R3, #0x0

08007C72 D1F1 BNE 0x8007C58

08007C74 BC12 POP {R1,R4}

08007C76 4770 BX LR

这是一个名为__iar_copy_init2的函数,他执行了什么"copy"操作呢?

首先压R3,R4入栈,然后跳转到0x0800'7C6C,从R0——Region$$Table$$Base中取出参数0x238放入R3,接下来的指令大家应该都熟悉了,0x238不为0,所以我们被带至7C58处,再次从Region$$Table$$Base中取出参数0x0800'7F14放入R1,从Region$$Table$$Base取出参数0x2000'2AC8放入R2处。细心的观众应该能察觉这和__iar_zero_init2中取参数的几乎一样:先取出大小,随后取出了地址——只不过这里多出了1个地址,没错这就是"copy",随后的指令

08007C60 F8514B04 LDR R4, [R1], #0x4

08007C64 F8424B04 STR R4, [R2], #0x4

08007C68 1F1B SUBS R3, R3, #0x4

08007C6A D1F9 BNE 0x8007C60

则是另一个“4指令”,指令1将R1指向地址的数据读到R4,指令2将R2指向地址的数据改写为R4的数据,指令3、4是完成一个循环。

说到这里大家都应该明白了——这就是一个"copy"的操作,从Flash地址0x0800'7F14起,将长度0x238的数据拷贝到RAM地址0x2000'2AC8中。

通过Jlink,我们可以看到这片区域是我们定义的并且已初始化的全局变量。也就是说,每次复位后,IAR在此处进行全局变量的初始化。

在这“4指令”执行完毕后,再次从Region$$Table$$Base中取出参数,为0,比较之后条件符合,函数返回__iar_data_init2。

此时的R0已经为0x0800'7C9C与R4相等,__iar_data_init2终于完成它的使命。

08007D98 2000 MOVS R0, #0x0

08007D9A F7FDFC49 BL main

将R0清零以后,IAR放弃主动权,把PC指针交给了用户程序的入口——main()。

但请注意,这里使用的是BL指令进行main跳转,也就是说,main函数只是IAR手中的一个子程序,若是main函数执行到了结尾,接下来则会执行exit等IAR提供的“退出”函数。这些函数,等待下回分解~

总之,IAR在启动main()函数以前,执行了Reset_Handler,调用SystemInit()(ST库提供)进行时钟,Flash读取初始化,并转入__iar_program_start中执行__low_level_init与__iar_data_init2,并在__iar_data_init2中,先后调用__iar_zero_init2与__iar_copy_init2对全局变量、全局已初始化变量进行相应的初始化操作。最后,调用main()函数执行。

这就是IAR在启动main()函数之前做的事情,它并没有那么神秘,只要花些时间,就可以跟跟踪分析出这个过程。

/***************************************************************************//**

* @brief

* Select reference clock/oscillator used for a clock branch.

*

* @details

* Notice that if a selected reference is not enabled prior to selecting its

* use, it will be enabled, and this function will wait for the selected

* oscillator to be stable. It will however NOT be disabled if another

* reference clock is selected later.

*

* This feature is particularly important if selecting a new reference

* clock for the clock branch clocking the core, otherwise the system

* may halt.

*

* @param[in] clock

* Clock branch to select reference clock for. One of:

* @li #cmuClock_HF

* @li #cmuClock_LFA

* @li #cmuClock_LFB @if _CMU_LFCLKSEL_LFAE_ULFRCO

* @li #cmuClock_LFC

* @endif @if _SILICON_LABS_32B_PLATFORM_2

* @li #cmuClock_LFE

* @endif

* @li #cmuClock_DBG @if DOXYDOC_USB_PRESENT

* @li #cmuClock_USBC

* @endif

*

* @param[in] ref

* Reference selected for clocking, please refer to reference manual for

* for details on which reference is available for a specific clock branch.

* @li #cmuSelect_HFRCO

* @li #cmuSelect_LFRCO

* @li #cmuSelect_HFXO

* @li #cmuSelect_LFXO

* @li #cmuSelect_HFCLKLE

* @li #cmuSelect_AUXHFRCO

* @li #cmuSelect_HFCLK @ifnot DOXYDOC_EFM32_GECKO_FAMILY

* @li #cmuSelect_ULFRCO

* @endif

******************************************************************************/

void CMU_ClockSelectSet(CMU_Clock_TypeDef clock, CMU_Select_TypeDef ref)

{

uint32_t select = cmuOsc_HFRCO;

CMU_Osc_TypeDef osc = cmuOsc_HFRCO;

uint32_t freq;

uint32_t tmp;

uint32_t selRegId;

#if defined( _SILICON_LABS_32B_PLATFORM_2 )

volatile uint32_t *selReg = NULL;

#endif

#if defined( CMU_LFCLKSEL_LFAE_ULFRCO )

uint32_t lfExtended = 0;

#endif

selRegId = (clock >> CMU_SEL_REG_POS) & CMU_SEL_REG_MASK;

switch (selRegId)

{

case CMU_HFCLKSEL_REG:

switch (ref)

{

case cmuSelect_LFXO:

#if defined( _SILICON_LABS_32B_PLATFORM_2 )

select = CMU_HFCLKSEL_HF_LFXO;

#elif defined( _SILICON_LABS_32B_PLATFORM_1 )

select = CMU_CMD_HFCLKSEL_LFXO;

#endif

osc = cmuOsc_LFXO;

break;

case cmuSelect_LFRCO:

#if defined( _SILICON_LABS_32B_PLATFORM_2 )

select = CMU_HFCLKSEL_HF_LFRCO;

#elif defined( _SILICON_LABS_32B_PLATFORM_1 )

select = CMU_CMD_HFCLKSEL_LFRCO;

#endif

osc = cmuOsc_LFRCO;

break;

case cmuSelect_HFXO:

#if defined( CMU_HFCLKSEL_HF_HFXO )

select = CMU_HFCLKSEL_HF_HFXO;

#elif defined( CMU_CMD_HFCLKSEL_HFXO )

select = CMU_CMD_HFCLKSEL_HFXO;

#endif

osc = cmuOsc_HFXO;

#if defined( CMU_MAX_FREQ_HFLE )

/* Set 1 HFLE wait-state until the new HFCLKLE frequency is known.

This is known after 'select' is written below. */

setHfLeConfig(CMU_MAX_FREQ_HFLE + 1, CMU_MAX_FREQ_HFLE);

#endif

#if defined( CMU_CTRL_HFXOBUFCUR_BOOSTABOVE32MHZ )

/* Adjust HFXO buffer current for frequencies above 32MHz */

if (SystemHFXOClockGet() > 32000000)

{

CMU->CTRL = (CMU->CTRL & ~_CMU_CTRL_HFXOBUFCUR_MASK)

| CMU_CTRL_HFXOBUFCUR_BOOSTABOVE32MHZ;

}

else

{

CMU->CTRL = (CMU->CTRL & ~_CMU_CTRL_HFXOBUFCUR_MASK)

| CMU_CTRL_HFXOBUFCUR_BOOSTUPTO32MHZ;

}

#endif

break;

case cmuSelect_HFRCO:

#if defined( _SILICON_LABS_32B_PLATFORM_2 )

select = CMU_HFCLKSEL_HF_HFRCO;

#elif defined( _SILICON_LABS_32B_PLATFORM_1 )

select = CMU_CMD_HFCLKSEL_HFRCO;

#endif

osc = cmuOsc_HFRCO;

#if defined( CMU_MAX_FREQ_HFLE )

/* Set 1 HFLE wait-state until the new HFCLKLE frequency is known.

This is known after 'select' is written below. */

setHfLeConfig(CMU_MAX_FREQ_HFLE + 1, CMU_MAX_FREQ_HFLE);

#endif

break;

#if defined( CMU_CMD_HFCLKSEL_USHFRCODIV2 )

case cmuSelect_USHFRCODIV2:

select = CMU_CMD_HFCLKSEL_USHFRCODIV2;

osc = cmuOsc_USHFRCO;

break;

#endif

#if defined( CMU_LFCLKSEL_LFAE_ULFRCO ) || defined( CMU_LFACLKSEL_LFA_ULFRCO )

case cmuSelect_ULFRCO:

/* ULFRCO cannot be used as HFCLK */

EFM_ASSERT(0);

return;

#endif

default:

EFM_ASSERT(0);

return;

}

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(osc, true, true);

/* Configure worst case wait states for flash access before selecting */

flashWaitStateMax();

/* Switch to selected oscillator */

#if defined( _CMU_HFCLKSEL_MASK )

CMU->HFCLKSEL = select;

#else

CMU->CMD = select;

#endif

#if defined( CMU_MAX_FREQ_HFLE )

/* Update HFLE configuration after 'select' is set.

Note that the HFCLKLE clock is connected differently on planform 1 and 2 */

setHfLeConfig(CMU_ClockFreqGet(cmuClock_HFLE), CMU_MAX_FREQ_HFLE);

#endif

/* Keep EMU module informed */

EMU_UpdateOscConfig();

/* Update CMSIS core clock variable */

/* (The function will update the global variable) */

freq = SystemCoreClockGet();

/* Optimize flash access wait state setting for currently selected core clk */

flashWaitStateControl(freq);

break;

#if defined( _SILICON_LABS_32B_PLATFORM_2 )

case CMU_LFACLKSEL_REG:

selReg = (selReg == NULL) ? &CMU->LFACLKSEL : selReg;

#if !defined( _CMU_LFACLKSEL_LFA_HFCLKLE )

/* HFCLKCLE can not be used as LFACLK */

EFM_ASSERT(ref != cmuSelect_HFCLKLE);

#endif

/* Fall through and select clock source */

case CMU_LFECLKSEL_REG:

selReg = (selReg == NULL) ? &CMU->LFECLKSEL : selReg;

#if !defined( _CMU_LFECLKSEL_LFE_HFCLKLE )

/* HFCLKCLE can not be used as LFECLK */

EFM_ASSERT(ref != cmuSelect_HFCLKLE);

#endif

/* Fall through and select clock source */

case CMU_LFBCLKSEL_REG:

selReg = (selReg == NULL) ? &CMU->LFBCLKSEL : selReg;

switch (ref)

{

case cmuSelect_Disabled:

tmp = _CMU_LFACLKSEL_LFA_DISABLED;

break;

case cmuSelect_LFXO:

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(cmuOsc_LFXO, true, true);

tmp = _CMU_LFACLKSEL_LFA_LFXO;

break;

case cmuSelect_LFRCO:

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(cmuOsc_LFRCO, true, true);

tmp = _CMU_LFACLKSEL_LFA_LFRCO;

break;

case cmuSelect_HFCLKLE:

/* Ensure correct HFLE wait-states and enable HFCLK to LE */

setHfLeConfig(SystemCoreClockGet(), CMU_MAX_FREQ_HFLE);

BUS_RegBitWrite(&CMU->HFBUSCLKEN0, _CMU_HFBUSCLKEN0_LE_SHIFT, 1);

tmp = _CMU_LFBCLKSEL_LFB_HFCLKLE;

break;

case cmuSelect_ULFRCO:

/* ULFRCO is always on, there is no need to enable it. */

tmp = _CMU_LFACLKSEL_LFA_ULFRCO;

break;

default:

EFM_ASSERT(0);

return;

}

*selReg = tmp;

break;

#elif defined( _SILICON_LABS_32B_PLATFORM_1 )

case CMU_LFACLKSEL_REG:

case CMU_LFBCLKSEL_REG:

switch (ref)

{

case cmuSelect_Disabled:

tmp = _CMU_LFCLKSEL_LFA_DISABLED;

break;

case cmuSelect_LFXO:

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(cmuOsc_LFXO, true, true);

tmp = _CMU_LFCLKSEL_LFA_LFXO;

break;

case cmuSelect_LFRCO:

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(cmuOsc_LFRCO, true, true);

tmp = _CMU_LFCLKSEL_LFA_LFRCO;

break;

case cmuSelect_HFCLKLE:

#if defined( CMU_MAX_FREQ_HFLE )

/* Set HFLE wait-state and divider */

freq = SystemCoreClockGet();

setHfLeConfig(freq, CMU_MAX_FREQ_HFLE);

#endif

/* Ensure HFCORE to LE clocking is enabled */

BUS_RegBitWrite(&CMU->HFCORECLKEN0, _CMU_HFCORECLKEN0_LE_SHIFT, 1);

tmp = _CMU_LFCLKSEL_LFA_HFCORECLKLEDIV2;

break;

#if defined( CMU_LFCLKSEL_LFAE_ULFRCO )

case cmuSelect_ULFRCO:

/* ULFRCO is always enabled */

tmp = _CMU_LFCLKSEL_LFA_DISABLED;

lfExtended = 1;

break;

#endif

default:

/* Illegal clock source for LFA/LFB selected */

EFM_ASSERT(0);

return;

}

/* Apply select */

if (selRegId == CMU_LFACLKSEL_REG)

{

#if defined( _CMU_LFCLKSEL_LFAE_MASK )

CMU->LFCLKSEL = (CMU->LFCLKSEL

& ~(_CMU_LFCLKSEL_LFA_MASK | _CMU_LFCLKSEL_LFAE_MASK))

| (tmp << _CMU_LFCLKSEL_LFA_SHIFT)

| (lfExtended << _CMU_LFCLKSEL_LFAE_SHIFT);

#else

CMU->LFCLKSEL = (CMU->LFCLKSEL & ~_CMU_LFCLKSEL_LFA_MASK)

| (tmp << _CMU_LFCLKSEL_LFA_SHIFT);

#endif

}

else

{

#if defined( _CMU_LFCLKSEL_LFBE_MASK )

CMU->LFCLKSEL = (CMU->LFCLKSEL

& ~(_CMU_LFCLKSEL_LFB_MASK | _CMU_LFCLKSEL_LFBE_MASK))

| (tmp << _CMU_LFCLKSEL_LFB_SHIFT)

| (lfExtended << _CMU_LFCLKSEL_LFBE_SHIFT);

#else

CMU->LFCLKSEL = (CMU->LFCLKSEL & ~_CMU_LFCLKSEL_LFB_MASK)

| (tmp << _CMU_LFCLKSEL_LFB_SHIFT);

#endif

}

break;

#if defined( _CMU_LFCLKSEL_LFC_MASK )

case CMU_LFCCLKSEL_REG:

switch(ref)

{

case cmuSelect_Disabled:

tmp = _CMU_LFCLKSEL_LFA_DISABLED;

break;

case cmuSelect_LFXO:

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(cmuOsc_LFXO, true, true);

tmp = _CMU_LFCLKSEL_LFC_LFXO;

break;

case cmuSelect_LFRCO:

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(cmuOsc_LFRCO, true, true);

tmp = _CMU_LFCLKSEL_LFC_LFRCO;

break;

default:

/* Illegal clock source for LFC selected */

EFM_ASSERT(0);

return;

}

/* Apply select */

CMU->LFCLKSEL = (CMU->LFCLKSEL & ~_CMU_LFCLKSEL_LFC_MASK)

| (tmp << _CMU_LFCLKSEL_LFC_SHIFT);

break;

#endif

#endif

#if defined( CMU_DBGCLKSEL_DBG ) || defined( CMU_CTRL_DBGCLK )

case CMU_DBGCLKSEL_REG:

switch(ref)

{

#if defined( CMU_DBGCLKSEL_DBG )

case cmuSelect_AUXHFRCO:

/* Select AUXHFRCO as debug clock */

CMU->DBGCLKSEL = CMU_DBGCLKSEL_DBG_AUXHFRCO;

break;

case cmuSelect_HFCLK:

/* Select divided HFCLK as debug clock */

CMU->DBGCLKSEL = CMU_DBGCLKSEL_DBG_HFCLK;

break;

#endif

#if defined( CMU_CTRL_DBGCLK )

case cmuSelect_AUXHFRCO:

/* Select AUXHFRCO as debug clock */

CMU->CTRL = (CMU->CTRL & ~(_CMU_CTRL_DBGCLK_MASK))

| CMU_CTRL_DBGCLK_AUXHFRCO;

break;

case cmuSelect_HFCLK:

/* Select divided HFCLK as debug clock */

CMU->CTRL = (CMU->CTRL & ~(_CMU_CTRL_DBGCLK_MASK))

| CMU_CTRL_DBGCLK_HFCLK;

break;

#endif

default:

/* Illegal clock source for debug selected */

EFM_ASSERT(0);

return;

}

break;

#endif

#if defined( USB_PRESENT )

case CMU_USBCCLKSEL_REG:

switch(ref)

{

case cmuSelect_LFXO:

/* Select LFXO as clock source for USB, can only be used in sleep mode */

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(cmuOsc_LFXO, true, true);

/* Switch oscillator */

CMU->CMD = CMU_CMD_USBCCLKSEL_LFXO;

/* Wait until clock is activated */

while((CMU->STATUS & CMU_STATUS_USBCLFXOSEL)==0)

{

}

break;

case cmuSelect_LFRCO:

/* Select LFRCO as clock source for USB, can only be used in sleep mode */

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(cmuOsc_LFRCO, true, true);

/* Switch oscillator */

CMU->CMD = CMU_CMD_USBCCLKSEL_LFRCO;

/* Wait until clock is activated */

while((CMU->STATUS & CMU_STATUS_USBCLFRCOSEL)==0)

{

}

break;

#if defined( CMU_STATUS_USBCHFCLKSEL )

case cmuSelect_HFCLK:

/* Select undivided HFCLK as clock source for USB */

/* Oscillator must already be enabled to avoid a core lockup */

CMU->CMD = CMU_CMD_USBCCLKSEL_HFCLKNODIV;

/* Wait until clock is activated */

while((CMU->STATUS & CMU_STATUS_USBCHFCLKSEL)==0)

{

}

break;

#endif

#if defined( CMU_CMD_USBCCLKSEL_USHFRCO )

case cmuSelect_USHFRCO:

/* Select USHFRCO as clock source for USB */

/* Ensure selected oscillator is enabled, waiting for it to stabilize */

CMU_OscillatorEnable(cmuOsc_USHFRCO, true, true);

/* Switch oscillator */

CMU->CMD = CMU_CMD_USBCCLKSEL_USHFRCO;

/* Wait until clock is activated */

while((CMU->STATUS & CMU_STATUS_USBCUSHFRCOSEL)==0)

{

}

break;

#endif

default:

/* Illegal clock source for USB */

EFM_ASSERT(0);

return;

}

break;

#endif

default:

EFM_ASSERT(0);

break;

}

#if defined( CMU_MAX_FREQ_HFLE )

/* Get to assert wait-state config. */

getHfLeConfig();

#endif

}