将普通I/0口作为时钟信号可能出现如下问题,综合可以通过,只是在实现的时候,ISE会报错。如下:

出现这种情况事实上,是由于将普通端口作为时钟端口而在.ucf文件中没有将他们绑定到全局时钟上,这时钟信号无法最优路径也就导致了整个设计的时序性较差。看下面的例子:

//产生抢答器的控制信号 always @(emcee or actor1 or actor2 or actor3 or actor4) begin if (emcee == 1'b0)begin enable = 1'b1; cnt = 1'b1; end else begin enable = cnt && actor1 && actor2 && actor3 && actor4; cnt = 0; end end

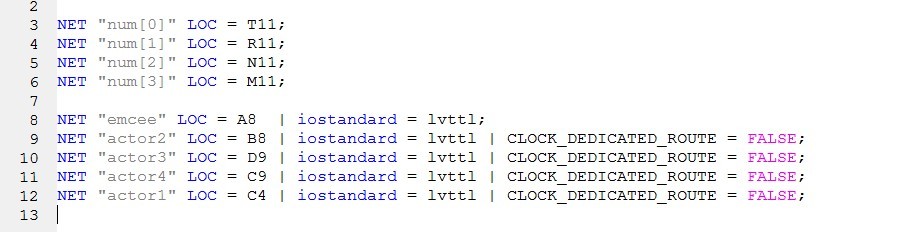

这是四变量抢答器VerilogHDL的部分代码(产生控制信号),在.v文件中把actor1~4都作为了时钟端口,虽然该设计可以被综合且能被正确的仿真,但是在map时会出现上文报错的情况。此时若修改.ucf 文件加上CLOCK_DEDICATED_ROUTE = FALSE;如下:

此时,会将错误变成警告,编译会通过,当然,这个办法是治标不治本,针对于对时序要求不高的设计而言的,若对时序严格要求,那么这样写就会有问题了。