学号 《信息安全系统设计基础》第7周学习总结(一)

学号 《信息安全系统设计基础》第7周学习总结(一)

教材学习内容总结

基本存储技术:SRAM存储器 DRAM存储器 ROM存储器 旋转硬盘 固态硬盘

随机访问存储器:

1 静态(SRAM):双稳定特性、只要通电就能永远稳定,速度较快

2 动态(DRAM):对干扰敏感,一旦电压被干扰,永远不能恢复,并且暴露在光线下会导致电容电压改变,速度较慢。

DRAM中=芯片单元分成M个超单元,每个超单元有N个DRAM单元组成,并有r行 c列。

读取过程:从16*8的DRAM中读取超单元(4,3),首先存储控制器发送行地址4,然后DRAM将4行的所有内容拷贝到内部行缓冲区,接着控制器再发送列地址3,DRAM将行缓冲区拷贝出超单元(4,3)中的8位并发送到存储控制器。

快业模式的DRAM: 存储控制器发送行地址的时候后面跟着三个列地址(1+3),相比原本的DRAM拷贝一次行就浪费一次要快得多。

VRAM: 输出时通过对行内部缓冲区的整个内容行位移得到,更快,并且允许对存储器并行的读和写。

非易失性存储器:

ROM(只读存储器):

1 PROM(只能被编程一次,只能高电流熔断一次)

2 可擦写可编程ROM(光擦除的可擦写和冲编程的次数达1000次,电子可擦除的可达到10^5次)

3 闪存

固件:存储在ROM设备中的程序。

movl A,%eax的过程:

1 CPU将地址放到系统总线上

2 I/O桥将信号信号传递到存储器

3 存储器从系统总线上读取地址A

4 并读取除数据写到存储器总线上

5 I/O桥将存储器总线上的信号翻译成系统总线号,并传递到CUP。

6 CPU从总线上读数据并拷贝到寄存器%eax

movl %eax,A的过程:

1 CPU将地址A放到系统总线上(I/O桥信号翻译过程也在其中)

2 存储器从总线上读出地址A,等待数据送达

3 CPU将%eax中的数据字拷贝到系统总线上(和2同时)

4 主存从存储器总线独处数据字并存到DRAM的A地址中。

磁盘构造:

盘片(有两面,盘片中央有可旋转的主轴,旋转速度RPM)

每个表面有8个磁道,没个刺刀被划分为一组扇区,扇区间的空隙存储用来标识扇区的格式化位。

磁盘容量=字节数/扇区+平均扇区数/磁道+磁道数/表面+表面数/盘片+盘片数/磁盘

磁盘上一个扇区读取时间=寻道时间+传送时间+平均旋转时间(总传送时间的一半)

局部性:

1 时间局部性(被引用过一次的存储器位置不久后也有可能在被多次引用)

2 空间局部性(被引用过一次的存储器位置不久后将引用附近的位置)

具有步长为K的引用模式的程序,K越小空间局部性越好。

重复引用同一个变量的程序有良好的时间局部性。

教材学习中的问题和解决过程

P385中谈到若DRAM被组织成一个线性数组,则需要4个地址引脚,一开始没反应过来,后来问了同学才知道自己没注意一个地址引脚带两位(0、1),则16位的话要4个地址引脚。

弄懂之后就会做习题6.1了

P403页

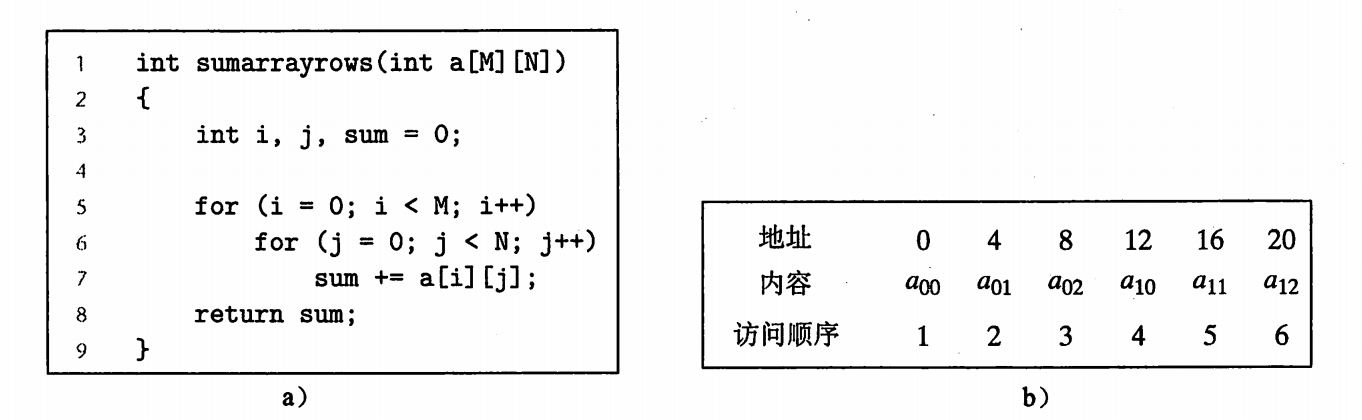

如图,一开始弄不懂为什么这是一个步长为1的引用模式,后来问了周岐浩同学知道该程序行优先顺序访问,如a00到a01、a01到a02都隔了一个元素,以此类推,所以是步长为1.

下图按照列优先顺序被访问,那么就不止隔着一个元素了,如a00到a10隔着3个元素,a10到a01隔着2个元素,所以局部性很差。

由此可得课后作业习题6.8中可把程序循环部分改成:

for(k = 0;k < N;k++)

for(i = 0;i < N;i++)

for(j = 0;j < N;j++)

或者 sum+=a[i][j][k]

其他(感悟、思考等,可选)

还是那句话,课本很重要,习题不能不做。