寄存器,移位寄存器的电路原理以及verilog代码实现

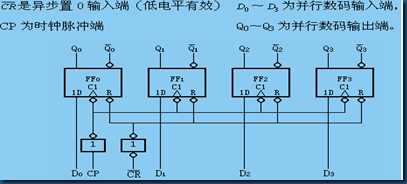

寄存器:用以存放二进制代码的电路,下图为由维特阻塞D触发器组成的4位数码寄存器:

逻辑功能分析:

1.异步端CR置0时,输出置0;

2.同步并行置数:D0~D3为4个输入代码,当CP上升沿到达时,D0~D3被同时并行置入。

3.在置数端为1,CP端为0时,保持不变。

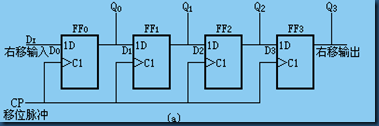

2.移位寄存器:具有存放数码和使数码逐位右移或左移的电路称为移位寄存器。

移位寄存器按照不同的分类方法可以分为不同的类型。 如果按照移位寄存器的移位方向来进行分类, 可以分为左移移位寄存器、移位寄存器和双向移位寄存器等;如果按照工作方式来分类,可以分为串入/串出移位寄存器、串入/并出移位寄存器和并入/串出移位寄存器等。

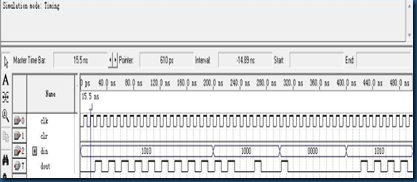

以下为异步清零的4位并入串出移位寄存器(输入为并行数据,输出为串行数据)

module reg_bc(clk,clr,din,dout); input clk,clr; // 输入时钟端,清零端(高电平有效) input[3:0] din; // 数据输入端 output dout; // 数据输出端 reg[1:0] cnt; reg[3:0] q; reg dout; always@(posedge clk) // 时钟上升沿触发 begin cnt<=cnt+1; //cnt 自加 1 if(clr) // 判断清零信号是否有效 begin q<=4'b0000; //q 置 置 0 end else begin if(cnt>0) // 判断 cnt 是否大于 0 begin q[3:1]<=q[2:0]; //q 中的值向左移 1 位 end else if(cnt==2'b00) // 判断 cnt 是否为 0 begin q<=din; //把 把 din 的值赋予 q end dout<=q[3]; //把 把 q 的最高位输出 end end

posted on 2015-08-07 19:00 Sasha.Xu 阅读(16547) 评论(0) 编辑 收藏 举报