基于FPGA简单相位检测模块设计

基于FPGA简单相位检测模块设计

1.相位检测的原理

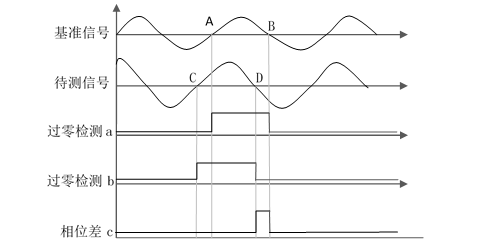

信号的相位参数用于描述信号的变化趋势,故相位检测不是单一的信号检测,一般来说是两个同频信号之间的参数差值的检测,如图1-1,相位检测使用较为广泛的为过零检测的方式,即通过对信号的整形测试,将输入信号转化为对应的过零高低电平,通过比较参考信号高低电平与待测信号高低电平之间的关系就可以得到对应的相位参数,

图 1-1 相位检测原理

设基准信号为ϕ_1 (t)(式 1-1),待测信号为ϕ_2 (t) (式 1-2),基准信号的过零检测电平为a;待测信号的过零检测信号为b,相位差值信号为c。

ϕ_1 (t)=sin((ω_c t+φ_1)) 式 1-1

ϕ_2 (t)=sin((ω_c t+φ_2)) 式 1-2

基准信号在A点发生跳变,由零下转为零上,此时触发过零检测信号a由低电平转化为高电平;待测信号在C点发生跳变时,将过零检测信号b由低电平转化为高电平,信号a,b分别为对应信号的上半周期,通过比较之间初始位置的差距就可以测量出对应信号之间的参数差值(式 1-3)。

φ=(φ_1-φ)_2 式 1-3

测量模块的时钟为标准时钟,设计计数器对相差信号进行计数,可以得到信号的高脉冲时间,依据标准信号的波形周期就可以计算出待测信号与标准信号的相位差参数。

2. 连续相位检测的FPGA实现

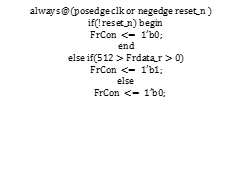

连续相位检测的实现主要依据相位检测的原理,为保证输入信号的稳定性,先对输入信号进行缓存,对缓存的信号进行半波整形,去除掉负半周期的波形,对采集的信号进行过零检测,过零的信号部分转化为Frcon对应的高电平,对于待测信号也类似,将待测信号进行半波整形,把高电平部分转化为Fvcon对应的高电平。

图 1-2 过零电平的产生

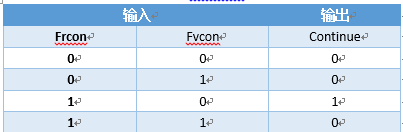

过零检测电平信号Frcon,Fvcon可组成4个类型的电平信号,电平状态分别为“00”、“01” 、“10” 、“11”, 其中转态“00” 、“10”都满足检测检测的逻辑电平,但考虑到设计的稳定性,这里选择“10”作为判决的逻辑电平,同时也将该转态作为相位计数器的控制电平,真值表关系如下(表 1-1):

表 1-1 过零转态真值表

电平检测时对Frcon、Fvcon信号进行拼接,组成一个2Bits的判决信号,当组合信号状态变为“10”时,触发Continue判决输出电平,启动计数器,对相差电平进行计数,计算与标准信号的相位参差。

图 1-3 过零信号的电平判决

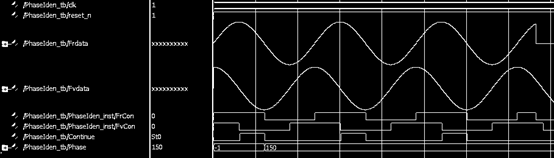

3. 连续相位检测模块的ModelSim仿真

完成了以上工作,对模连续相位检测块进行编译,如果没有语法错误就可以开始逻辑的设计验证,编写测设脚本tesebench文件,设置仿真参数:标准信号的相位设计为:0π,待测信号使用MATLAB生产测试文件,设计初始相位为2/π,仿真时钟为5个单位时间,数据的速率为1Mhz;全编译工程文件,调用Modelsim仿真工具进行逻辑的验证,目标器件为Intel公司Cyclone IV E家族的EP4CE15F23C8,占用逻辑资源:26 / 15,408 ( < 1 % ),储存空间占用0 / 516,096 ( 0 % ),9*9嵌入式乘法器占用0 / 112 ( 0 % ),数字锁相环占用 0 / 4 ( 0 % )。运行仿真,结果如图所示(图 1-4),符合设计逻辑。

图 1-4 连续相位检测模块的ModelSim波形仿真

如有技术错误请指正,转载请注明出处。