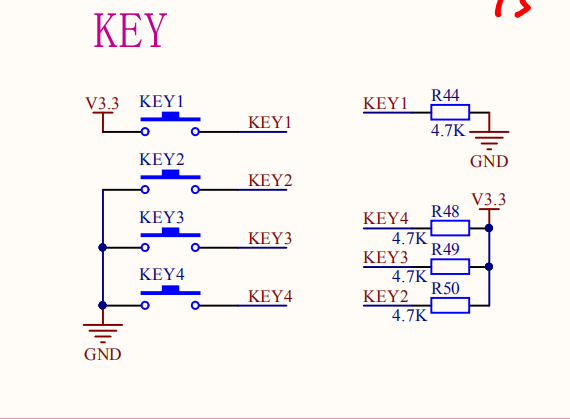

说真的,后知后觉这个问题还是有点值得研究的,一开始学习我用的板子在按键模块电路中GPIO输入脚是有外部上下拉电阻的,如下图所示:当KEY1接V3.3,在其后为它接一个下拉电阻,可以保证按下按键输入高电平有效,相反KEY2、3、4则为输入低电平有效

所以自然不需要考虑什么IO口的上下拉问题,最最坑的一点是自己将上下拉简单理解为了是否接有上下拉电阻,并没有深层次去考究钻研这个问题,从而也就导致了自己在碰到别人程序时产生了疑惑,它的原理图中都没有上下拉电阻,为什么软件配置的时候要设置为下拉啊,于是我就开始对照两者的不同,这时疑惑也就更多了。现在我将自己整理别人和自己理解所得分享出来,希望有和我有着相同疑惑的人能清晰认识关于GPIO口的上下拉配置问题,由此引申到之后更多的电路设计或者软件编写,也能有所启示。

其实,上拉电阻的目的是为了保证在无信号输入时输入端的电平为高电平。而在信号输入为低电平是输入端的电平应该也为低电平。如果没有上拉电阻,在没有外界输入的情况下输入端是悬空的,它的电平是未知的无法保证的,上拉电阻就是为了保证无信号输入时输入端的电平为高电平,同样还有下拉电阻它是为了保证无信号输入时输入端的电平为低电平。不知道自己有没有讲清楚,现在附上自己搜索的参考链接吧。

1.https://blog.csdn.net/xuw_xy/article/details/95514042

2.http://bbs.eeworld.com.cn/thread-1070283-1-1.html

想简单理解的朋友,只需要知道我最后写的意思是什么就可以了,想深究一下的话可以看一下链接内容,自己也可以搜索相关知识!