第六章存储器层次结构

参考资料http://www.cnblogs.com/hyq20135317/ 韩玉琪的博客

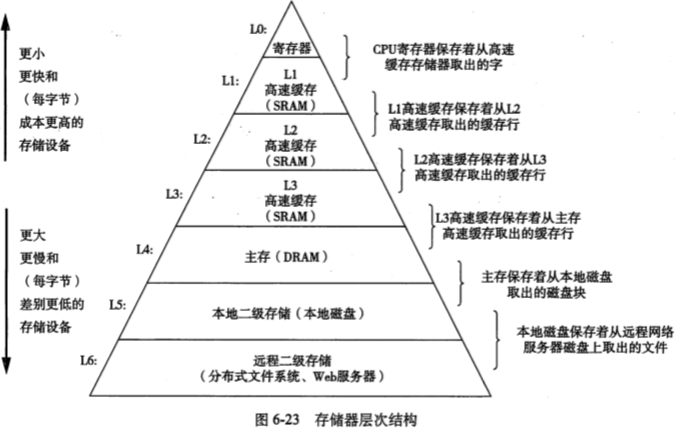

存储器系统是一个线性的字节数组。是一个具有不同容量、成本和访问时间的存储设备的层次结构。

分类:1.靠近CPU的高速缓存存储器; 2.相对慢速的主存储器

存储器层次结构:指令制定期间——0周期;

高速缓存中——1-30个周期;

主存中——50-200个周期;

磁盘上——几千万个周期。

基本属性——局部性:多次访问相同数据项集合。

存储技术:1.SRAM存储器

2.DRAM存储器

3.ROM存储器

4.旋转的个固态的硬盘

6.1 存储技术

- 随机访问存储器(RAM)

分类:静态(SRAM)——双稳态的(摆钟的左右两边状态)

动态(DRAM)——对干扰敏感

传统DRAM——分成d个超单元

存储器模块:1.双列(DIMM) 2.单列(SIMM)

增强的DRAM:快页模式

扩展数据输出

双倍数据速率通过不

非易失性存储器

访问主存——总线事务、读事务、写事务

- 磁盘存储

盘片:表面*2+磁道+扇区(512bety)+间隙+主轴

旋转速率(5400-15000r/min)

容量=字节数*平均扇区数*磁道数*表面数*盘片数

扇区的访问时间=寻道时间+旋转时间+传送时间

- 逻辑磁盘块三元组:盘面、磁道、扇区——唯一表示物理扇区

- 固态硬盘

6.2 局部性

- 对程序数据的引用:步长为k的引用模式、行优先顺序

- 取指令

6.3 存储器层次结构

- 缓存:高速缓存——高速缓存cash是一个小而快速的存储设备,它作为存储在更大、更慢的设备中的数据对象的缓冲区域。使用高速缓存的过程称为缓存。

- 缓存命中:当前存储在第k层的一个块中查找,刚好缓存在第k层中

缓存不命中种类:1).强制性不命中(冷缓存)——放置策略

2).冲突不命中

- 缓存管理

6.4 高速缓存存储器

L1高速缓存:位于CPU寄存器文件和主存之间,访问速度2-4个时钟周期

L2高速缓存:位于L1高速缓存和主存之间,访问速度10个时钟周期

L3高速缓存:位于L2高速缓存和主存之间,访问速度30或40个时钟周期

1. 通用的高速缓存存储器结构

m:每个存储器地址有m位,形成M=2^m个不同的地址

S:这个数组中有S=2^s个高速缓存组

E:每个组包含E个高速缓存行

B:每个行是由一个B=2^b字节的数据块组成的

参考资料:http://www.cnblogs.com/hyq20135317/p/4905723.html